ążąŠčĆčāą╝ ąĀą░ą┤ąĖąŠąÜąŠčé • ą¤čĆąŠčüą╝ąŠčéčĆ č鹥ą╝čŗ - CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąĪąŠąŠą▒čēąĄąĮąĖčÅ ą▒ąĄąĘ ąŠčéą▓ąĄč鹊ą▓ | ąÉą║čéąĖą▓ąĮčŗąĄ č鹥ą╝čŗ

ąĪčéčĆą░ąĮąĖčåą░ 1 ąĖąĘ 1

[ ąĪąŠąŠą▒čēąĄąĮąĖą╣: 20 ]

ąÉą▓č鹊čĆ

ąĪąŠąŠą▒čēąĄąĮąĖąĄ

greeka

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪą▒ ą╝ą░čĆ 18, 2017 15:55:41

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé čÅąĮą▓ 12, 2017 14:13:48ąĪąŠąŠą▒čēąĄąĮąĖą╣: 24

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąÆčüąĄą╝ ą┐čĆąĖą▓ąĄčé,

ąĮąĄ ą╝ąŠą│čā ą┐ąŠąĮčÅčéčī ą▓ č湥ą╝ ą┤ąĄą╗ąŠ, ąĮą░čüčéčĆą░ąĖą▓ą░čÄ čĆąĄą│ąĖčüčéčĆ MCSM1.RXOFF_MODE = 11 (3) čćč鹊ą▒ ąŠąĮ ąŠčüčéą░ą▓ą░ą╗čüčÅ ą▓ RX ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░, ąĮąŠ ąŠąĮ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE.

ą¦č鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĖčćąĖąĮąŠą╣ čéą░ą║ąŠą│ąŠ?

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

GRAF

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčü ą╝ą░čĆ 19, 2017 23:02:12

ą£čāą┤čĆčŗą╣ ą║ąŠčé

ąÜą░čĆą╝ą░: 2

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 5

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪčĆ čÅąĮą▓ 23, 2008 22:11:54ąĪąŠąŠą▒čēąĄąĮąĖą╣: 1867ą×čéą║čāą┤ą░: ąÜą░ą╗ąĖąĮąĖąĮą│čĆą░ą┤

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąöą░ą▓ą░ą╣č鹥 ą┤ą╗čÅ ąĮą░čćą░ą╗ą░ ą▓ąĘą│ą╗čÅąĮąĄą╝ ąĮą░ ą┐ąŠą╗ąĮčāčÄ ą┐čĆąŠčåąĄą┤čāčĆčā ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ čĆąĄą│ąĖčüčéčĆąŠą▓. ą¤ąŠą║ą░ąČąĖč鹥 čüą▓ąŠąĖ ąĮą░čüčéčĆąŠą╣ą║ąĖ.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

int4880053

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤ąĮ ą╝ą░čĆ 20, 2017 11:37:50

ąōąŠą▓ąŠčĆčÅčēąĖą╣ čü č鹥ą║čüč鹊ą╗ąĖč鹊ą╝

ąÜą░čĆą╝ą░: 17

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 185

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé ą┤ąĄą║ 12, 2008 21:12:14ąĪąŠąŠą▒čēąĄąĮąĖą╣: 1604ą×čéą║čāą┤ą░: Moscow

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąØą░ č乊čĆčāą╝ąĄ

www.kazus.ru čéą░ą╝ ą┐ąŠą╗ąĮąŠ ą┐čĆąŠ ąĮąĄą│ąŠ ąĮą░ą┐ąĖčüą░ąĮąŠ.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

greeka

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčé ą╝ą░čĆ 21, 2017 19:40:31

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé čÅąĮą▓ 12, 2017 14:13:48ąĪąŠąŠą▒čēąĄąĮąĖą╣: 24

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąöą░ čÅ ą┐ąĄčĆąĄčćąĖčéą░ą╗ ą╝ąĮąŠą│ąŠ ąĖąĮčäčŗ, ąĮąŠ ą▓čüąĄ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╝ čüčģąŠą┤ąĖčéčüčÅ ą║ č鹊ą╝čā, čćč鹊 ąĄčüą╗ąĖ ąĮą░čüčéčĆąŠą╣ą║ą░ ąĄčüčéčī - ąĘąĮą░čćąĖčé ą┤ąŠą╗ąČąĮąŠ čĆą░ą▒ąŠčéą░čéčī.

GRAF ąÜąŠą┤:

ąĪą▒čĆąŠčü:

ąÜąŠą┤:

void CC1101_Reset(void) {

ąØą░čüčéčĆąŠą╣ą║ą░:

ąÜąŠą┤:

void CC1101_Configure(void)

ąĪą│ąĄąĮąĄčĆąĄąĮąĮą░čÅ čüčéčāą┤ąĖąĄą╣.

ą¤ąŠčüą╗ąĄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą┐ąĄčĆąĖč乥čĆąĖąĖ ą▓ ą£ąÜ ąĖą┤ąĄčé čéą░ą║ąŠą╣ ą▓čŗąĘąŠą▓:

ąÜąŠą┤:

CC1101_Reset();

ąöą░ą╗ąĄąĄ ą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĖ ą┐ąŠ ą┐ą░ą┤ą░čÄčēąĄą╝čā čäčĆąŠąĮčéčā ąĮąŠą│ąĖ GDO0 ąĮą░čüčéčĆąŠąĄąĮąĮąŠą╣ ąĮą░ ą┐ąŠą╗čāč湥ąĮąĖąĄ ą┐ą░ą║ąĄčéą░ ą┐ąŠą┐ą░ą┤ą░ąĄą╝ ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║:

ąÜąŠą┤:

void uEXTI_IRQHandler(uint32_t Pin)

ąś ą▓ ąŠčüąĮąŠą▓ąĮąŠą╝ čåąĖą║ą╗ąĄ ą║ą░ą║ č鹊ą╗čīą║ąŠ ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ ą▓čŗčüčéą░ą▓ąĖą╗ąĖ čäą╗ą░ą│:

ąÜąŠą┤:

while (1)

ąĪą░ą╝ CC1101_HandleStatus:

ąÜąŠą┤:

void CC1101_HandleStatus(void) {

ąĄčüą╗ąĖ ą▓čŗąĘąŠą▓ CC1101_RxMode(); ą║ą░ą║ čüąĄą╣čćą░čü ąĘą░ą║ąŠą╝ąĄąĮč湥ąĮ, č鹊 ą▒ąŠą╗čīčłąĄ ą┐čĆąĖąĄą╝ą░ ąĮąĄčé.

ąÜąŠą┤:

void CC1101_RxMode(void) {

ą¤ą░čĆą░ą╝ąĄčéčĆčŗ čüčéčāą┤ąĖąĖ:

ąÆą╗ąŠąČąĄąĮąĖąĄ:

2017-03-21_1949.png [16.95 KiB]

ąĪą║ą░čćąĖą▓ą░ąĮąĖą╣: 642

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆą░ąĘ čĆąĄą┤ą░ą║čéąĖčĆąŠą▓ą░ą╗ąŠčüčī greeka ąÆčé ą╝ą░čĆ 21, 2017 22:13:08, ą▓čüąĄą│ąŠ čĆąĄą┤ą░ą║čéąĖčĆąŠą▓ą░ą╗ąŠčüčī 1 čĆą░ąĘ.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

ąÆčŗą▒ąĖčĆą░ąĄą╝ čüčģąĄą╝čā BMS ą┤ą╗čÅ ąĘą░čĆčÅą┤ą░ ą╗ąĖčéąĖą╣-ąČąĄą╗ąĄąĘąŠč乊čüčäą░čéąĮčŗčģ (LiFePO4) ą░ą║ą║čāą╝čāą╗čÅč鹊čĆąŠą▓

ą×ą▒čÅąĘą░č鹥ą╗čīąĮčŗą╝ čāčüą╗ąŠą▓ąĖąĄą╝ ą┤ąŠą╗ą│ąŠą╣ ąĖ čüčéą░ą▒ąĖą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ Li-FePO4-ą░ą║ą║čāą╝čāą╗čÅč鹊čĆąŠą▓, ą▓ č鹊ą╝ čćąĖčüą╗ąĄ ąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░ EVE Energy, čÅą▓ą╗čÅąĄčéčüčÅ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄ čüą┐ąĄčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗčģ BMS-ą╝ąĖą║čĆąŠčüčģąĄą╝. ąøąĖčéąĖą╣-ąČąĄą╗ąĄąĘąŠč乊čüčäą░čéąĮčŗąĄ ąÉąÜąæ ąŠčéą╗ąĖčćą░čÄčéčüčÅ čéą░ą║ąĖą╝ąĖ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ą╝ąĖ, ą║ą░ą║ ą▓čŗčüąŠą║ą░čÅ ą╝ąĮąŠą│ąŠą║čĆą░čéąĮąŠčüčéčī čåąĖą║ą╗ąŠą▓ ąĘą░čĆčÅą┤ą░-čĆą░ąĘčĆčÅą┤ą░, ą▒ąĄąĘąŠą┐ą░čüąĮąŠčüčéčī, ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą▒čŗčüčéčĆąŠą╣ ąĘą░čĆčÅą┤ą║ąĖ, čāčüč鹊ą╣čćąĖą▓ąŠčüčéčī ą║ ą▒čāč乥čĆąĮąŠą╝čā čĆąĄąČąĖą╝čā čĆą░ą▒ąŠčéčŗ ąĖ ą┐čĆąĖąĄą╝ą╗ąĄą╝ą░čÅ čüč鹊ąĖą╝ąŠčüčéčī. ąØąŠ ą┤ą╗čÅ čŹčéąĖčģ ąÉąÜąæ ąŠč湥ąĮčī ą▓ą░ąČąĄąĮ ą║ąŠąĮčéčĆąŠą╗čī ą┐čĆąŠčåąĄčüčüą░ ąĘą░čĆčÅą┤ą░ ąĖ čĆą░ąĘčĆčÅą┤ą░ ą┤ą╗čÅ ąĖąĘą▒ąĄą│ą░ąĮąĖčÅ ą▓ąŠąĘą┤ąĄą╣čüčéą▓ąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ ąĘą░čĆčÅą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ 100% ąĘą░čĆčÅą┤ą░. ąśąĮąČąĄąĮąĄčĆčŗ ąÜą×ą£ą¤ąŁąø ą┐ąŠą┤ą│ąŠč鹊ą▓ąĖą╗ąĖ čüą┐ąĖčüąŠą║ čéą░ą║ąĖčģ čĆąĄčłąĄąĮąĖą╣ ąŠčé čĆą░ąĘąĮčŗčģ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĄą╣.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ>>

ąĀąĄą║ą╗ą░ą╝ą░

ąĀąĄą║ą╗ą░ą╝ą░

ąØąŠą▓čŗą╣ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ EVE čüąĄčĆąĖąĖ PLM ą┤ą╗čÅ GSM-čéčĆąĄą║ąĄčĆąŠą▓, čĆą░ą▒ąŠčéą░čÄčēąĖčģ ą▓ ąČčæčüčéą║ąĖčģ čāčüą╗ąŠą▓ąĖčÅčģ (ą┤ąŠ -40┬░ąĪ)

ąÜąŠą╝ą┐ą░ąĮąĖčÅ EVE ą▓čŗą┐čāčüčéąĖą╗ą░ ąĮąŠą▓čŗą╣ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ čüąĄčĆąĖąĖ PLM, čüąŠč湥čéą░čÄčēąĖą╣ ą▓ čüąĄą▒ąĄ ą▓čŗčüąŠą║čāčÄ ą▒ąĄąĘąŠą┐ą░čüąĮąŠčüčéčī, ą┤ą╗ąĖč鹥ą╗čīąĮčŗą╣ čüčĆąŠą║ čüą╗čāąČą▒čŗ, čłąĖčĆąŠą║ąĖą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĮčŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĖ ą▓čŗčüąŠą║čāčÄ č鹊ą║ąŠąŠčéą┤ą░čćčā ą┤ą░ąČąĄ ą┐čĆąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ.

ąŁčéąĖ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆčŗ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąĘą░čĆčÅą┤ ą┐čĆąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ ąŠčé -40/-20┬░ąĪ (čüąĮąĖąČąĄąĮąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ č鹊ą║ą░), ą▒ąĄąĘąŠą┐ą░čüąĮčŗ (ąĮąĄ ą▓ąŠčüą┐ą╗ą░ą╝ąĄąĮčÅčÄčéčüčÅ ąĖ ąĮąĄ ą▓ąĘčĆčŗą▓ą░čÄčéčüčÅ) ą┐čĆąĖ ą╝ąĄčģą░ąĮąĖč湥čüą║ąŠą╝ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖąĖ (ą┐čĆąŠčéčŗą║ą░ąĮąĖąĄ ąĖ čüą┤ą░ą▓ą╗ąĖą▓ą░ąĮąĖąĄ), čāčüč鹊ą╣čćąĖą▓čŗ ą║ ą▓ąĖą▒čĆą░čåąĖąĖ. ą×ąĮąĖ ą╝ąŠą│čāčé ą┐čĆąĖą╝ąĄąĮčÅčéčīčüčÅ ą║ą░ą║ ą┤ą╗čÅ ą░ą▓č鹊čéčĆą░ąĮčüą┐ąŠčĆčéą░ (čéčĆąĄą║ąĄčĆčŗ, ą╝ą░čÅčćą║ąĖ, čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖčÅ), čéą░ą║ ąĖ ą┤ą╗čÅ ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░, IoT-čāčüčéčĆąŠą╣čüčéą▓.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ>>

greeka

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčé ą╝ą░čĆ 21, 2017 22:14:22

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé čÅąĮą▓ 12, 2017 14:13:48ąĪąŠąŠą▒čēąĄąĮąĖą╣: 24

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąśąĘą▓ąĖąĮąĖč鹥, ąĮąĄ č鹊 čüą║ąŠą┐ąĖą┐ą░čüčéąĖą╗. ą×ą▒ąĮąŠą▓ąĖą╗. ąÜąŠąĮąĄčćąĮąŠ ąČąĄ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 0x0F (ą┐ąĄčĆąĄčģąŠą┤ ą▓ RX ą┐ąŠčüą╗ąĄ ąŠčéą┐čĆą░ą▓ą║ąĖ ąĖ ą┐ąŠą╗čāč湥ąĮąĖčÅ).

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

Ser60

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčé ą╝ą░čĆ 21, 2017 23:30:10

ąöčĆčāą│ ąÜąŠčéą░

ąÜą░čĆą╝ą░: 74

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 607

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪčĆ ą┤ąĄą║ 24, 2008 09:58:58ąĪąŠąŠą▒čēąĄąĮąĖą╣: 3715

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą£ąĄą┤ą░ą╗ąĖ: 3

ąÆąŠąŠą▒čēąĄ, ą▓ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖčæą╝ą░ ą┐ą░ą║ąĄčéą░ ą┐ąŠ GDO0, ą┐ą░ą┤ą░čÄčēąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ ąĮčæą╝ čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠ ą┐čĆąĖąĮčÅčéąĖąĖ ą╗ąĖčłčī čüą╗ąŠą▓ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ. ąöą╗čÅ ą╝ąŠą╝ąĄąĮčéą░ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐čĆąĖąĮčÅčéąĖčÅ ą┐ą░ą║ąĄčéą░ čüą╗ąĄą┤čāąĄčé ą┤ąŠąČą┤ą░čéčīčüčÅ ąĮą░čĆą░čüčéą░čüčéą░čÄčēąĄą│ąŠ čāčĆąŠą▓ąĮčÅ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ ą║ą░ą║ ąŠąĮ čāą┐ą░ą╗. ą» čŹč鹊 ą┤ąĄą╗ą░čÄ ąŠą▒čŗčćąĮąŠ čéą░ą║ (ą║ąŠą┤ ą┤ą╗čÅ MSP430):

ąĪą┐ąŠą╣ą╗ąĄčĆ ąÜąŠą┤:

P1IES_bit.GDO0 = 0; // set INT on low-to-high transition

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

greeka

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪčĆ ą╝ą░čĆ 22, 2017 01:19:18

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé čÅąĮą▓ 12, 2017 14:13:48ąĪąŠąŠą▒čēąĄąĮąĖą╣: 24

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąÜą░ą║ ą│ąŠą▓ąŠčĆąĖčé ą┤ą░čéą░čłąĖčé:

ą”ąĖčéą░čéą░:

6 (0x06) - Asserts when sync word has been sent / received, and de-asserts at the end of the packet.

ąØą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ ąĮąĄ ą▓ąĖą┤ąĮąŠ, ąĮąŠ čāčĆąŠą▓ąĄąĮčī čüčéą░ąĮąŠą▓ąĖčéčüčÅ = 1, ą┐ąŠč鹊ą╝ č湥čĆąĄąĘ 1,5 ms ą┐ą░ą┤ą░ąĄčé. ą¤ąŠą╗ą░ą│ą░čÄ ą║ąŠą│ą┤ą░ 1 - čŹč鹊 ą┐čĆąĖąĄą╝ čüąĖąĮą║ čüą╗ąŠą▓ą░, ą║ąŠą│ą┤ą░ 0 - ąŠą║ąŠąĮčćą░ąĮąĖąĄ ą┐ą░ą║ąĄčéą░.

ąŻ ą╝ąĄąĮčÅ ąĮą░čüčéčĆąŠąĄąĮą░ ą░ą▓č鹊ąŠčćąĖčüčéą║ą░ FIFO ą┐ąŠ ą▒ąĖč鹊ą╝čā ą┐ą░ą║ąĄčéčā (CRC) ąĖ čüąŠą▒čüčéą▓ąĄąĮąĮąŠ ą┐ą░ą║ąĄčé ą║ą░ą║ ą▓ąĖą┤ąĮąŠ ąĮą░ ą║ą░čĆčéąĖąĮą║ąĄ čćąĖčéą░ąĄčéčüčÅ ą║ąŠčĆčĆąĄą║čéąĮąŠ.

UPD: ą» ą┐ąŠąĮčÅą╗ ą┐čĆąŠ čćč鹊 ą▓čŗ: ąĮą░čüčéčĆąŠą╣ą║ą░ ąĖąĮą▓ąĄčĆčüąĖąĖ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą╗ąĖąĮąĖąĖ:

ą”ąĖčéą░čéą░:

0x02: IOCFG0 ŌĆō GDO0 Output Pin Configuration

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

Ser60

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪčĆ ą╝ą░čĆ 22, 2017 03:52:39

ąöčĆčāą│ ąÜąŠčéą░

ąÜą░čĆą╝ą░: 74

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 607

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪčĆ ą┤ąĄą║ 24, 2008 09:58:58ąĪąŠąŠą▒čēąĄąĮąĖą╣: 3715

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą£ąĄą┤ą░ą╗ąĖ: 3

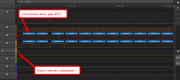

ąöą░, ą┐ąŠąČą░ą╗čāą╣ ąÆčŗ ą┐čĆą░ą▓čŗ ąĮą░čüčćčæčé GDO0, čÅ čāąČąĄ ą┐ąŠą┤ąĘą░ą▒čŗą╗. ą×ą┤ąĮą░ą║ąŠ, čÅ čüąĄą╣čćą░čü ąĮą░čüčéčĆąŠąĖą╗ ąŠą┤ąĖąĮ ąĖąĘ čćąĖą┐ąŠą▓ ą▓ Studio ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā CC-ą┤ąĄą▒ą░ą│ą│ąĄčĆąŠą╝, ą┤čĆčāą│ąŠą╣ ąĮą░ ą┐čĆąĖčæą╝ ą▓ ą┤ąĄč乊ą╗čéąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ (ą▓ ZIP ą░čĆčģąĖą▓ąĄ ą▓ąĮąĖąĘčā) ą▒ąĄąĘ ą▓čŗčģąŠą┤ą░ ąĖąĘ čĆąĄąČąĖą╝ą░ RX. ąś ąŠąĮ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠ ąĖąĘ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░ ąĮąĄ ą▓čŗčģąŠą┤ąĖčé ą┐ąŠ ą┐čĆąĖčæą╝čā ą┐ą░ą║ąĄčéą░ (čüą╝. ąŠčüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝čā). ą¤ą░ą║ąĄčé čüąŠčüč鹊ąĖčé ąĖąĘ čüą╗ąŠą▓ą░ "test" čü 2 ą┐čĆąĄą┤čłąĄčüčéą▓čāčÄčēąĖą╝ąĖ ą▒ą░ą╣čéą░ą╝ąĖ ąĮąŠą╝ąĄčĆą░ ą┐ą░ą║ąĄčéą░ ąĖ ą▒ą░ą╣čéą░ą╝ąĖ RSSI ąĖ CRC ą▓ ą║ąŠąĮčåąĄ. ą¤ąŠčćąĖčéą░ą╣č鹥 ąĄčĆčĆą░čéčā ąĮą░ čüą▓ąŠčÄ ą▓ąĄčĆčüąĖčÄ. ą¦ąĖą┐ čüą╗čāčćą░ąĄą╝ ąĮąĄ ą║ąĖčéą░ą╣čüą║ą░čÅ ą┐ąŠą┤ą┤ąĄą╗ą║ą░? ąśąĮč鹥čĆąĄčüąĮąŠ, čćč鹊 čā ąÆą░čü ą╗ąĄąČąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ 0čģ31? ąŻ ą╝ąĄąĮčÅ 0čģ14 - ą┐ąŠą║čāą┐ą░ą╗ ąĄą│ąŠ ą│ąŠą┤ą░ 4 ąĮą░ąĘą░ą┤.

ąĪą┐ąŠą╣ą╗ąĄčĆ ąÜčüčéą░čéąĖ, ą┐ąŠčüą╗ąĄ čćč鹥ąĮąĖčÅ ą┤ą╗ąĖąĮčŗ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą┐ą░ą║ąĄčéą░ ą║ąŠą╝ą░ąĮą┤ąŠą╣ 0xFB čüą╗ąĄą┤čāąĄčé ą┐ąĄčĆąĄą┤čæčĆąĮčāčéčī CS ąĖ čāąČąĄ ą┐ąŠč鹊ą╝ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╣ čüąĄčüčüąĖąĖ čćąĖčéą░čéčī RX FIFO ą║ąŠą╝ą░ąĮą┤ąŠą╣ 0xFF.

ąÆą╗ąŠąČąĄąĮąĖąĄ:

cc1101rx.png [66.36 KiB]

ąĪą║ą░čćąĖą▓ą░ąĮąĖą╣: 832

ąÆą╗ąŠąČąĄąĮąĖąĄ:

CC1101.zip [1.48 KiB]

ąĪą║ą░čćąĖą▓ą░ąĮąĖą╣: 206

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

greeka

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪčĆ ą╝ą░čĆ 22, 2017 10:14:42

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé čÅąĮą▓ 12, 2017 14:13:48ąĪąŠąŠą▒čēąĄąĮąĖą╣: 24

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąÉ ąĄčüčéčī ą┐ąŠą┤ą┤ąĄą╗ą║ąĖ CC1101? ąÜą░ą║ ąĖčģ čĆą░čüą┐ąŠąĘąĮą░čéčī?

ąŻ ą╝ąĄąĮčÅ ąĮą░ čéą░ą║ąĖčģ ą╝ąŠą┤čāą╗čÅčģ:

ą”ąĖčéą░čéą░:

ąÜčüčéą░čéąĖ, ą┐ąŠčüą╗ąĄ čćč鹥ąĮąĖčÅ ą┤ą╗ąĖąĮčŗ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą┐ą░ą║ąĄčéą░ ą║ąŠą╝ą░ąĮą┤ąŠą╣ 0xFB čüą╗ąĄą┤čāąĄčé ą┐ąĄčĆąĄą┤čæčĆąĮčāčéčī CS ąĖ čāąČąĄ ą┐ąŠč鹊ą╝ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╣ čüąĄčüčüąĖąĖ čćąĖčéą░čéčī RX FIFO ą║ąŠą╝ą░ąĮą┤ąŠą╣ 0xFF.

ąŻ ą╝ąĄąĮčÅ čéą░ą║ ąĖ ąĄčüčéčī, čüą╝. čüą░ą╝čŗą╣ ą┐ąĄčĆą▓čŗą╣ ą┐ąŠčüčé, čéą░ą╝ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ąŠčéą▓ąĄčéą░ ąŠčé FB ą┤ąĄčĆą│ą░ąĄčéčüčÅ ą▓ąĄčĆčģąĮčÅčÅ ą╗ąĖąĮąĖčÅ - čŹč鹊 CSN

ąÆ čĆąĄą│ąĖčüčéčĆąĄ 0x31 (0xF1) ą╗ąĄąČąĖčé 0x14

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

greeka

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪčĆ ą╝ą░čĆ 22, 2017 18:04:08

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé čÅąĮą▓ 12, 2017 14:13:48ąĪąŠąŠą▒čēąĄąĮąĖą╣: 24

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

Serg1987

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą╝ą░čĆ 23, 2017 15:04:03

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤ąĮ ąĖčÄąĮ 13, 2016 10:41:52ąĪąŠąŠą▒čēąĄąĮąĖą╣: 129

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąźąŠčĆąŠčłąŠ ąČąĄ ą▓ą░ą╝. ąŻ ą╝ąĄąĮčÅ ą▓ąŠąĮ čü Si4432 ąŠą┤ąĮąĖ ą▒ą░ą│ąĖ.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

Ser60

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą╝ą░čĆ 23, 2017 16:55:05

ąöčĆčāą│ ąÜąŠčéą░

ąÜą░čĆą╝ą░: 74

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 607

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪčĆ ą┤ąĄą║ 24, 2008 09:58:58ąĪąŠąŠą▒čēąĄąĮąĖą╣: 3715

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą£ąĄą┤ą░ą╗ąĖ: 3

ąźą╝ą╝ą╝, ąĖ čü čüąĖą╗ą╗ą░ą▒ąŠą▓čüą║ąĖą╝ąĖ čā ą╝ąĄąĮčÅ ąĮąĖą║ąŠą│ą┤ą░ ą┐čĆąŠą▒ą╗ąĄą╝ ąĮąĄ ą▒čŗą╗ąŠ - čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ čćą░čüčŗ. ą¤čĆą░ą▓ą┤ą░, ą┤ąĄą╗ąŠ ą┤ąŠą▓ąĄą╗ąŠčüčī ąĖą╝ąĄčéčī č鹊ą╗čīą║ąŠ čü Si446x čüąĄčĆąĖąĄą╣, ą┐čĆąĖčæą╝ąĮąĖą║ąŠą╝ Si4362, ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ąŠą╝ 4060 ąĖ ąĄčēčæ ąĮąĄ ą┐ąŠą╝ąĮčÄ č鹊čćąĮąŠ ą║ą░ą║ąĖą╝ąĖ, ąĮąŠ č鹊čćąĮąŠ ąĮąĄ čüąŠ čüčéą░čĆąŠą╣ čüąĄčĆąĖąĄą╣ Si443x. ąĪąĄą╣čćą░čü ą┤ąĄą╗ą░čÄ ą┐čĆąŠąĄą║čé ąĮą░ Si4468 čü ą▓čŗčģąŠą┤ąĮąŠą╣ ą╝ąŠčēąĮąŠčüčéčīčÄ +20dBm, ą┐ąŠą║ą░ ąŠąĮ ą▓ čüčéą░ą┤ąĖąĖ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ. ąŻ ą╝ąĄąĮčÅ čéčāčé, ą║čüčéą░čéąĖ, ąĮąĄčüą║ąŠą╗čīą║ąŠ čüčéą░č鹥ą╣ ą▓ čłąĄčĆčüčéąĖ ą┐čĆąŠ ą╝ąŠą┤čāą╗ąĖ ąĮą░ Si ąĮą░ą╣ą┤č鹥. ą£ąŠą┤čāą╗ąĖ ą▓čüąĄą│ą┤ą░ ą┤ąĄą╗ą░ą╗ ą┐ąŠą┤ ąĮąĖčģ čüą░ą╝ čü ąŠą┤ąĮąĖą╝ ą╗ąĖčłčī ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ą▓ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ čüčéą░čéčīąĄ. ąØąŠ ą▓ ą╗čÄą▒ąŠą╝ čüą╗čāčćą░ąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗ ąĮąĄą║ąĖčéą░ą╣čüą║ąĖąĄ ą╝ąŠą┤čāą╗ąĖ (ą▓ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ čüčéą░čéčīąĄ) ąĖ ą┐ąŠą║čāą┐ą░ą╗ ą▓čüąĄ Si čćąĖą┐čŗ č鹊ą╗čīą║ąŠ čā ąŠčäąĖčåąĖą░ą╗čīąĮčŗčģ ą┤ąĖčüčéčĆąĖą▒čŖčÄč鹊čĆąŠą▓. ąĪ ą┐ąŠą║čāą┐ą║ąŠą╣ ąĮą░ ąÉą╗ąĖ čā ą╝ąĄąĮčÅ ąĮčāą╗ąĄą▓ąŠą╣ ąŠą┐čŗčé, č鹊ą╗čīą║ąŠ čüąŠ čüą╗čāčģąŠą▓ ąĘąĮą░čÄ, čćč鹊 čéą░ą╝ ą▒čŗą▓ą░čÄčé ą┐ąŠą┤ą┤ąĄą╗ą║ąĖ.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

greeka

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą╝ą░čĆ 23, 2017 20:35:58

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé čÅąĮą▓ 12, 2017 14:13:48ąĪąŠąŠą▒čēąĄąĮąĖą╣: 24

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą”ąĖčéą░čéą░:

greeka - ąĄčüą╗ąĖ č鹊, ąŠ čćčæą╝ ą┐ąĖčłąĖč鹥, ąĄą┤ąĖąĮčüčéą▓ąĄąĮąĮą░čÅ ą┐čĆąŠą▒ą╗ąĄą╝ą░, čćč鹊 ą╝ąĄčłą░ąĄčé ąÆą░ą╝ ą┐ąŠą┤ą░čéčī ą║ąŠą╝ą░ąĮą┤čā ą┐ąĄčĆąĄą▓ąŠą┤ą░ ą╝ąŠą┤čāą╗čÅ ą▓ RX ą┐ąŠčüą╗ąĄ ą▓čŗą│čĆčāąĘą║ąĖ ąĖąĘ ąĮąĄą│ąŠ ą┐ą░ą║ąĄčéą░? ąśą╗ąĖ ąĖą╝ąĄąĄčéčüčÅ ąŠą┐ą░čüąĮąŠčüčéčī ą┐čĆąŠą┐čāčüčéąĖčéčī ą║ą░ą║ąŠą╣-č鹊 ą┐ą░ą║ąĄčé ąĘą░ ą▓čĆąĄą╝čÅ ą▓čŗą│čĆčāąĘą║ąĖ?

Ser60 ąŠčéą▓ąĄčćčā ą▓ą░ą╝ ą▓ čüą▓ąŠąĄą╣ č鹥ą╝ąĄ.

ąÆąŠąŠą▒čēąĄą╝-č鹊 ą┐čĆąŠą▒ą╗ąĄą╝čŗ ąĮąĄčé, čéą░ą║ ąĖ ą┤ąĄą╗ą░čÄ. ąæąŠą╗ąĄąĄ č鹊ą│ąŠ, ą┐čĆąĖąĄą╝ąĮąĖą║ ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┤ąŠą╗ą│ąŠ ą┤ąĄčƹȹ░čéčī ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą┐čĆąĖąĄą╝ą░ čé.ą║. ąŠąĮ čāą┐ą╗čŗą▓ą░ąĄčé. ąØąŠ ąĮą░čüč鹊čĆąŠąČąĖą╗ą░ čŹčéą░ čüąĖčéčāą░čåąĖčÅ, ą┤čāą╝ą░ą╗ čćč鹊 čÅ čćč鹊-č鹊 čāą┐čāčüčéąĖą╗, ą▓ąĄą┤čī ą┤ąŠą╗ąČąĮąŠ ąČąĄ čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ ąĘą░čÅą▓ą╗ąĄąĮąŠ.

ąĢčēąĄ ą╝ąĮąĄ ąĮąĄą┐ąŠąĮčÅč鹥ąĮ čéą░ą║ąŠą╣ ą╝ąŠą╝ąĄąĮčé - ąĄčüą╗ąĖ čÅ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ą┐ą░ą┤ąĄąĮąĖčÅ ąĖą╝ą┐čāą╗čīčüą░ ąĮą░ ą╗ąĖąĮąĖąĖ GDO0 ą▒čāą┤čā ąĮąĄ ą┐čŗčéą░čéčīčüčÅ ą▓čŗą│čĆčāąĘąĖčéčī ą┐ą░ą║ąĄčé, ą░ ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčī ą▓ čĆąĄąČąĖą╝ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąŠč鹊ą╝ ą▓čŗą│čĆčāąČą░čéčī č鹥ą║čāčēąĖą╣ ą┐čĆąĖąĮčÅčéčŗą╣ ą┐ą░ą║ąĄčé, ą┐čĆąĖ čŹč鹊ą╝ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčīčüčÅ ąĮąŠą▓čŗą╣ ą┐ą░ą║ąĄčé, ą▒čāą┤čāčé ą╗ąĖ ą▒ąĖčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ RX FIFO?

ą”ąĖčéą░čéą░:

ąŻ ą╝ąĄąĮčÅ čéčāčé, ą║čüčéą░čéąĖ, ąĮąĄčüą║ąŠą╗čīą║ąŠ čüčéą░č鹥ą╣ ą▓ čłąĄčĆčüčéąĖ ą┐čĆąŠ ą╝ąŠą┤čāą╗ąĖ ąĮą░ Si ąĮą░ą╣ą┤č鹥.

ą¤ąŠą┤čüą║ą░ąČąĖč鹥 ą║ą░ą║ čüčéą░čéčīąĖ ąĖčüą║ą░čéčī ą┐ąŠ ą░ą▓č鹊čĆčā? ąśą╗ąĖ ą┤ą░ą╣č鹥 čüčüčŗą╗ą║ąĖ ąĮą░ ąĮąĖčģ.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

GRAF

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą╝ą░čĆ 23, 2017 20:56:51

ą£čāą┤čĆčŗą╣ ą║ąŠčé

ąÜą░čĆą╝ą░: 2

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 5

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪčĆ čÅąĮą▓ 23, 2008 22:11:54ąĪąŠąŠą▒čēąĄąĮąĖą╣: 1867ą×čéą║čāą┤ą░: ąÜą░ą╗ąĖąĮąĖąĮą│čĆą░ą┤

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąĪčéčĆą░ąĮąĖčåą░ 2 Details

If a received data byte is written to the RX FIFO at the exact same time as the last byte in the RX FIFO is read over the SPI interface, the RX FIFO pointer is not properly updated and the last read byte is duplicated.

Workaround(s)

For packets below 64 bytes, it is recommended to wait until the complete packet has been received before reading it out.

ą”ąĖčéą░čéą░:

ąæąŠą╗ąĄąĄ č鹊ą│ąŠ, ą┐čĆąĖąĄą╝ąĮąĖą║ ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┤ąŠą╗ą│ąŠ ą┤ąĄčƹȹ░čéčī ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą┐čĆąĖąĄą╝ą░ čé.ą║. ąŠąĮ čāą┐ą╗čŗą▓ą░ąĄčé.

ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąĮąĄ ą░ą╝ą┐ą╗ąĖčéčāą┤ąĮą░čÅ ą╝ąŠą┤čāą╗čÅčåąĖčÅ, č鹊 čāčģąŠą┤ čćą░čüč鹊čéčŗ ą╝ąŠąČąĮąŠ ą║ąŠą╝ą┐ąĄąĮčüąĖčĆąŠą▓ą░čéčī, ą▓ ą┐čāąĮą║č鹥 14.1 ą┤ą░čéą░čłąĖčéą░ čüą║ą░ąĘą░ąĮąŠ.

ąŚą┤ąĄčüčī ą┐čĆąĖą╝ąĄčĆ.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

Ser60

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą╝ą░čĆ 23, 2017 21:43:31

ąöčĆčāą│ ąÜąŠčéą░

ąÜą░čĆą╝ą░: 74

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 607

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪčĆ ą┤ąĄą║ 24, 2008 09:58:58ąĪąŠąŠą▒čēąĄąĮąĖą╣: 3715

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą£ąĄą┤ą░ą╗ąĖ: 3

greeka ą┐ąĖčüą░ą╗(ą░):

ą▒čāą┤čāčé ą╗ąĖ ą▒ąĖčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ RX FIFO?

ąØąĄ ą▒čāą┤čāčé. ą¤ąŠ ą╝ąŠą┤čāą╗čÄ hardware ą▒ą░ą│ą░, čćč鹊

GRAF čāą║ą░ąĘą░ą╗.

greeka ą┐ąĖčüą░ą╗(ą░):

ą¤ąŠą┤čüą║ą░ąČąĖč鹥 ą║ą░ą║ čüčéą░čéčīąĖ ąĖčüą║ą░čéčī ą┐ąŠ ą░ą▓č鹊čĆčā? ąśą╗ąĖ ą┤ą░ą╣č鹥 čüčüčŗą╗ą║ąĖ ąĮą░ ąĮąĖčģ.

ąŻ ą╝ąĄąĮčÅ čéčāčé ąĮąĄčüą║ąŠą╗čīą║ąŠ čüčéą░č鹥ą╣ ąĮą░ č鹥ą╝čā. ąæčŗčüčéčĆąĄąĄ ą▒čāą┤ąĄčé ąÆą░ą╝ ąĮą░ąČą░čéčī ą║ąĮąŠą┐ą║čā ą¤čĆąŠčäąĖą╗čī ą┐ąŠą┤ čŹčéąĖą╝ ą╝ąŠąĖą╝ čüąŠąŠą▒čēąĄąĮąĖąĄą╝, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ čüčéą░čéčīčÅą╝.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

greeka

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą╝ą░čĆ 23, 2017 22:57:04

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé čÅąĮą▓ 12, 2017 14:13:48ąĪąŠąŠą▒čēąĄąĮąĖą╣: 24

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

GRAF ą┐ąĖčüą░ą╗(ą░):

ąĪčéčĆą░ąĮąĖčåą░ 2 Details

If a received data byte is written to the RX FIFO at the exact same time as the last byte in the RX FIFO is read over the SPI interface, the RX FIFO pointer is not properly updated and the last read byte is duplicated.

Workaround(s)

For packets below 64 bytes, it is recommended to wait until the complete packet has been received before reading it out.

ąØąĄ ą┐ąŠąĮčÅą╗ ą║ą░ą║ čŹč鹊 ąŠčéąĮąŠčüąĖčéčüčÅ ą║ č鹊ą╝čā, ąŠ č湥ą╝ čÅ ą┐ąĖčüą░ą╗.

ąÆąŠčé ą┐čĆąĖą╝ąĄčĆ - čā ą╝ąĄąĮčÅ ą┐ą░ą║ąĄčé ąĮą░ 60 ą▒ą░ą╣čé + čüąĖčüč鹥ą╝ąĮčŗąĄ 2 ą▒ą░ą╣čéą░ ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą▒ą░ą▓ą╗čÅąĄčé čüą░ą╝ čćąĖą┐. ą» ą┐ąŠą╗čāčćąĖą╗ ą┐ą░ą║ąĄčé, CRC čüąŠčłą╗ąŠčüčī, čćąĖą┐ ą┤ąĄčĆąĮčāą╗ ąĮąŠą│ąŠą╣. ą» ąĮą░čćąĖąĮą░čÄ čćąĖčéą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĖąĘ RX FIFO ąĖ ą▓ čŹč鹊čé ąČąĄ ą╝ąŠą╝ąĄąĮčé ą╝ąŠą┤čāą╗čī ąĮą░čćąĖąĮą░ąĄčé ą┐ąŠą╗čāčćą░čéčī ą┤ą░ąĮąĮčŗąĄ (č鹊ąČąĄ ą┐ą░ą║ąĄčé ąĮą░ 60 ą▒ą░ą╣čé). ą¤ąŠą┤ ą▒ą░ą│ čŹč鹊čé ą╝čŗ ąĮąĄ ą┐ąŠą┐ą░ą┤ą░ąĄą╝, ąĮąŠ čćč鹊 ą▒čāą┤ąĄčé čü ą┤ą░ąĮąĮčŗą╝ąĖ, ą║ąŠč鹊čĆčŗąĄ čÅ ąĄčēąĄ ąĮąĄ ą┐čĆąŠčćąĖčéą░ą╗ ąĖąĘ ą▒čāč乥čĆą░?

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ after 4 minutes 4 seconds: Ser60 ą┐ąĖčüą░ą╗(ą░):

ąŻ ą╝ąĄąĮčÅ čéčāčé ąĮąĄčüą║ąŠą╗čīą║ąŠ čüčéą░č鹥ą╣ ąĮą░ č鹥ą╝čā. ąæčŗčüčéčĆąĄąĄ ą▒čāą┤ąĄčé ąÆą░ą╝ ąĮą░ąČą░čéčī ą║ąĮąŠą┐ą║čā ą¤čĆąŠčäąĖą╗čī ą┐ąŠą┤ čŹčéąĖą╝ ą╝ąŠąĖą╝ čüąŠąŠą▒čēąĄąĮąĖąĄą╝, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ čüčéą░čéčīčÅą╝.

ąÉ čüą╗ąŠąĮą░-č鹊 čÅ ąĖ ąĮąĄ ąĘą░ą╝ąĄčéąĖą╗

ąæą╗ą░ą│ąŠą┤ą░čĆąŠčćą║ą░!

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

Ser60

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: CC1101 ą▓čŗčģąŠą┤ąĖčé ą▓ IDLE ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ ą░ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ą╝ą░čĆ 24, 2017 02:03:12

ąöčĆčāą│ ąÜąŠčéą░

ąÜą░čĆą╝ą░: 74

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 607

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪčĆ ą┤ąĄą║ 24, 2008 09:58:58ąĪąŠąŠą▒čēąĄąĮąĖą╣: 3715

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą£ąĄą┤ą░ą╗ąĖ: 3

greeka ą┐ąĖčüą░ą╗(ą░):

čćč鹊 ą▒čāą┤ąĄčé čü ą┤ą░ąĮąĮčŗą╝ąĖ, ą║ąŠč鹊čĆčŗąĄ čÅ ąĄčēąĄ ąĮąĄ ą┐čĆąŠčćąĖčéą░ą╗ ąĖąĘ ą▒čāč乥čĆą░?

ą×ąĮąĖ čéą░ą╝ ąĖ ą▒čāą┤čāčé čüąĖą┤ąĄčéčī ą┐ąŠą║ą░ ąĖčģ ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĄč鹥 ąĖą╗ąĖ ąĮąĄ ąŠčćąĖčüčéąĖč鹥 FIFO. ąØą░čüą║ąŠą╗čīą║ąŠ čÅ ą┐ąŠą╝ąĮčÄ, ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮ ą║ą░ą║ ą║ąŠą╗čīčåąĄą▓ąŠą╣ ą▒čāč乥čĆ. ąĢčüą╗ąĖ ą┤ą╗čÅ ą▓ąĮąŠą▓čī ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ ą▒ą░ą╣č鹊ą▓ ąĮąĄ ą▒čāą┤ąĄčé ą╝ąĄčüčéą░ ą▓ ąĮčæą╝, čćąĖą┐ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čĆąĄąČąĖą╝ RXFIFO_OVERFLOW ąĖ ą┐čĆąĖčæą╝ ą┐čĆąĄą║čĆą░čéąĖčé.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĪčéčĆą░ąĮąĖčåą░ 1 ąĖąĘ 1

[ ąĪąŠąŠą▒čēąĄąĮąĖą╣: 20 ]

ąÜč鹊 čüąĄą╣čćą░čü ąĮą░ č乊čĆčāą╝ąĄ

ąĪąĄą╣čćą░čü čŹč鹊čé č乊čĆčāą╝ ą┐čĆąŠčüą╝ą░čéčĆąĖą▓ą░čÄčé: ąĮąĄčé ąĘą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╣ ąĖ ą│ąŠčüčéąĖ: 32

ąÆčŗ ąĮąĄ ą╝ąŠąČąĄč鹥 ąĮą░čćąĖąĮą░čéčī č鹥ą╝čŗąĮąĄ ą╝ąŠąČąĄč鹥 ąŠčéą▓ąĄčćą░čéčī ąĮą░ čüąŠąŠą▒čēąĄąĮąĖčÅąĮąĄ ą╝ąŠąČąĄč鹥 čĆąĄą┤ą░ą║čéąĖčĆąŠą▓ą░čéčī čüą▓ąŠąĖ čüąŠąŠą▒čēąĄąĮąĖčÅąĮąĄ ą╝ąŠąČąĄč鹥 čāą┤ą░ą╗čÅčéčī čüą▓ąŠąĖ čüąŠąŠą▒čēąĄąĮąĖčÅąĮąĄ ą╝ąŠąČąĄč鹥 ą┤ąŠą▒ą░ą▓ą╗čÅčéčī ą▓ą╗ąŠąČąĄąĮąĖčÅ