|

ążąŠčĆčāą╝ ąĀą░ą┤ąĖąŠąÜąŠčé • ą¤čĆąŠčüą╝ąŠčéčĆ č鹥ą╝čŗ - ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ

ąĪąŠąŠą▒čēąĄąĮąĖčÅ ą▒ąĄąĘ ąŠčéą▓ąĄč鹊ą▓ | ąÉą║čéąĖą▓ąĮčŗąĄ č鹥ą╝čŗ

|

ąĪčéčĆą░ąĮąĖčåą░ 316 ąĖąĘ 380

|

[ ąĪąŠąŠą▒čēąĄąĮąĖą╣: 7597 ] |

... , , , , , , ... |

| ąÉą▓č鹊čĆ |

ąĪąŠąŠą▒čēąĄąĮąĖąĄ |

trofim2

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé čÅąĮą▓ 12, 2018 18:01:36 |

|

ąÜą░čĆą╝ą░: 3

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 7

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé čüąĄąĮ 10, 2015 06:59:03

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 106

ą×čéą║čāą┤ą░: ąōčĆąŠą┤ąĮąŠ, BY

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

|

|

|

|

|

WiseLord

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé čÅąĮą▓ 12, 2018 23:14:38 |

|

| ąöčĆčāą│ ąÜąŠčéą░ |

|

ąÜą░čĆą╝ą░: 86

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 1018

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé ą░ą┐čĆ 11, 2013 11:19:59

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 4875

ą×čéą║čāą┤ą░: ą£ąĖąĮčüą║

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

ąśą╝čģąŠ, ąĄčüą╗ąĖ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ ąĄčüčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, č鹊 ą▓čüąĄ čŹčéąĖ čüčāą┐ąĄčĆč鹊čćąĮčŗąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ ą┐čĆąĄą▓čĆą░čēą░čÄčéčüčÅ ą▓ čéčŗą║ą▓čā. ąÉ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĄčüčéčī ą▓ ą╗čÄą▒ąŠą╣ ą╝ą░ą╗ąŠ-ą╝ą░ą╗čīčüą║ąĖ čüą╗ąŠąČąĮąŠą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ.

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

|

|

|

|

|

trofim2

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪą▒ čÅąĮą▓ 13, 2018 08:11:28 |

|

ąÜą░čĆą╝ą░: 3

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 7

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé čüąĄąĮ 10, 2015 06:59:03

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 106

ą×čéą║čāą┤ą░: ąōčĆąŠą┤ąĮąŠ, BY

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

ą¤čĆąĖ ą╝ąĖą║čĆąŠčüąĄą║čāąĮą┤ąĮčŗčģ ąĘą░ą┤ąĄčƹȹ║ą░čģ, ą┐čĆąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ, ą╝ąŠąČąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ ąĘą░ą┐čĆąĄčéąĖčéčī.

ąÆ ą║ą░ąČą┤ąŠą╝ ą║ąŠąĮą║čĆąĄčéąĮąŠą╝ čüą╗čāčćą░ąĄ čĆąĄčłą░čéčī čüą░ą╝ąŠą╝čā, čćč鹊 ą▓ą░ąČąĮąĄąĄ, ą░ čćč鹊 ąĮąĄčé.

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

|

|

|

|

|

BOB51

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪą▒ čÅąĮą▓ 13, 2018 10:22:02 |

|

| ąöčĆčāą│ ąÜąŠčéą░ |

|

ąÜą░čĆą╝ą░: 93

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 1351

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčé ą╝ą░čĆ 16, 2010 22:02:27

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 14062

ą×čéą║čāą┤ą░: ąöą×ąØąĢą”ąÜ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

ą×ą▒čŗčćąĮąŠ ą┐čĆąĖ ąŠčüąŠą▒čŗčģ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅčģ ąĘą░ą┤ąĄčƹȹ║ąĖ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ. ą¤čĆąĖ ą┐ąŠą┤ąŠą▒ąĮąŠą╝ ą┐ąŠą┤čģąŠą┤ąĄ ąĄčüč鹥čüčéą▓ąĄąĮąĮąŠ ąĘą░ą┐čĆąĄčēą░čÄčéčüčÅ ąÆąĪąĢ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮą░ ą▓čĆąĄą╝čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą║čĆąĖčéąĖčćąĮčŗčģ ą▓čĆąĄą╝ąĄąĮąĮčŗčģ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ą┐čĆąŠą▒ą╗ąĄą╝ą░ - čāč湥čé ąĮąĄčĆą░ą▓ąĮąŠčåąĄąĮąĮąŠčüčéąĖ ą▓čĆąĄą╝ąĄąĮąĖ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą║ąŠą╝ą░ąĮą┤ čāčüą╗ąŠą▓ąĮąŠą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ ą▓ ą║ąŠąĮčåąĄ čüč湥čéąĮąŠą│ąŠ čåąĖą║ą╗ą░. ąś ą┤ąŠą▒ą░ą▓ąŠą║ ą▓ ą▓ąĖą┤ąĄ ąŠčåąĄąĮą║ąĖ čāčüą╗ąŠą▓ąĖą╣ ą┐čĆąĖ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čåąĖą║ą╗ąŠą▓ ą▓ ąĄą┤ąĖąĮąŠą╝ ą░ą╗ą│ąŠčĆąĖčéą╝ąĄ. ąÜą░ą║ ą┐čĆąĖą╝ąĄčĆ ąŠčüąŠą▒ąŠ ąČąĄčüčéą║ąŠą│ąŠ ą┐ąŠą┤čģąŠą┤ą░ ą║ čĆą░ą▓ąĮąŠąĘąĮą░čćąĮąŠčüčéąĖ čüąĄčĆąĖąĖ ą▓čĆąĄą╝ąĄąĮąĮčŗčģ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą┐čĆąĖ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąŠčåąĄąĮą║ąĄ čāčüą╗ąŠą▓ąĖą╣ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ čåąĖą║ą╗ąŠą▓ - ą┐čĆąŠą│čĆą░ą╝ą╝ąĮą░čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖčÅ ą┐čĆąŠč鹊ą║ąŠą╗ą░ ąŠą▒ą╝ąĄąĮą░ ą┤ą╗čÅ čüą▓ąĄč鹊ą┤ąĖąŠą┤ąŠą▓ čéąĖą┐ą░ WS2812 (ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą║ą░ą║ 菹╗ąĄą╝ąĄąĮčé - ąĘą░ą│ąŠč鹊ą▓ą║ą░ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ąĖ): ąĪą┐ąŠą╣ą╗ąĄčĆ;

;

; trd2812_m.txt

;

; čäą░ą╣ą╗ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą╝ą░čüčüąĖą▓ą░

; ąĖąĘ ą▒čāč乥čĆą░ ą▓čŗą▓ąŠą┤ą░ ą▓ ą╗ąĖąĮąĄą╣ą║čā ąĮą░ ąŠčüąĮąŠą▓ąĄ WS2812B

; ą▒ą░ąĘąŠą▓čŗą╣ ą£ąÜ ąĖąĘ ą╗ąĖąĮąĄą╣ą║ąĖ ąÉąóą£ąĢąø ą┐čĆąĖ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥

; ąŠčé 16 ą£ąĄą│ą░ą│ąĄčĆčå ( 0,000000062 S)

;

; čéčĆąĄą▒čāąĄą╝čŗąĄ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą┐ąŠ ą┤ą░čéą░čłąĖčéčā WS2812B

;

;Data transfer time( TH+TL=1.25┬Ąs┬▒600ns)

; T0H 0 code ,high voltage time 0.4us ┬▒150ns

; T1H 1 code ,high voltage time 0.8us ┬▒150ns

; T0L 0 code ,low voltage time 0.85us ┬▒150ns

; T1L 1 code ,low voltage time 0.45us ┬▒150ns

; RES low voltage time Above 50┬Ąs

; ąĖčüčģąŠą┤ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąĖąĮąĖąĖ čüą▓čÅąĘąĖ = 0

; ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┐ą░ą║ąĄčéą░ą╝ąĖ ąĖąĘ čéčĆąĄčģ ą▒ą░ą╣čé ąĮą░ č鹊čćą║čā

; čüčéą░čĆčłąĖą╝ąĖ ą▒ąĖčéą░ą╝ąĖ ą▓ą┐ąĄčĆąĄą┤ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ

; čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ G - R - B čåą▓ąĄčéą░ą╝ č鹊čćą║ąĖ

; ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą╗ąŠą║ąŠą▓ ą┤ąŠą╗ąČąĮąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī

; ą║ąŠą╗ąĖč湥čüčéą▓čā č鹊č湥ą║ ą▓ ą╗ąĄąĮč鹥

;

; čĆąĄą░ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ čüąŠą│ą╗ą░čüąĮąŠ č鹥čüčé - ąŠčéą╗ą░ą┤ą║ąĖ ą┤ąĄą▒ą░ą│ą│ąĄčĆąŠą╝ (ą▓ąĄčĆčüąĖčÅ1!)

; ą░ą▓čĆ-čüčéčāą┤ąĖąŠ 4.19

;

; Data transfer time( TH+TL=1.38┬Ąs -10ns)

; T0H 0 code ,high voltage time 0.44us ┬▒10ns

; T1H 1 code ,high voltage time 0.88us ┬▒10ns

; T0L 0 code ,low voltage time 0.94us ┬▒10ns

; T1L 1 code ,low voltage time 0.50us ┬▒10ns

; RES low voltage time 192,88uS (Above 50┬Ąs)

;

; ą┤ą╗ąĖąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü ą┐ą░ą║ąĄč鹊ą╝ ąĘą░ą│čĆčāąĘą║ąĖ (x60*3) = 2175uS (0.002175)

; ąĖąĮč鹥čĆą▓ą░ą╗ ą╝ąĄąČą┤čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ (irq t/c0) = 0.004S (4000uS)

;

; define datas

; .equ port_out = PORTB ; ą┐ąŠčĆčé ą▓čŗą▓ąŠą┤ą░ (ą┐ąŠ čāčüą╝ąŠčéčĆąĄąĮąĖčÄ)

; .equ out_line = 0 ; ą╗ąĖąĮąĖčÅ ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ

; .equ bufout = SRAM_START ; ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ ą▓čŗą▓ąŠą┤ą░

; .equ pixel = 60 ; ą║ąŠą╗ąĖč湥čüčéą▓ąŠ č鹊č湥ą║ ą▓ ą╗ąĖąĮąĄą╣ą║ąĄ/ą╗ąĄąĮč鹥

; .equ bufout_size = (pixel * 3) ; ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▒ąŠą╗ąĄąĄ ąŠą▒čŖąĄą╝ą░ ą×ąŚąŻ - čüč鹥ą║!!!

;čéą░ą▒ą╗ąĖčåą░ ąŠą▒čīčÅą▓ą╗ąĄąĮąĮčŗčģ ąĖą╝ąĄąĮ - ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĀą×ąØ

;

; .def name = r31 ; ZH čĆąĄą│ąĖčüčéčĆ (ą┐ąŠą╗ąĮčŗą╣)

; .def name = r30 ; ZL čĆąĄą│ąĖčüčéčĆ (ą┐ąŠą╗ąĮčŗą╣)

; .def name = r29 ; YH čĆąĄą│ąĖčüčéčĆ (ą┐ąŠą╗ąĮčŗą╣)

; .def name = r28 ; YL čĆąĄą│ąĖčüčéčĆ (ą┐ąŠą╗ąĮčŗą╣)

; .def name = r27 ; XH čĆąĄą│ąĖčüčéčĆ (ą┐ąŠą╗ąĮčŗą╣) čāą║ą░ąĘą░č鹥ą╗čī č鹥ą║čāčēąĄą╣ čÅč湥ą╣ą║ąĖ ą╝ą░čüčüąĖą▓ą░ bufout

; .def name = r26 ; XL čĆąĄą│ąĖčüčéčĆ (ą┐ąŠą╗ąĮčŗą╣) čāą║ą░ąĘą░č鹥ą╗čī č鹥ą║čāčēąĄą╣ čÅč湥ą╣ą║ąĖ ą╝ą░čüčüąĖą▓ą░ bufout

; .def name = r25 ; čĆąĄą│ąĖčüčéčĆ (ą┐ąŠą╗ąĮčŗą╣) BH

; .def name = r24 ; čĆąĄą│ąĖčüčéčĆ (ą┐ąŠą╗ąĮčŗą╣) BL

; .def name = r23 ; čĆąĄą│ąĖčüčéčĆ (ą┐ąŠą╗ąĮčŗą╣)

; .def name = r22 ; čĆąĄą│ąĖčüčéčĆ (ą┐ąŠą╗ąĮčŗą╣)

; .def name = r21 ; čĆąĄą│ąĖčüčéčĆ (ą┐ąŠą╗ąĮčŗą╣)

; .def name = r20 ; čĆąĄą│ąĖčüčéčĆ (ą┐ąŠą╗ąĮčŗą╣)

; .def name = r19 ; čĆąĄą│ąĖčüčéčĆ (ą┐ąŠą╗ąĮčŗą╣)

; .def name = r18 ; čĆąĄą│ąĖčüčéčĆ (ą┐ąŠą╗ąĮčŗą╣)

; .def tmp1 = r17 ; čĆąĄą│ąĖčüčéčĆ (ą┐ąŠą╗ąĮčŗą╣) čüč湥čéčćąĖą║ ą▒ą░ą╣čé ą▓čŗą▓ąŠą┤ą░

; .def tmp0 = r16 ; čĆąĄą│ąĖčüčéčĆ (ą┐ąŠą╗ąĮčŗą╣) ą▒čāč乥čĆ ą▓čŗą▓ąŠą┤ąĖą╝ąŠą│ąŠ ą▒ą░ą╣čéą░

; .def regn = r15 ; čĆąĄą│ąĖčüčéčĆ (čāčĆąĄąĘą░ąĮ)

; .def regn = r14 ; čĆąĄą│ąĖčüčéčĆ (čāčĆąĄąĘą░ąĮ)

; .def regn = r11 ; čĆąĄą│ąĖčüčéčĆ (čāčĆąĄąĘą░ąĮ)

; .def regn = r10 ; čĆąĄą│ąĖčüčéčĆ (čāčĆąĄąĘą░ąĮ)

; .def regn = r9 ; čĆąĄą│ąĖčüčéčĆ (čāčĆąĄąĘą░ąĮ)

; .def regn = r8 ; čĆąĄą│ąĖčüčéčĆ (čāčĆąĄąĘą░ąĮ)

; .def regn = r7 ; čĆąĄą│ąĖčüčéčĆ (čāčĆąĄąĘą░ąĮ)

; .def regn = r6 ; čĆąĄą│ąĖčüčéčĆ (čāčĆąĄąĘą░ąĮ)

; .def regn = r5 ; čĆąĄą│ąĖčüčéčĆ (čāčĆąĄąĘą░ąĮ)

; .def regn = r4 ; čĆąĄą│ąĖčüčéčĆ (čāčĆąĄąĘą░ąĮ)

; .def regn = r3 ; čĆąĄą│ąĖčüčéčĆ (čāčĆąĄąĘą░ąĮ)

; .def regn = r2 ; čĆąĄą│ąĖčüčéčĆ (čāčĆąĄąĘą░ąĮ)

; .def matr = r1 ; čĆąĄą│ąĖčüčéčĆ (čāčĆąĄąĘą░ąĮ) r1 ą┐ąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī!!!

; .def madr = r0 ; čĆąĄą│ąĖčüčéčĆ (čāčĆąĄąĘą░ąĮ) r0 ą┐ąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī!!!

;

;----------

; .macro ;; ą▓ą▓ąŠą┤ ąĖ ą┐čĆąĄą┤ąŠą▒čĆą░ą▒ąŠčéą║ą░ ą┤ą░ąĮąĮčŗčģ

;

;

; .endmacro

;

;----------

;

; ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ą▒čāč乥čĆą░ ą▓čŗą▓ąŠą┤ą░ ą▓ ąŠą▒ą╗ą░čüčéąĖ ą┤ą░ąĮąĮčŗčģ

; .dseg

; .org bufout

;point0: .byte 3 ; g:r:b

;point1: .byte 3 ; g:r:b

;point2: .byte 3 ; g:r:b

;point3: .byte 3 ; g:r:b

;point4: .byte 3 ; g:r:b

;point5: .byte 3 ; g:r:b

;point6: .byte 3 ; g:r:b

;point7: .byte 3 ; g:r:b

;point8: .byte 3 ; g:r:b

;point9: .byte 3 ; g:r:b

;point10: .byte 3 ; g:r:b

;point11: .byte 3 ; g:r:b

;point12: .byte 3 ; g:r:b

;point13: .byte 3 ; g:r:b

;point14: .byte 3 ; g:r:b

;point15: .byte 3 ; g:r:b

;point16: .byte 3 ; g:r:b

;point17: .byte 3 ; g:r:b

;point18: .byte 3 ; g:r:b

;point19: .byte 3 ; g:r:b

;point20: .byte 3 ; g:r:b

;point21: .byte 3 ; g:r:b

;point22: .byte 3 ; g:r:b

;point23: .byte 3 ; g:r:b

;point24: .byte 3 ; g:r:b

;point25: .byte 3 ; g:r:b

;point26: .byte 3 ; g:r:b

;point27: .byte 3 ; g:r:b

;point28: .byte 3 ; g:r:b

;point29: .byte 3 ; g:r:b

;point30: .byte 3 ; g:r:b

;point31: .byte 3 ; g:r:b

;point32: .byte 3 ; g:r:b

;point33: .byte 3 ; g:r:b

;point34: .byte 3 ; g:r:b

;point35: .byte 3 ; g:r:b

;point36: .byte 3 ; g:r:b

;point37: .byte 3 ; g:r:b

;point38: .byte 3 ; g:r:b

;point39: .byte 3 ; g:r:b

;point40: .byte 3 ; g:r:b

;point41: .byte 3 ; g:r:b

;point42: .byte 3 ; g:r:b

;point43: .byte 3 ; g:r:b

;point44: .byte 3 ; g:r:b

;point45: .byte 3 ; g:r:b

;point46: .byte 3 ; g:r:b

;point47: .byte 3 ; g:r:b

;point48: .byte 3 ; g:r:b

;point49: .byte 3 ; g:r:b

;point50: .byte 3 ; g:r:b

;point51: .byte 3 ; g:r:b

;point52: .byte 3 ; g:r:b

;point53: .byte 3 ; g:r:b

;point54: .byte 3 ; g:r:b

;point55: .byte 3 ; g:r:b

;point56: .byte 3 ; g:r:b

;point57: .byte 3 ; g:r:b

;point58: .byte 3 ; g:r:b

;point59: .byte 3 ; g:r:b

;

;----------

.cseg

.org 0x0020 ; čüčéą░čĆąŠą▓ą░čÅ ą┐ąŠąĘąĖčåąĖčÅ 0čģ0020 !!!

slot0:

; 6/14 (6-4=2 ą┐ąŠčüąĄą╝čā čĆąŠą╗čī ąŠčüčéą░čéą║ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé CBI)

cbi port_out,out_line ; 2 čåąĖą║ą╗ą░

nop

nop

nop

nop

nop

nop

nop

nop

nop

ret ; 4 čåąĖą║ą╗ą░

.org (slot0+16)

slot1:

nop ; 13/7 (13-4=9)

nop

nop

nop

nop

nop

nop

cbi port_out,out_line ; 2 čåąĖą║ą╗ą░

nop

nop

ret ; 4 čåąĖą║ą╗ą░

.org 0x0060

xslot0:

; 6/14 (6-5=1 ą┐ąŠčüąĄą╝čā čĆąŠą╗čī ąŠčüčéą░čéą║ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé CBI čü ąĖąĘą▒čŗčéą║ąŠą╝ ą▓ 1 nop)

cbi port_out,out_line ; 2 čåąĖą║ą╗ą░

cbr zl,(1<<6) ; ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ čāą║ą░ąĘą░č鹥ą╗čÅ 1 čåąĖą║ą╗

nop

nop

nop

nop

nop

nop ; -2 čåąĖą║ą╗ą░ ąĮą░ ld tmp0,x+

dec tmp1 ; 1 čåąĖą║ą╗

brbs SREG_Z,ends_trd ; 1 čåąĖą║ą╗ ą┐čĆąĖ ąĮąĄąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĖ (ą▓ čåąĖą║ą╗ąĄ)

rjmp trasstt ; 2 čåąĖą║ą╗ą░

.org (xslot0+16)

xslot1:

nop ; 13/7 (13-5=8)

cbr zl,(1<<6) ; ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ čāą║ą░ąĘą░č鹥ą╗čÅ 1 čåąĖą║ą╗

nop

nop

nop

nop

nop

cbi port_out,out_line ; 2 čåąĖą║ą╗ą░

; -2 čåąĖą║ą╗ą░ ąĮą░ ld tmp0,x+

dec tmp1 ; 1 čåąĖą║ą╗

brbs SREG_Z,ends_trd ; 1 čåąĖą║ą╗ ą┐čĆąĖ ąĮąĄąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĖ (ą▓ čåąĖą║ą╗ąĄ)

rjmp trasstt ; 2 čåąĖą║ą╗ą░

;

ends_trd:

pop tmp0

pop tmp1

pop xl

pop xh

pop zl

pop zh ; ą▓ąŠčüčüčéą░ąĮąŠą▓ąĖčéčī čĆą░ą▒ąŠčćčāčÄ ąŠą▒ą╗ą░čüčéčī ąĖąĘ čüč鹥ą║ą░

ret

;----------

;

; ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ:

; ą╗ąĖąĮąĖčÅ out_line ąĮą░čüčéčĆąŠąĄąĮą░ ąĮą░ ą▓čŗą▓ąŠą┤

; ąĖčüčģąŠą┤ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī out_line =0

; čāą║ą░ąĘą░č鹥ą╗čī čüč鹥ą║ą░ čāčüą░čéąĮąŠą▓ą╗ąĄąĮ ąĮą░ RAMEND

; ą╝ą░čüčüąĖą▓ ą┤ą░ąĮąĮčŗčģ (bufout:bufout_size) ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ąĘą░ą│čĆčāąČąĄąĮ

; čäą╗ą░ą│ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ ą╝ą░čüčüąĖą▓ą░ ą┤ą░ąĮąĮčŗčģ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ

;

mass_trm:

push zh

push zl

push xh

push xl

push tmp1

push tmp0 ; čģčĆą░ąĮąĖą╝ čĆą░ą▒ąŠčćčāčÄ ąŠą▒ą╗ą░čüčéčī ą▓ čüč鹥ą║ąĄ

res_line:

ldi tmp0,4

ser tmp1

cbi port_out,out_line

res_time:

dec tmp1

brne res_time

dec tmp0

brne res_time ; =>50uS time out

ldi xh,high (bufout)

ldi xl,low (bufout) ; ąĘą░ą│čĆčāąĘą║ą░ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░ ą╝ą░čüčüąĖą▓ą░

; ą▓ čāą║ą░ąĘą░č鹥ą╗čī

ldi tmp1,bufout_size

ldwi z,slot0 ; ą░ą┤čĆąĄčü ąĮą░čćą░ą╗ą░ čéą░ą▒ą╗ąĖčåčŗ ą▓ čāą║ą░ąĘą░č鹥ą╗ąĄ

;----------

trasstt:

ld tmp0,x+ ; 2 čåąĖą║ą╗ą░

slot_0:

sbi port_out,out_line ; 2 čåąĖą║ą╗ą░ čĆąĄą░ą╗čīąĮąŠ ą┤ąŠ čāčüčéą░ąĮąŠą▓ą║ąĖ 3 čåąĖą║ą╗ą░

bst tmp0,7 ; 1 čåąĖą║ą╗

bld zl,4 ; 1 čåąĖą║ą╗

icall ; 3 čåąĖą║ą╗ą░ = 4 čåąĖą║ą╗ą░ ąŠčé out_line=1

;----------

slot_1:

sbi port_out,out_line

bst tmp0,6 ; 1 čåąĖą║ą╗

bld zl,4 ; 1 čåąĖą║ą╗

icall ; 3 čåąĖą║ą╗ą░

;----------

slot_2:

sbi port_out,out_line

bst tmp0,5 ; 1 čåąĖą║ą╗

bld zl,4 ; 1 čåąĖą║ą╗

icall ; 3 čåąĖą║ą╗ą░

;----------

slot_3:

sbi port_out,out_line

bst tmp0,4 ; 1 čåąĖą║ą╗

bld zl,4 ; 1 čåąĖą║ą╗

icall ; 3 čåąĖą║ą╗ą░

;----------

slot_4:

sbi port_out,out_line

bst tmp0,3 ; 1 čåąĖą║ą╗

bld zl,4 ; 1 čåąĖą║ą╗

icall ; 3 čåąĖą║ą╗ą░

;----------

slot_5:

sbi port_out,out_line

bst tmp0,2 ; 1 čåąĖą║ą╗

bld zl,4 ; 1 čåąĖą║ą╗

icall ; 3 čåąĖą║ą╗ą░

;----------

slot_6:

sbi port_out,out_line

bst tmp0,1 ; 1 čåąĖą║ą╗

bld zl,4 ; 1 čåąĖą║ą╗

icall ; 3 čåąĖą║ą╗ą░

;----------

slot_7:

sbi port_out,out_line

sbr zl,(1<<6) ; ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ čāą║ą░ąĘą░č鹥ą╗čÅ ą┐ąŠą┤ ąĘą░ą▓ąĄčĆčłą░čÄčēąĖą╣ čäčĆą░ą│ą╝ąĄąĮčé

; 1 čåąĖą║ą╗

bst tmp0,0 ; 1 čåąĖą║ą╗

bld zl,4 ; 1 čåąĖą║ą╗

ijmp ; 3 čåąĖą║ą╗ą░

;----------ąĄčüč鹥čüčéą▓ąĄąĮąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮą░ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ ą╝ą░čüčüąĖą▓ą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮčŗ.

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

ąÆčŗą▒ąĖčĆą░ąĄą╝ čüčģąĄą╝čā BMS ą┤ą╗čÅ ąĘą░čĆčÅą┤ą░ ą╗ąĖčéąĖą╣-ąČąĄą╗ąĄąĘąŠč乊čüčäą░čéąĮčŗčģ (LiFePO4) ą░ą║ą║čāą╝čāą╗čÅč鹊čĆąŠą▓

ą×ą▒čÅąĘą░č鹥ą╗čīąĮčŗą╝ čāčüą╗ąŠą▓ąĖąĄą╝ ą┤ąŠą╗ą│ąŠą╣ ąĖ čüčéą░ą▒ąĖą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ Li-FePO4-ą░ą║ą║čāą╝čāą╗čÅč鹊čĆąŠą▓, ą▓ č鹊ą╝ čćąĖčüą╗ąĄ ąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░ EVE Energy, čÅą▓ą╗čÅąĄčéčüčÅ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄ čüą┐ąĄčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗčģ BMS-ą╝ąĖą║čĆąŠčüčģąĄą╝. ąøąĖčéąĖą╣-ąČąĄą╗ąĄąĘąŠč乊čüčäą░čéąĮčŗąĄ ąÉąÜąæ ąŠčéą╗ąĖčćą░čÄčéčüčÅ čéą░ą║ąĖą╝ąĖ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ą╝ąĖ, ą║ą░ą║ ą▓čŗčüąŠą║ą░čÅ ą╝ąĮąŠą│ąŠą║čĆą░čéąĮąŠčüčéčī čåąĖą║ą╗ąŠą▓ ąĘą░čĆčÅą┤ą░-čĆą░ąĘčĆčÅą┤ą░, ą▒ąĄąĘąŠą┐ą░čüąĮąŠčüčéčī, ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą▒čŗčüčéčĆąŠą╣ ąĘą░čĆčÅą┤ą║ąĖ, čāčüč鹊ą╣čćąĖą▓ąŠčüčéčī ą║ ą▒čāč乥čĆąĮąŠą╝čā čĆąĄąČąĖą╝čā čĆą░ą▒ąŠčéčŗ ąĖ ą┐čĆąĖąĄą╝ą╗ąĄą╝ą░čÅ čüč鹊ąĖą╝ąŠčüčéčī. ąØąŠ ą┤ą╗čÅ čŹčéąĖčģ ąÉąÜąæ ąŠč湥ąĮčī ą▓ą░ąČąĄąĮ ą║ąŠąĮčéčĆąŠą╗čī ą┐čĆąŠčåąĄčüčüą░ ąĘą░čĆčÅą┤ą░ ąĖ čĆą░ąĘčĆčÅą┤ą░ ą┤ą╗čÅ ąĖąĘą▒ąĄą│ą░ąĮąĖčÅ ą▓ąŠąĘą┤ąĄą╣čüčéą▓ąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ ąĘą░čĆčÅą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ 100% ąĘą░čĆčÅą┤ą░. ąśąĮąČąĄąĮąĄčĆčŗ ąÜą×ą£ą¤ąŁąø ą┐ąŠą┤ą│ąŠč鹊ą▓ąĖą╗ąĖ čüą┐ąĖčüąŠą║ čéą░ą║ąĖčģ čĆąĄčłąĄąĮąĖą╣ ąŠčé čĆą░ąĘąĮčŗčģ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĄą╣.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ>>

|

|

|

|

|

|

trofim2

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪą▒ čÅąĮą▓ 13, 2018 10:41:37 |

|

ąÜą░čĆą╝ą░: 3

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 7

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé čüąĄąĮ 10, 2015 06:59:03

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 106

ą×čéą║čāą┤ą░: ąōčĆąŠą┤ąĮąŠ, BY

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

ąóą░ą║ąĖąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ ą┐čĆą░ą▓ąĖą╗čīąĮąĄąĄ ąĮą░ąĘčŗą▓ą░čéčī ąĮą░ąĮąŠčüąĄą║čāąĮą┤ąĮčŗą╝ąĖ.

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

|

|

|

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

ąØąŠą▓čŗą╣ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ EVE čüąĄčĆąĖąĖ PLM ą┤ą╗čÅ GSM-čéčĆąĄą║ąĄčĆąŠą▓, čĆą░ą▒ąŠčéą░čÄčēąĖčģ ą▓ ąČčæčüčéą║ąĖčģ čāčüą╗ąŠą▓ąĖčÅčģ (ą┤ąŠ -40┬░ąĪ)

ąÜąŠą╝ą┐ą░ąĮąĖčÅ EVE ą▓čŗą┐čāčüčéąĖą╗ą░ ąĮąŠą▓čŗą╣ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ čüąĄčĆąĖąĖ PLM, čüąŠč湥čéą░čÄčēąĖą╣ ą▓ čüąĄą▒ąĄ ą▓čŗčüąŠą║čāčÄ ą▒ąĄąĘąŠą┐ą░čüąĮąŠčüčéčī, ą┤ą╗ąĖč鹥ą╗čīąĮčŗą╣ čüčĆąŠą║ čüą╗čāąČą▒čŗ, čłąĖčĆąŠą║ąĖą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĮčŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĖ ą▓čŗčüąŠą║čāčÄ č鹊ą║ąŠąŠčéą┤ą░čćčā ą┤ą░ąČąĄ ą┐čĆąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ.

ąŁčéąĖ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆčŗ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąĘą░čĆčÅą┤ ą┐čĆąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ ąŠčé -40/-20┬░ąĪ (čüąĮąĖąČąĄąĮąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ č鹊ą║ą░), ą▒ąĄąĘąŠą┐ą░čüąĮčŗ (ąĮąĄ ą▓ąŠčüą┐ą╗ą░ą╝ąĄąĮčÅčÄčéčüčÅ ąĖ ąĮąĄ ą▓ąĘčĆčŗą▓ą░čÄčéčüčÅ) ą┐čĆąĖ ą╝ąĄčģą░ąĮąĖč湥čüą║ąŠą╝ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖąĖ (ą┐čĆąŠčéčŗą║ą░ąĮąĖąĄ ąĖ čüą┤ą░ą▓ą╗ąĖą▓ą░ąĮąĖąĄ), čāčüč鹊ą╣čćąĖą▓čŗ ą║ ą▓ąĖą▒čĆą░čåąĖąĖ. ą×ąĮąĖ ą╝ąŠą│čāčé ą┐čĆąĖą╝ąĄąĮčÅčéčīčüčÅ ą║ą░ą║ ą┤ą╗čÅ ą░ą▓č鹊čéčĆą░ąĮčüą┐ąŠčĆčéą░ (čéčĆąĄą║ąĄčĆčŗ, ą╝ą░čÅčćą║ąĖ, čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖčÅ), čéą░ą║ ąĖ ą┤ą╗čÅ ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░, IoT-čāčüčéčĆąŠą╣čüčéą▓.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ>>

|

|

|

|

|

|

strengerst

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčé čÅąĮą▓ 16, 2018 13:25:19 |

|

| ąÆčŗą╝ąŠą│ą░č鹥ą╗čī ą┐čĆąĖą┐ąŠčÅ |

|

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé čÅąĮą▓ 18, 2013 15:11:02

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 516

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

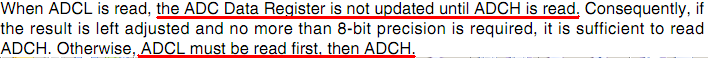

ą¤ąŠą┤čüą║ą░ąČąĖč鹥 ą┐čĆąĖą╝ąĄčĆąŠą╝ ą║ą░ą║ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ ąĘą░ą▒čĆą░čéčī ąĘąĮą░č湥ąĮąĖčÅ čü čĆąĄą│ąĖčüčéčĆąŠą▓ ADCH ąĖ ADCL ąĖ ą┐čĆąĖčüą▓ąŠąĖčéčī ą┐ąŠą╗čāč湥ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆčā R16. ą¤čĆąĖ čāčüą╗ąŠą▓ąĖąĖ čćč鹊 ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ ą┐ąŠ ą╗ąĄą▓ąŠą╝čā ą║čĆą░čÄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ ąĮą░čüčéčĆąŠą╣ą║ą░čģ.

ąØą░ ąĪąś ąĮą░čłąĄą╗ ą▓čĆąŠą┤ąĄ čéą░ą║ ą┤ąĄą╗ą░ąĄčéčüčÅ: v=(ADCL|ADCH<<8); ą░ ą║ą░ą║ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ.

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

|

|

|

|

|

Ivanoff-iv

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčé čÅąĮą▓ 16, 2018 13:37:18 |

|

| ąöčĆčāą│ ąÜąŠčéą░ |

|

ąÜą░čĆą╝ą░: 46

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 2030

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé ąĮąŠčÅ 11, 2016 05:48:09

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 6619

ą×čéą║čāą┤ą░: ąĪąĄčĆą┤čåąĄ ą¤ą░čĆą╝čŗ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą£ąĄą┤ą░ą╗ąĖ: 1

|

|

čéą░ą║ čéą░ą╝ v 16 ą▒ąĖčéąĮą░čÅ... ą░ čāč鹥ą▒čÅ R16 ą▓ąŠčüą╝ąĖą▒ąĖčéąĮčŗą╣, čéą░ą║ čćč鹊 ą▓čŗą▒ąĖčĆą░ą╣ ą║ą░ą║ąĖąĄ ą▒ąĖčéčŗ ADC č鹥ą▒ąĄ ąĮčāąČąĮčŗ, ąĄčüą╗ąĖ čüčéą░čĆčłąĖąĄ č鹊 čüąĮą░čćą░ą╗ą░ ą┐čĆąŠčćąĖčéą░ą╣ ą▓ ąĮąĄą│ąŠ ADCL, ą░ ą┐ąŠč鹊ą╝ ą▓ ąĮąĄą│ąŠ ąČąĄ ADCH (čüčéą░čĆąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĘą░čéčĆąĄčéčüčÅ ąĖ ąŠčüčéą░ąĮčāčéčüčÅ č鹊ą╗čīą║ąŠ čüčéą░čĆčłąĖąĄ 8 ą▒ąĖčé)

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ after 1 minute 42 seconds:

ąĮą░ ąĪ čćą░čüč鹊 ą┤ąĄą╗ą░ąĄčéčüčÅ v=ADC; ąŠčüčéą░ą╗čīąĮąŠąĄ čāąČąĄ čüą░ą╝ ą║ąŠą╝ą┐ąĖą╗čÅč鹊čĆ čĆą░ąĘą▒ąĄčĆčæčé.

_________________

ą¤čĆąŠčüč鹊 ąĮąĄ čāčćąĖ čäąĖąĘąĖą║čā ą▓ čłą║ąŠą╗ąĄ, ąĖ ą▓čüčÅ čéą▓ąŠčÅ ąČąĖąĘąĮčī ą▒čāą┤ąĄčé ąĮą░ą┐ąŠą╗ąĮąĄąĮą░ čćčāą┤ąĄčüą░ą╝ąĖ ąĖ ą▓ąŠą╗čłąĄą▒čüčéą▓ąŠą╝

ąæąĄąĘą│čĆą░ą╝ąŠčéąĮąŠ ą▓ąŠą┐čĆąŠčłą░čÄčēąĖą╝ ą┐čĆąŠ čüąĖą╗ąŠą▓čāčÄ ąĖą╗ąĖ ą▓čŗčüąŠą║ąŠą▓ąŠą╗čīčéąĮčāčÄ čŹą╗ąĄą║čéčĆąŠąĮąĖą║čā čÅ ąĮąĄ ąŠčéą▓ąĄčćą░čÄ, ą░ č鹊 ąĄčēčæ ą┐ąŠčüą░ą┤čÅčé ąĘą░ čāčćą░čüčéąĖąĄ ą▓ (čüą░ą╝ąŠ)čāą▒ąĖąĄąĮąĖąĖ ąŠą▒ąŠą╗čéčāčüą░...

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

|

|

|

|

|

dgrett

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčé čÅąĮą▓ 16, 2018 13:45:20 |

|

| ąÆčŗą╝ąŠą│ą░č鹥ą╗čī ą┐čĆąĖą┐ąŠčÅ |

ąÜą░čĆą╝ą░: -8

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 49

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčü ą┤ąĄą║ 28, 2014 21:54:05

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 615

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

ą» čćąĖčéą░čÄ čüčĆą░ąĘčā ADCH:

in temp,ADCH

ąś ą▓čüąĄ čłčāčĆčłąĖčé. ąóąŠą╗čīą║ąŠ čüą┐ąĄčĆą▓ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄ ADLAR

_________________

ą» ą▓čüčæ-ą▓čüčæ čāąĘąĮAčÄ ąĖ čüčéą░ąĮčā ą┐čĆąŠč乥čüčüąŠčĆąŠą╝.

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

|

|

|

|

|

Ivanoff-iv

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčé čÅąĮą▓ 16, 2018 13:50:29 |

|

| ąöčĆčāą│ ąÜąŠčéą░ |

|

ąÜą░čĆą╝ą░: 46

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 2030

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé ąĮąŠčÅ 11, 2016 05:48:09

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 6619

ą×čéą║čāą┤ą░: ąĪąĄčĆą┤čåąĄ ą¤ą░čĆą╝čŗ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą£ąĄą┤ą░ą╗ąĖ: 1

|

|

ą▓ąŠąĘą╝ąŠąČąĮąŠ, ą┐čĆąŠčüč鹊 ąĄčüčéčī čĆčÅą┤ 16ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ (čā čéą░ą╣ą╝ąĄčĆąŠą▓ č鹊čćąĮąŠ) ą┐čĆąĖ čćč鹥ąĮąĖąĖ (ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ) ąŠą┤ąĮąŠą│ąŠ ą▒ąĖčéą░ ą▓č鹊čĆąŠą╣ ą▒ą╗ąŠą║ąĖčĆčāąĄčéčüčÅ, čćč鹊ą▒čŗą┐čĆąŠčćąĖčéą░ąĮąŠ ą▒čŗą╗ąŠ ąĖą╝ąĄąĮąĮąŠ č鹊 čćč鹊 ą▒čŗą╗ąŠ ą▓ čĆąĄą│ąĖčüčéčĆąĄ (ą░ č鹊 ą┐ąŠą║ą░ čćąĖčéą░ą╗ ąŠą┤ąĖąĮ ą▒ąĖčé - čĆąĄą│ąĖčüčéčĆ ąĖąĘą╝ąĄąĮąĖą╗čüčÅ ąĖ ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐ąŠą╗čāčćąĖą╝ čģą▓ąŠčüčé ą┐ą░ą▓ą╗ąĖąĮąĖą╣, čĆąŠą│ą░ ąŠą╗ąĄąĮčīąĖ - ą▓ čüą╝čŗčüą╗ąĄ ąŠčé čüąŠą▓ąĄčĆčłąĄąĮąĮąŠ čĆą░ąĘąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣)

_________________

ą¤čĆąŠčüč鹊 ąĮąĄ čāčćąĖ čäąĖąĘąĖą║čā ą▓ čłą║ąŠą╗ąĄ, ąĖ ą▓čüčÅ čéą▓ąŠčÅ ąČąĖąĘąĮčī ą▒čāą┤ąĄčé ąĮą░ą┐ąŠą╗ąĮąĄąĮą░ čćčāą┤ąĄčüą░ą╝ąĖ ąĖ ą▓ąŠą╗čłąĄą▒čüčéą▓ąŠą╝

ąæąĄąĘą│čĆą░ą╝ąŠčéąĮąŠ ą▓ąŠą┐čĆąŠčłą░čÄčēąĖą╝ ą┐čĆąŠ čüąĖą╗ąŠą▓čāčÄ ąĖą╗ąĖ ą▓čŗčüąŠą║ąŠą▓ąŠą╗čīčéąĮčāčÄ čŹą╗ąĄą║čéčĆąŠąĮąĖą║čā čÅ ąĮąĄ ąŠčéą▓ąĄčćą░čÄ, ą░ č鹊 ąĄčēčæ ą┐ąŠčüą░ą┤čÅčé ąĘą░ čāčćą░čüčéąĖąĄ ą▓ (čüą░ą╝ąŠ)čāą▒ąĖąĄąĮąĖąĖ ąŠą▒ąŠą╗čéčāčüą░...

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

|

|

|

|

|

strengerst

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčé čÅąĮą▓ 16, 2018 13:52:43 |

|

| ąÆčŗą╝ąŠą│ą░č鹥ą╗čī ą┐čĆąĖą┐ąŠčÅ |

|

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé čÅąĮą▓ 18, 2013 15:11:02

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 516

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

ąĢčüą╗ąĖ čÅ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą┐ąŠąĮčÅą╗ č鹊 ą╝ąŠąČąĮąŠ ą┐čĆąŠčüčé čüčćąĖčéą░čéčī ADCH ą┐ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ADLAR. ą░ ADCL ą╝ąŠąČąĮąŠ ą▓ąŠąŠą▒čēąĄ ąĮąĄ čéčĆąŠą│ą░čéčī.

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

dgrett

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčé čÅąĮą▓ 16, 2018 13:55:51 |

|

| ąÆčŗą╝ąŠą│ą░č鹥ą╗čī ą┐čĆąĖą┐ąŠčÅ |

ąÜą░čĆą╝ą░: -8

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 49

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčü ą┤ąĄą║ 28, 2014 21:54:05

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 615

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

ąØčā čü čéą░ą╣ą╝ąĄčĆą░ą╝ąĖ ąĖ čé.ą┤. čÅ ąŠą▒čĆą░čēą░čÄčüčī ą┐ąŠ ąöą© ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ after 1 minute 58 seconds:ąĢčüą╗ąĖ čÅ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą┐ąŠąĮčÅą╗ č鹊 ą╝ąŠąČąĮąŠ ą┐čĆąŠčüčé čüčćąĖčéą░čéčī ADCH ą┐ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ADLAR. ą░ ADCL ą╝ąŠąČąĮąŠ ą▓ąŠąŠą▒čēąĄ ąĮąĄ čéčĆąŠą│ą░čéčī. ą» ąĖą╝ąĄąĮąĮąŠ čéą░ą║ ąĖ ą┤ąĄą╗ą░čÄ, ą│ąŠą▓ąŠčĆčÄ ąČąĄ, čłčāčĆčłąĖčé

_________________

ą» ą▓čüčæ-ą▓čüčæ čāąĘąĮAčÄ ąĖ čüčéą░ąĮčā ą┐čĆąŠč乥čüčüąŠčĆąŠą╝.

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

Ivanoff-iv

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčé čÅąĮą▓ 16, 2018 13:56:49 |

|

| ąöčĆčāą│ ąÜąŠčéą░ |

|

ąÜą░čĆą╝ą░: 46

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 2030

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé ąĮąŠčÅ 11, 2016 05:48:09

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 6619

ą×čéą║čāą┤ą░: ąĪąĄčĆą┤čåąĄ ą¤ą░čĆą╝čŗ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą£ąĄą┤ą░ą╗ąĖ: 1

|

ąĢčüą╗ąĖ čÅ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą┐ąŠąĮčÅą╗ č鹊 ą╝ąŠąČąĮąŠ ą┐čĆąŠčüčé čüčćąĖčéą░čéčī ADCH ą┐ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ADLAR. ą░ ADCL ą╝ąŠąČąĮąŠ ą▓ąŠąŠą▒čēąĄ ąĮąĄ čéčĆąŠą│ą░čéčī. čüą║ąŠčĆąĄąĄ ą▓čüąĄą│ąŠ ą┤ą░, ąĮčā ąĄčüą╗ąĖ ąĮąĄ ą▓ąĘą╗ąĄčéąĖčé - ąĘąĮą░ąĄčłčī ą║čāą┤ą░ ą║ąŠą┐ą░čéčī.

_________________

ą¤čĆąŠčüč鹊 ąĮąĄ čāčćąĖ čäąĖąĘąĖą║čā ą▓ čłą║ąŠą╗ąĄ, ąĖ ą▓čüčÅ čéą▓ąŠčÅ ąČąĖąĘąĮčī ą▒čāą┤ąĄčé ąĮą░ą┐ąŠą╗ąĮąĄąĮą░ čćčāą┤ąĄčüą░ą╝ąĖ ąĖ ą▓ąŠą╗čłąĄą▒čüčéą▓ąŠą╝

ąæąĄąĘą│čĆą░ą╝ąŠčéąĮąŠ ą▓ąŠą┐čĆąŠčłą░čÄčēąĖą╝ ą┐čĆąŠ čüąĖą╗ąŠą▓čāčÄ ąĖą╗ąĖ ą▓čŗčüąŠą║ąŠą▓ąŠą╗čīčéąĮčāčÄ čŹą╗ąĄą║čéčĆąŠąĮąĖą║čā čÅ ąĮąĄ ąŠčéą▓ąĄčćą░čÄ, ą░ č鹊 ąĄčēčæ ą┐ąŠčüą░ą┤čÅčé ąĘą░ čāčćą░čüčéąĖąĄ ą▓ (čüą░ą╝ąŠ)čāą▒ąĖąĄąĮąĖąĖ ąŠą▒ąŠą╗čéčāčüą░...

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

strengerst

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčé čÅąĮą▓ 16, 2018 14:01:26 |

|

| ąÆčŗą╝ąŠą│ą░č鹥ą╗čī ą┐čĆąĖą┐ąŠčÅ |

|

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé čÅąĮą▓ 18, 2013 15:11:02

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 516

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

ąĪą┐ą░čüąĖą▒ąŠ ą▒čāą┤čā ą┐čĆąŠą▒ąŠą▓ą░čéčī.

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

Alexeyslav

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪčĆ čÅąĮą▓ 17, 2018 00:17:05 |

|

ąÜą░čĆą╝ą░: 28

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 568

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé ą╝ą░ą╣ 05, 2011 21:26:34

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 4550

ą×čéą║čāą┤ą░: ąŻą║čĆą░ąĖąĮą░, ąĪą╗ą░ą▓čāčéąĖčć

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

ąĪ ąÉą”ą¤ čéą░ą║ąŠą╣ ą┐čĆąŠą▒ą╗ąĄą╝čŗ ąĮąĄčé, ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠ čćąĖčéą░ą╣ čĆąĄą│ąĖčüčéčĆčŗ. ą×ąĮ ąĮąĄ ą╝ąĄąĮčÅąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ čéą░ą║čé ąĖ ą┐ąŠčŹč鹊ą╝čā ąĮąĄčé ą┐čĆąŠą▒ą╗ąĄą╝čŗ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ ą┤ą▓čāčģ ą▒ą░ą╣čé. ą¤ąŠąČą░ą╗čāą╣, čü ąÉą”ą¤ ąĮą░ą┤ąŠ čüą┐ąĄčåąĖą░ą╗čīąĮąŠ čĆą░čüčüčéą░ą▓ąĖčéčī ąĖ ąĘą░čĆčÅą┤ąĖčéčī ą│čĆą░ą▒ą╗ąĖ čćč鹊ą▒čŗ ą┐čĆąŠčćąĖčéą░čéčī čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé ąŠčé ąŠą┤ąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ą░ ą╝ą╗ą░ą┤čłąĖą╣ ąŠčé ą┤čĆčāą│ąŠą╣.

ąóąĄą╝ą▒ąŠą╗ąĄąĄ ą║ąŠą│ą┤ą░ čüč鹊ąĖčé ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ ą┐ąŠ čüčéą░čĆčłąĄą╣ čüč鹊čĆąŠąĮąĄ ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ 8 ą▒ąĖčé.

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

Engineer_Keen

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪčĆ čÅąĮą▓ 17, 2018 07:37:53 |

|

| ąöčĆčāą│ ąÜąŠčéą░ |

|

ąÜą░čĆą╝ą░: 32

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 234

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé čÅąĮą▓ 29, 2010 10:27:40

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 3851

ą×čéą║čāą┤ą░: ą£ąŠčüą║ą▓ą░

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

ą¤čĆąŠčüč鹊 ąŠčüčéą░ą▓ą╗čÄ čŹč鹊 čéčāčé...

| ąÆą╗ąŠąČąĄąĮąĖčÅ: |

ADC_READ.png [13 KiB]

ADC_READ.png [13 KiB]

ąĪą║ą░čćąĖą▓ą░ąĮąĖą╣: 550

|

_________________

ąØąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠ čüąŠą▒čĆą░ąĮąĮą░čÅ ąĖąĘ ąĮąĄąĖčüą┐čĆą░ą▓ąĮčŗčģ ą┤ąĄčéą░ą╗ąĄą╣ čüčģąĄą╝ą░ ąĮčāąČą┤ą░ąĄčéčüčÅ ą▓ ąŠčéą╗ą░ą┤ą║ąĄ ąĖ čüčĆą░ąĘčā ąĮąĄ čĆą░ą▒ąŠčéą░ąĄčé... (ąĪ)

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

Ivanoff-iv

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪčĆ čÅąĮą▓ 17, 2018 08:37:12 |

|

| ąöčĆčāą│ ąÜąŠčéą░ |

|

ąÜą░čĆą╝ą░: 46

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 2030

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé ąĮąŠčÅ 11, 2016 05:48:09

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 6619

ą×čéą║čāą┤ą░: ąĪąĄčĆą┤čåąĄ ą¤ą░čĆą╝čŗ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą£ąĄą┤ą░ą╗ąĖ: 1

|

|

čé.ąĄ. ADCL ą▒ąĄąĘ ADCH čćąĖčéą░čéčī ąĮąĄą╗čīąĘčÅ, ą░ ąĮą░ąŠą▒ąŠčĆąŠčé ą╝ąŠąČąĮąŠ, ą┐ąŠąĮčÅčéąĮąŠ. (čÅ ą▓čüąĄą│ą┤ą░ čüčéą░čĆą░ą╗čüčÅ čćąĖčéą░čéčī ą▓čüčæ, čéą░ą║, ąĮą░ ą▓čüčÅą║ąĖą╣ čüą╗čāčćą░ą╣)

_________________

ą¤čĆąŠčüč鹊 ąĮąĄ čāčćąĖ čäąĖąĘąĖą║čā ą▓ čłą║ąŠą╗ąĄ, ąĖ ą▓čüčÅ čéą▓ąŠčÅ ąČąĖąĘąĮčī ą▒čāą┤ąĄčé ąĮą░ą┐ąŠą╗ąĮąĄąĮą░ čćčāą┤ąĄčüą░ą╝ąĖ ąĖ ą▓ąŠą╗čłąĄą▒čüčéą▓ąŠą╝

ąæąĄąĘą│čĆą░ą╝ąŠčéąĮąŠ ą▓ąŠą┐čĆąŠčłą░čÄčēąĖą╝ ą┐čĆąŠ čüąĖą╗ąŠą▓čāčÄ ąĖą╗ąĖ ą▓čŗčüąŠą║ąŠą▓ąŠą╗čīčéąĮčāčÄ čŹą╗ąĄą║čéčĆąŠąĮąĖą║čā čÅ ąĮąĄ ąŠčéą▓ąĄčćą░čÄ, ą░ č鹊 ąĄčēčæ ą┐ąŠčüą░ą┤čÅčé ąĘą░ čāčćą░čüčéąĖąĄ ą▓ (čüą░ą╝ąŠ)čāą▒ąĖąĄąĮąĖąĖ ąŠą▒ąŠą╗čéčāčüą░...

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

WiseLord

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪčĆ čÅąĮą▓ 17, 2018 09:58:04 |

|

| ąöčĆčāą│ ąÜąŠčéą░ |

|

ąÜą░čĆą╝ą░: 86

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 1018

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé ą░ą┐čĆ 11, 2013 11:19:59

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 4875

ą×čéą║čāą┤ą░: ą£ąĖąĮčüą║

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

ąÜčüčéą░čéąĖ, ąĄčüą╗ąĖ čĆąĄčćčī ąĖą┤čæčé ąŠą▒ avr-gcc, ąĄčüą╗ąĖ ąĮčāąČąĮą░ ą▓čüčÅ 10-ą▒ąĖčéąĮą░čÅ č鹊čćąĮąŠčüčéčī, č鹊 ąĄčüčéčī ąĄčēčæ čüą┐ąŠčüąŠą▒ - čćąĖčéą░čéčī čüčĆą░ąĘčā ADCW ą▓ 16-ą▒ąĖčéąĮčāčÄ ą┐ąĄčĆąĄą╝ąĄąĮąĮčāčÄ. ąĢčüą╗ąĖ ąČąĄ 8 ą▒ąĖčé ą┤ąŠčüčéą░č鹊čćąĮąŠ, č鹊 ą┤ą░, ą┐čĆąŠčēąĄ ą▓čüąĄą│ąŠ čćąĖčéą░čéčī ADCH, čü čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄą╝ čĆąĄąĘčāą╗čīčéą░čéą░ ą▓ą╗ąĄą▓ąŠ. ąÜąŠą┤: /* ADC */

#define ADCW _SFR_IO16(0x04)

#define ADCL _SFR_IO8(0x04)

#define ADCH _SFR_IO8(0x05)

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

strengerst

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪčĆ čÅąĮą▓ 17, 2018 11:51:03 |

|

| ąÆčŗą╝ąŠą│ą░č鹥ą╗čī ą┐čĆąĖą┐ąŠčÅ |

|

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé čÅąĮą▓ 18, 2013 15:11:02

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 516

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

ą¤ąŠą┤čüą║ą░ąČąĖč鹥 ą║ąŠą╝čā ąĮąĄ čéčĆčāą┤ąĮąŠ čćč鹊 ąĮąĄ čéą░ą║ ąĮą░ čüčģąĄą╝ąĄ ą▓ ą┐čĆąŠč鹥čāčüąĄ, čéą░ą║ ą║ą░ą║ ą┤ą▓ąĖą│ą░čÄ ą┐ąŠą╗ąĘčāąĮąŠą║ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ ąĖ ąĮąĄč湥ą│ąŠ ąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé. ąÆ ąĮą░čćą░ą╗čīąĮčŗą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą©ąĖą╝ čüąĖą│ąĮą░ą╗ ą▓čŗčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĄą│ąŠ čüą║ą▓ą░ąČąĮąŠčüčéčī, ąÉ ą┐ąŠč鹊ą╝ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čüą║ą▓ą░ąČąĮąŠčüčéąĖ ą┐ąŠčüč鹊čÅąĮąĮčŗ ąĖ ąĮą░ ą┐ąŠą╗ąĘčāąĮąŠą║ ąĮąĄ čĆąĄą░ą│ąĖčĆčāčÄčé? ąĪą┐ąŠą╣ą╗ąĄčƹܹŠą┤:

.include "tn13Adef.inc"; Header files

.list; // ą×č鹊ą▒čĆąŠąČąĄąĮąĖčÅ ą╗ąĖčüčéąĖąĮą│ą░ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą╝ą░ąĮą┤čŗ.

.cseg; čĆą░ą▒ąŠčéą░ąĄą╝ čü ą┐čĆąŠą│čĆą░ą╝ąĮąŠą╣ ą┐ą░ą╝čÅčéčīčÄ ą░ ąĮąĄ ąŠąĘčā ąĖą╗ąĖ eeprom

.org 0; čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄą╝ ąĮą░čćą░ą╗čīąĮčāčÄ ą┐ąŠąĘąĖčåąĖčÄ čüčéčĆąŠą║ąĖ

rjmp START; Reset Handler

rjmp START; IRQ0 Handler

rjmp START;; PCINT0Z Handler

rjmp START3; Timer0 Overflow Handler

rjmp START; EEPROM Ready Handler

rjmp START; Analog Comparator Handler

rjmp START; TIM0_COMPA CompareA Handler

rjmp START; Timer0 CompareB Handler

rjmp START; Watchdog Interrupt Handler

rjmp start3; ADC Conversion Handler

start3:

CLV;

//ąĪčćąĖčéčŗą▓ą░ąĄą╝ ą┤ą░ąĮąĮčŗąĄ ąÉą”ą¤

in R16, ADCL;

//ąŚą░ą┐ąĖčüčŗą▓ą░ąĄą╝ čüčćąĖčéą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ.

out OCR0A, R16;

reti;

START:

// ą║ąŠą╝ą░ąĮą┤ą░ ąĘą░ą┐čĆąĄčēą░ąĄčé ą│ą╗ąŠą▒ą░ą╗čīąĮčŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

CLI;

//ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ čüčé菹║ą░.(čāčüčéą░ąĮąŠą▓ą║ą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ čĆą░ąĘą╝ąĄčĆą░ ą×ąŚąŻ);

ldi R17, RAMEND;

out SPL, R17;

//ąÆčŗą▒ąĖčĆą░ąĄą╝ ą║ąŠčŹčäąĖčåąĖąĄąĮčé ą┐čĆąĄą┤ąĄą╗ąĖč鹥ą╗čÅ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ąÉą”ą¤ ą┐čĆąĖ čĆą░čüč湥č鹥 čćč鹊 čćą░čüč鹊čéą░ 9,6/8=1,2 ą£ą│čå; 1200/8=150; ą│ą┤ąĄ 8 ą▓čŗą▒čĆą░ąĮąĮčŗą╣ ą║ąŠčŹčäąĖčåąĖąĄąĮčé

//ąŚą░ą┐čĆąĄčēą░ąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ą║ąŠą╝ą┐ąŠčĆą░č鹊čĆą░ ADIE

LDI R16,(0<<ADPS2)|(1<<ADPS1)|(1<<ADPS0)|(0<<ADIE);

out ADCSRA, R16;

//ąÆą║ą╗čÄčćą░ąĄą╝ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠ-čåąĖčäčĆąŠą▓ąŠą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī

SBI ADCSRA, ADEN;

//ąĀąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ ą▓čŗčüčéą░ą▓ą╗čÅąĄą╝ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ

SBI ADCSRA, ADATE;

LDI R16,(0<<ADTS2)|(0<<ADTS1)|(0<<ADTS0);

out ADCSRB, R16;

//ąÆčŗą▒ąĖčĆą░ąĄą╝ ąĮąŠąČą║čā ą╝ą║ ą║ąŠč鹊čĆą░čÅ ą▒čāą┤ąĄčé ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčéčī ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ ADC1

LDI R16, (0<<MUX1)|(1<<MUX0);

out ADMUX, R16;

//ąöąĄą╗ą░ąĄą╝ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ ą┐ąŠ ą╗ąĄą▓ąŠą╝čā ą║čĆą░čÄ ą┤ą╗čÅ čüčćąĖčéčŗą▓ą░ąĮąĖčÅ ADCH.

SBI ADMUX, ADLAR;

//ąÆčŗą▒ąĖčĆą░ąĄą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ąĄčĆą░, čüčéą░ą▓ąĖą╝ ą┐ąĖčéą░ąĮąĖčÅ ąŠčé ąśą×ąØ.

SBI ADMUX, REFS0;

//ąŚą░ą┐čāčüą║ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ

SBI ADCSRA, ADSC;

//ą×čüčéą░ą▓ą╗čÅąĄą╝ čĆą░ą▒ąŠčéčā ąĮąŠąČą║ąĖ ą£ąÜ ą║ą░ą║ ąĮą░ ą▓čģąŠą┤ ą┤ą╗čÅ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░

CBI DDRB, DDB0;

CBI PORTB, PB0;

//ą¤ąŠą┤ą║ą╗čÄčćą░ąĄą╝ čéą░ą╣ą╝ąĄčĆ ą▓ čĆąĄąČąĖą╝ąĄ FAST PWM - čłąśą£ čüąĖą│ąĮą░ą╗ą░ čü čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą▓ąĄčĆčģąĮąĖą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ OCR0A

LDI R16, (1<<WGM01)|(1<<WGM00)|(1<<COM0A1)|(0<<COM0A0);

OUT TCCR0A,R16;

//ą×ą┐čĆąĄą┤ąĄą╗čÅąĄą╝ čüąŠčüč鹊čÅąĄąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ OCOA - ąĮąĄ ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĖą╣ čłąĖą╝ ą║ą░ą║ ąĮą░ ą▓čŗčģąŠą┤.

SBI DDRB, DDB0;

SBI PORTB, PB0;

/*ąĪą║ąŠčĆąŠčüčéčī čĆą░ą▒ąŠčéčŗ čéą░ą╣ą╝ąĄčĆą░ ą▓čŗą▒ąĖčĆą░ąĄą╝ ąĪąÜ/1024 - ą│ą┤ąĄ ąĪąÜ - čćą░čüč鹊čéą░ čĆą░ą▒ąŠčéčŗ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ąĄčĆą░

ą▓ ąĮą░čłąĄą╝ čüą╗čāčćą░ąĖ ą╝čŗ ą▓čŗčüčéą░ą▓ą╗čÅąĄą╝ ą▓ąŠ fuces clkdiv8 čćč鹊 ąŠą▒ąĄčüą┐ąĄčćąĖčé ąĮą░ą╝ čćą░čüč鹊čéčā 9,6ą£hz/8=1,2Mhz ąĘąĮą░čćąĖčé

čüą║ąŠčĆąŠčüčéčī čĆą░ą▒ąŠčéčŗ čéą░ą╣ą╝ąĄčĆą░ ą▒čāą┤ąĄčé 1,2Mhz/1024=1,17Khz čćč鹊 čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčé čüč湥čé ąĘąĮą░č湥ąĮąĖčÅ. ą¦ąĄą╝ ą╝ąĄąĮčīčłąĄ

čćą░čüč鹊čéą░ č鹥ą╝ ą▒ąŠą╗čīčłąĄąĄ ą▓čĆąĄą╝čÅ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ*/

ldi R16, (1<<CS02)|(0<<CS01)|(1<<CS00)|(0<<WGM02);

out TCCR0B, R16;

//ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░

ldi R16, (1<<TOIE0);

out TIMSK0, R16;

//ąĪą║ą▓ą░ąČąĮąŠčüčéčī čłąĖą╝ čüąĖą│ąĮą░ą╗ą░.

ldi R16, 0x50;

out OCR0A, R16;

sei;

rjmp START1;

START1:

nop;

rjmp START1;

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

Ivanoff-iv

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąÉčüčüąĄą╝ą▒ą╗ąĄčĆ (ASM) ą┤ą╗čÅ AVR ą▓ ą▓ąŠą┐čĆąŠčüą░čģ ąĖ ąŠčéą▓ąĄčéą░čģ  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪčĆ čÅąĮą▓ 17, 2018 12:37:06 |

|

| ąöčĆčāą│ ąÜąŠčéą░ |

|

ąÜą░čĆą╝ą░: 46

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 2030

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé ąĮąŠčÅ 11, 2016 05:48:09

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 6619

ą×čéą║čāą┤ą░: ąĪąĄčĆą┤čåąĄ ą¤ą░čĆą╝čŗ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą£ąĄą┤ą░ą╗ąĖ: 1

|

...ąĮčā ąĄčüą╗ąĖ ąĮąĄ ą▓ąĘą╗ąĄčéąĖčé - ąĘąĮą░ąĄčłčī ą║čāą┤ą░ ą║ąŠą┐ą░čéčī. (ą┐ąŠą┤čüą║ą░ąĘą║ą░) ą┐čÅčéčīčÄ ą┐ąŠčüčéą░ą╝ąĖ ą▓čŗčłąĄ čüčüčŗą╗ą║ą░ ąĘą░ čüč鹥ąĮą║čā čüąŠ čüčéčĆąĄą╗čÅčÄčēąĖą╝ąĖ ą│čĆą░ą▒ą╗čÅą╝ąĖ  čŹč鹊 čéą▓ąŠą╣ čüą╗čāčćą░ą╣

_________________

ą¤čĆąŠčüč鹊 ąĮąĄ čāčćąĖ čäąĖąĘąĖą║čā ą▓ čłą║ąŠą╗ąĄ, ąĖ ą▓čüčÅ čéą▓ąŠčÅ ąČąĖąĘąĮčī ą▒čāą┤ąĄčé ąĮą░ą┐ąŠą╗ąĮąĄąĮą░ čćčāą┤ąĄčüą░ą╝ąĖ ąĖ ą▓ąŠą╗čłąĄą▒čüčéą▓ąŠą╝

ąæąĄąĘą│čĆą░ą╝ąŠčéąĮąŠ ą▓ąŠą┐čĆąŠčłą░čÄčēąĖą╝ ą┐čĆąŠ čüąĖą╗ąŠą▓čāčÄ ąĖą╗ąĖ ą▓čŗčüąŠą║ąŠą▓ąŠą╗čīčéąĮčāčÄ čŹą╗ąĄą║čéčĆąŠąĮąĖą║čā čÅ ąĮąĄ ąŠčéą▓ąĄčćą░čÄ, ą░ č鹊 ąĄčēčæ ą┐ąŠčüą░ą┤čÅčé ąĘą░ čāčćą░čüčéąĖąĄ ą▓ (čüą░ą╝ąŠ)čāą▒ąĖąĄąĮąĖąĖ ąŠą▒ąŠą╗čéčāčüą░...

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĪčéčĆą░ąĮąĖčåą░ 316 ąĖąĘ 380

|

[ ąĪąŠąŠą▒čēąĄąĮąĖą╣: 7597 ] |

... , , , , , , ... |

ąÜč鹊 čüąĄą╣čćą░čü ąĮą░ č乊čĆčāą╝ąĄ |

ąĪąĄą╣čćą░čü čŹč鹊čé č乊čĆčāą╝ ą┐čĆąŠčüą╝ą░čéčĆąĖą▓ą░čÄčé: Martian, veso74 ąĖ ą│ąŠčüčéąĖ: 45 |

|

ąÆčŗ ąĮąĄ ą╝ąŠąČąĄč鹥 ąĮą░čćąĖąĮą░čéčī č鹥ą╝čŗ

ąÆčŗ ąĮąĄ ą╝ąŠąČąĄč鹥 ąŠčéą▓ąĄčćą░čéčī ąĮą░ čüąŠąŠą▒čēąĄąĮąĖčÅ

ąÆčŗ ąĮąĄ ą╝ąŠąČąĄč鹥 čĆąĄą┤ą░ą║čéąĖčĆąŠą▓ą░čéčī čüą▓ąŠąĖ čüąŠąŠą▒čēąĄąĮąĖčÅ

ąÆčŗ ąĮąĄ ą╝ąŠąČąĄč鹥 čāą┤ą░ą╗čÅčéčī čüą▓ąŠąĖ čüąŠąŠą▒čēąĄąĮąĖčÅ

ąÆčŗ ąĮąĄ ą╝ąŠąČąĄč鹥 ą┤ąŠą▒ą░ą▓ą╗čÅčéčī ą▓ą╗ąŠąČąĄąĮąĖčÅ

|

|

|