|

ążąŠčĆčāą╝ ąĀą░ą┤ąĖąŠąÜąŠčé • ą¤čĆąŠčüą╝ąŠčéčĆ č鹥ą╝čŗ - Xilinx ISE 11....ą║ą░ą║?

ąĪąŠąŠą▒čēąĄąĮąĖčÅ ą▒ąĄąĘ ąŠčéą▓ąĄč鹊ą▓ | ąÉą║čéąĖą▓ąĮčŗąĄ č鹥ą╝čŗ

|

ąĪčéčĆą░ąĮąĖčåą░ 7 ąĖąĘ 8

|

[ ąĪąŠąŠą▒čēąĄąĮąĖą╣: 157 ] |

... , , , , |

| ąÉą▓č鹊čĆ |

ąĪąŠąŠą▒čēąĄąĮąĖąĄ |

Nobodevi4

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ:  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą╝ą░čĆ 11, 2010 15:43:43 |

|

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪą▒ ą╝ą░čĆ 06, 2010 18:35:33

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 7

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

ąÉ ą║ą░ą║ ąĮą░čüč湥čé Core-Generator??? ą×ąĮ ą▓čĆąŠą┤ąĄ ą┤ąŠą╗ąČąĄąĮ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čüąĖąĮčāčü???

D:\Xilinx\10.1\ISE\bin\nt\wincoregen.exe

File->New Project, ąĮą░ąĘą▓ą░ą╗ ą┐čĆąŠąĄą║čé SIN, ą┤ą░ą╗ąĄąĄ ą▓čŗą╗ąĄąĘą░ąĄčé ąŠą║ąĮąŠ čü ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄą╝čŗą╝ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ąĖ. ąØą░ ą▓ą║ą╗ą░ą┤ą║ąĄ Part (čéąĖą┐ą░ Family, Device, Package, Speed Grade) ąĮčā čÅ ąĖčģ ąĘą░ą┐ąŠą╗ąĮčÅčÄ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ: Spartan2, xc2s100, tq144, -6. ąÉ ąĘą░č湥ą╝ ąĮčāąČąĮčŗ ąĄčēąĄ 2 ą▓ą║ą╗ą░ą┤ą║ąĖ: Generation ąĖ Advanced?

ąöą░ą╗ąĄąĄ ą▓čŗą╗ąĄąĘą░ąĄčé ąŠą║ąĮąŠ Sine-Cosine Look-Up Table, ą▓ čüą░ą╝ąŠą╣ ą┐ąĄčĆą▓ąŠą╣ ą▓ą║ą╗ą░ą┤ą║ąĄ ąĄčüčéčī ą┐ą░čĆą░ą╝ąĄčéčĆčŗ Output Width ąĖ Theta Input Widhth ąĖ ąĄčēąĄ ą┐ąŠą╗ąĄ Memory ROM - čŹč鹊 ą▓čüąĄ ąĘą░č湥ą╝? ąś ą║ą░ą║ ą╝ąĮąĄ ą┐ąŠčüą╝ąŠčéčĆąĄčéčī čćč鹊 čŹčéą░ ą║čĆąĖą▓ą░čÅ ą▓ ąĖč鹊ą│ąĄ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠ čüąĖąĮčāčü?

ąÆčüąĄą╝ ąĘą░čĆą░ąĮąĄąĄ čüą┐ą░čüąĖą▒ąŠ!

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

|

|

|

|

|

ąÉąĮą┤čĆčÄčłą║ą░

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ:  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą╝ą░čĆ 11, 2010 18:09:48 |

|

| ąØą░čłąĄą╗ čéčĆą░ąĮąĘąĖčüč鹊čĆ. ą¤ąŠąĮčÄčģą░ą╗. |

|

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤ąĮ čÅąĮą▓ 04, 2010 02:19:25

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 152

ą×čéą║čāą┤ą░: čģąĘ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

ąØą░čłąĄą╗ ą┐čĆąŠ ą╝ąĄą░ąĮą┤čĆ

Spartan3E ą┐ąĖčüą░ą╗(ą░): ąĪąŠą┐čĆąŠčé ą┐ąŠ čüąĖą│ąĮą░ą╗čā ą┐ąŠčüą╗ąĄ ąĄą╝ą║ąŠčüčéčī ąĮą░ ąĘąĄą╝ą╗čÄ. ąÆąŠčé ą▓ą░ą╝ ąĖ čüąĖąĮčāčü ąĖąĘ ą╝ąĄą░ąĮą┤čĆą░. Spartan3E čüą▒ąĖą╗ ą╝ąĄąĮčÅ čü č鹊ą╗ą║čā.  uldemir ą┐ąĖčüą░ą╗(ą░): ąÆ ISE čéčāą╗ą▒ą░čĆąĄ ąČą╝ąĄč鹥 ą║ąĮąŠą┐ąŠčćą║čā ą▓ ą▓ąĖą┤ąĄ ą╗ą░ą╝ą┐ąŠčćą║ąĖ ąĖą╗ąĖ Edit -> Language templates ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ą┐čĆąĖą╝ąĄčĆčŗ ą┤ą╗čÅ ą╝ąĮąŠą│ąĖčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓. ąÆąŠčé ROM ąÜąŠą┤: ................................... ąŁč鹊 ąŠąĮąŠ? ąóą░ą╝ ą┐čĆąŠčüč鹊 ąĘą░ą┐ąŠą╗ąĮąĄąĮąŠ ą┐ąŠ ą▓ąŠąĘčĆą░čüčéą░čÄčēąĄą╣: 1, 2, 3, 4...16.

Nobodevi4 , ą║ čüąŠąČą░ą╗ąĄąĮąĖčÄ ą▓ ą▒ą╗ąĖąČą░ą╣čłąĄąĄ ą▓čĆąĄą╝čÅ ąĮąĄ ą╝ąŠą│čā ą┐ąŠčüą╝ąŠčéčĆąĄčéčī, čüąĄą╣čćą░čü Xilinx čāą┤ą░ą╗ąĖą╗ ąĘą░ ąĮąĄąĮą░ą┤ąŠą▒ąĮąŠčüčéčīčÄ, ą░ č鹊 ąĮą░ ą▓ąĖąĮč鹥 ą╝ąĄčüčéą░ ąĮąĄčé.

_________________

ą×ą┐čŗčé čĆą░čüč鹥čé ą┐čĆčÅą╝ąŠ ą┐čĆąŠą┐ąŠčĆčåąĖąŠąĮą░ą╗čīąĮąŠ ą▓čŗą▓ąĄą┤ąĄąĮąĮąŠą╝čā ąĖąĘ čüčéčĆąŠčÅ ąŠą▒ąŠčĆčāą┤ąŠą▓ą░ąĮąĖčÄ.

______________

Jedem das Seine

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

|

|

|

|

|

Spartan3E

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ:  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą╝ą░čĆ 11, 2010 21:14:10 |

|

| ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā! |

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé ą┤ąĄą║ 24, 2009 23:50:46

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 34

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

ąÉąĮą┤čĆčÄčłą║ą░ ą┐ąĖčüą░ą╗(ą░): ąØą░čłąĄą╗ ą┐čĆąŠ ą╝ąĄą░ąĮą┤čĆ Spartan3E ą┐ąĖčüą░ą╗(ą░): ąĪąŠą┐čĆąŠčé ą┐ąŠ čüąĖą│ąĮą░ą╗čā ą┐ąŠčüą╗ąĄ ąĄą╝ą║ąŠčüčéčī ąĮą░ ąĘąĄą╝ą╗čÄ. ąÆąŠčé ą▓ą░ą╝ ąĖ čüąĖąĮčāčü ąĖąĘ ą╝ąĄą░ąĮą┤čĆą░. Spartan3E čüą▒ąĖą╗ ą╝ąĄąĮčÅ čü č鹊ą╗ą║čā.  uldemir ą┐ąĖčüą░ą╗(ą░): ąÆ ISE čéčāą╗ą▒ą░čĆąĄ ąČą╝ąĄč鹥 ą║ąĮąŠą┐ąŠčćą║čā ą▓ ą▓ąĖą┤ąĄ ą╗ą░ą╝ą┐ąŠčćą║ąĖ ąĖą╗ąĖ Edit -> Language templates ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ą┐čĆąĖą╝ąĄčĆčŗ ą┤ą╗čÅ ą╝ąĮąŠą│ąĖčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓. ąÆąŠčé ROM ąÜąŠą┤: ................................... ąŁč鹊 ąŠąĮąŠ? ąóą░ą╝ ą┐čĆąŠčüč鹊 ąĘą░ą┐ąŠą╗ąĮąĄąĮąŠ ą┐ąŠ ą▓ąŠąĘčĆą░čüčéą░čÄčēąĄą╣: 1, 2, 3, 4...16. Nobodevi4 , ą║ čüąŠąČą░ą╗ąĄąĮąĖčÄ ą▓ ą▒ą╗ąĖąČą░ą╣čłąĄąĄ ą▓čĆąĄą╝čÅ ąĮąĄ ą╝ąŠą│čā ą┐ąŠčüą╝ąŠčéčĆąĄčéčī, čüąĄą╣čćą░čü Xilinx čāą┤ą░ą╗ąĖą╗ ąĘą░ ąĮąĄąĮą░ą┤ąŠą▒ąĮąŠčüčéčīčÄ, ą░ č鹊 ąĮą░ ą▓ąĖąĮč鹥 ą╝ąĄčüčéą░ ąĮąĄčé. ąæčŗą╗ ą▓ąŠą┐čĆąŠčü -

"ąØą░čĆąŠą┤, ą║č鹊-ąĮąĖą▒čāą┤ą▒ ąĘąĮą░ąĄčé, ą║ą░ą║ čüą┤ąĄą╗ą░čéčī ąŠą▒čŗą║ąĮąŠą▓ąĄąĮąĮčŗą╣ čüąĖąĮčāčü ą▓ ISE WebPack 10.1 ąĮą░ Spartan2 ąĖ XC2S100???"

ą» ą┐čĆąĄą┤ą╗ąŠąČąĖą╗ čüą░ą╝čŗą╣ ą┐čĆąŠčüč鹊ą╣ ą▓ą░čĆąĖą░ąĮčé čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ąŠą┤ąĮąŠą╣ ąĮąŠą│ąĖ ą┐ą╗ąĖčüą║ąĖ  . ą¤ąŠąĮčÅčéąĮąŠ, čćč鹊 čüąĖąĮčāčü ąĮąĄ ąĖą┤ąĄą░ą╗čīąĮčŗą╣ ą▒čāą┤ąĄčé, ąĮąŠ čĆąĄčćčī ą▓ąŠčüą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčéčüčÅ ą┐čĆąĄą║čĆą░čüąĮąŠ. ąöą╗čÅ "ą║čĆą░čüąĖą▓ąŠą│ąŠ" čüąĖąĮčāčüą░, ą║ą░ą║ ą▓ą┐čĆąŠč湥ą╝ ąĖ ą┤ą╗čÅ ą╗čÄą▒ąŠą╣ ą┤čĆčāą│ąŠą╣ ąĘą░ą┤ą░ąĮąĮąŠą╣ č乊čĆą╝čŗ čüąĖą│ąĮą░ą╗ą░, čüą░ą╝ąŠ čüąŠą▒ąŠą╣ - ą”ąÉą¤ ą╗ąĄą┐ąĖčéčī. ąöą╗čÅ čüąĖąĮčāčüą░ ą╝ąŠąČąĮąŠ ąŠą▒ąŠą╣čéąĖčüčī ąĖ ą▒ąĄąĘ čéą░ą▒ą╗ąĖčćąĮąŠą│ąŠ ą╝ąĄč鹊ą┤ą░. ąÉ ą┐čĆąŠčēąĄ ą▓čüąĄą│ąŠ ą┐ąĖą╗čā ą┤ąĄą╗ą░čéčī.

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

|

|

|

|

|

ąÉąĮą┤čĆčÄčłą║ą░

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ:  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą╝ą░čĆ 11, 2010 22:27:39 |

|

| ąØą░čłąĄą╗ čéčĆą░ąĮąĘąĖčüč鹊čĆ. ą¤ąŠąĮčÄčģą░ą╗. |

|

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤ąĮ čÅąĮą▓ 04, 2010 02:19:25

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 152

ą×čéą║čāą┤ą░: čģąĘ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

ą¤ąĖą╗čā č鹊 ą┤ą░, ą┐čĆąŠčüč鹊 čüč湥čéčćąĖą║ąŠą╝ čüčćąĖčéą░čéčī ą▓ "+", ą┐ąŠč鹊ą╝ ą▓ "-".

_________________

ą×ą┐čŗčé čĆą░čüč鹥čé ą┐čĆčÅą╝ąŠ ą┐čĆąŠą┐ąŠčĆčåąĖąŠąĮą░ą╗čīąĮąŠ ą▓čŗą▓ąĄą┤ąĄąĮąĮąŠą╝čā ąĖąĘ čüčéčĆąŠčÅ ąŠą▒ąŠčĆčāą┤ąŠą▓ą░ąĮąĖčÄ.

______________

Jedem das Seine

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

ąÆčŗą▒ąĖčĆą░ąĄą╝ čüčģąĄą╝čā BMS ą┤ą╗čÅ ąĘą░čĆčÅą┤ą░ ą╗ąĖčéąĖą╣-ąČąĄą╗ąĄąĘąŠč乊čüčäą░čéąĮčŗčģ (LiFePO4) ą░ą║ą║čāą╝čāą╗čÅč鹊čĆąŠą▓

ą×ą▒čÅąĘą░č鹥ą╗čīąĮčŗą╝ čāčüą╗ąŠą▓ąĖąĄą╝ ą┤ąŠą╗ą│ąŠą╣ ąĖ čüčéą░ą▒ąĖą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ Li-FePO4-ą░ą║ą║čāą╝čāą╗čÅč鹊čĆąŠą▓, ą▓ č鹊ą╝ čćąĖčüą╗ąĄ ąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░ EVE Energy, čÅą▓ą╗čÅąĄčéčüčÅ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄ čüą┐ąĄčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗčģ BMS-ą╝ąĖą║čĆąŠčüčģąĄą╝. ąøąĖčéąĖą╣-ąČąĄą╗ąĄąĘąŠč乊čüčäą░čéąĮčŗąĄ ąÉąÜąæ ąŠčéą╗ąĖčćą░čÄčéčüčÅ čéą░ą║ąĖą╝ąĖ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ą╝ąĖ, ą║ą░ą║ ą▓čŗčüąŠą║ą░čÅ ą╝ąĮąŠą│ąŠą║čĆą░čéąĮąŠčüčéčī čåąĖą║ą╗ąŠą▓ ąĘą░čĆčÅą┤ą░-čĆą░ąĘčĆčÅą┤ą░, ą▒ąĄąĘąŠą┐ą░čüąĮąŠčüčéčī, ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą▒čŗčüčéčĆąŠą╣ ąĘą░čĆčÅą┤ą║ąĖ, čāčüč鹊ą╣čćąĖą▓ąŠčüčéčī ą║ ą▒čāč乥čĆąĮąŠą╝čā čĆąĄąČąĖą╝čā čĆą░ą▒ąŠčéčŗ ąĖ ą┐čĆąĖąĄą╝ą╗ąĄą╝ą░čÅ čüč鹊ąĖą╝ąŠčüčéčī. ąØąŠ ą┤ą╗čÅ čŹčéąĖčģ ąÉąÜąæ ąŠč湥ąĮčī ą▓ą░ąČąĄąĮ ą║ąŠąĮčéčĆąŠą╗čī ą┐čĆąŠčåąĄčüčüą░ ąĘą░čĆčÅą┤ą░ ąĖ čĆą░ąĘčĆčÅą┤ą░ ą┤ą╗čÅ ąĖąĘą▒ąĄą│ą░ąĮąĖčÅ ą▓ąŠąĘą┤ąĄą╣čüčéą▓ąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ ąĘą░čĆčÅą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ 100% ąĘą░čĆčÅą┤ą░. ąśąĮąČąĄąĮąĄčĆčŗ ąÜą×ą£ą¤ąŁąø ą┐ąŠą┤ą│ąŠč鹊ą▓ąĖą╗ąĖ čüą┐ąĖčüąŠą║ čéą░ą║ąĖčģ čĆąĄčłąĄąĮąĖą╣ ąŠčé čĆą░ąĘąĮčŗčģ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĄą╣.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ>>

|

|

|

|

|

|

Spartan3E

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ:  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ą╝ą░čĆ 12, 2010 06:22:14 |

|

| ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā! |

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé ą┤ąĄą║ 24, 2009 23:50:46

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 34

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

ąÉąĮą┤čĆčÄčłą║ą░ ą┐ąĖčüą░ą╗(ą░): ą¤ąĖą╗čā č鹊 ą┤ą░, ą┐čĆąŠčüč鹊 čüč湥čéčćąĖą║ąŠą╝ čüčćąĖčéą░čéčī ą▓ "+", ą┐ąŠč鹊ą╝ ą▓ "-".

ą¤ąĖą╗ą░ ą┤ąĄą╗ą░ąĄčéčüčÅ ą║ąŠą╗čīčåąĄą▓čŗą╝ čüč湥čéčćąĖą║ąŠą╝ ą▓ + ą┐ąŠč鹊ą╝ ą▓ ą╝ą░ą║čüąĖą╝čāą╝ąĄ 0 ąĖ ą┐ąŠ ą║čĆčāą│čā.

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

|

|

|

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

ąØąŠą▓čŗą╣ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ EVE čüąĄčĆąĖąĖ PLM ą┤ą╗čÅ GSM-čéčĆąĄą║ąĄčĆąŠą▓, čĆą░ą▒ąŠčéą░čÄčēąĖčģ ą▓ ąČčæčüčéą║ąĖčģ čāčüą╗ąŠą▓ąĖčÅčģ (ą┤ąŠ -40┬░ąĪ)

ąÜąŠą╝ą┐ą░ąĮąĖčÅ EVE ą▓čŗą┐čāčüčéąĖą╗ą░ ąĮąŠą▓čŗą╣ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ čüąĄčĆąĖąĖ PLM, čüąŠč湥čéą░čÄčēąĖą╣ ą▓ čüąĄą▒ąĄ ą▓čŗčüąŠą║čāčÄ ą▒ąĄąĘąŠą┐ą░čüąĮąŠčüčéčī, ą┤ą╗ąĖč鹥ą╗čīąĮčŗą╣ čüčĆąŠą║ čüą╗čāąČą▒čŗ, čłąĖčĆąŠą║ąĖą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĮčŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĖ ą▓čŗčüąŠą║čāčÄ č鹊ą║ąŠąŠčéą┤ą░čćčā ą┤ą░ąČąĄ ą┐čĆąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ.

ąŁčéąĖ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆčŗ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąĘą░čĆčÅą┤ ą┐čĆąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ ąŠčé -40/-20┬░ąĪ (čüąĮąĖąČąĄąĮąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ č鹊ą║ą░), ą▒ąĄąĘąŠą┐ą░čüąĮčŗ (ąĮąĄ ą▓ąŠčüą┐ą╗ą░ą╝ąĄąĮčÅčÄčéčüčÅ ąĖ ąĮąĄ ą▓ąĘčĆčŗą▓ą░čÄčéčüčÅ) ą┐čĆąĖ ą╝ąĄčģą░ąĮąĖč湥čüą║ąŠą╝ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖąĖ (ą┐čĆąŠčéčŗą║ą░ąĮąĖąĄ ąĖ čüą┤ą░ą▓ą╗ąĖą▓ą░ąĮąĖąĄ), čāčüč鹊ą╣čćąĖą▓čŗ ą║ ą▓ąĖą▒čĆą░čåąĖąĖ. ą×ąĮąĖ ą╝ąŠą│čāčé ą┐čĆąĖą╝ąĄąĮčÅčéčīčüčÅ ą║ą░ą║ ą┤ą╗čÅ ą░ą▓č鹊čéčĆą░ąĮčüą┐ąŠčĆčéą░ (čéčĆąĄą║ąĄčĆčŗ, ą╝ą░čÅčćą║ąĖ, čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖčÅ), čéą░ą║ ąĖ ą┤ą╗čÅ ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░, IoT-čāčüčéčĆąŠą╣čüčéą▓.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ>>

|

|

|

|

|

|

Nobodevi4

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ:  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ą╝ą░čĆ 12, 2010 14:27:54 |

|

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪą▒ ą╝ą░čĆ 06, 2010 18:35:33

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 7

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

ąŠą║, čüą┐čü ąĘą░ ą┐čĆąĖą╝ąĄčĆčŗ, ą░ ą╝ąŠą│čā čÅ čüą┤ąĄą╗ą░čéčī čüąĖąĮčāčü, ąĖčüą┐ąŠą╗čīąĘčāčÅ, ą║ ą┐čĆąĖą╝ąĄčĆčā, ąŠą▒čŗą║ąĮąŠą▓ąĄąĮąĮčŗą╣ čüč湥čéčćąĖą║ ąĖ ą▒ą╗ąŠą║ ą┐ą░ą╝čÅčéąĖ?

ąØčā, č鹊 ąĄčüčéčī, ąĮą░ čüč湥čéčćąĖą║ ą▒čāą┤ąĄčé ą┐ąŠą┤ą░ą▓ą░čéčīčüčÅ ą║ą░ą║ąŠą╣-ąĮąĖčéčī ą╝ąĄą░ąĮą┤čĆ ąĖ ą░ą┤čĆąĄčüą░ ą▒čāą┤čāčé ą┐ąĄčĆąĄą▒ąĖčĆą░čéčīčüčÅ, ą░ ą▓ ą┐ą░ą╝čÅčéčī ąĘą░ą│ąĮą░čéčī čāąČąĄ ą│ąŠč鹊ą▓čāčÄ čéą░ą▒ą╗ąĖčåčā ąĘąĮą░č湥ąĮąĖą╣ čüąĖąĮčāčüą░????

ąóąŠ ąĄčüčéčī, ą┤ą░ąĮąĮčŗąĄ čā ą╝ąĄąĮčÅ - čŹč鹊 ą▒čāą┤ąĄčé čäčāąĮą║čåąĖčÅ, ą░ ą░ą┤čĆąĄčü - čŹč鹊 ą▒čāą┤ąĄčé ą░čĆą│čāą╝ąĄąĮčé (čāą│ąŠą╗).

???

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

|

|

|

|

|

SII

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ:  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ą╝ą░čĆ 12, 2010 16:40:00 |

|

| ąÆčŗą╝ąŠą│ą░č鹥ą╗čī ą┐čĆąĖą┐ąŠčÅ |

ąÜą░čĆą╝ą░: 4

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 40

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé čÅąĮą▓ 30, 2009 14:50:35

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 625

ą×čéą║čāą┤ą░: ąĪąŠą╗ąĮąĄčćąĮąŠą│ąŠčĆčüą║

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

ąØčā čéą░ą║, čüąŠą▒čüčéą▓ąĄąĮąĮąŠ, čéą░ą║ ąĖ ą┤ąĄą╗ą░čÄčé, ą║ąŠą│ą┤ą░ ą┐čĆąĖą╝ąĄąĮčÅčÄčé ą▓ąĮąĄčłąĮąĖą╣ ą”ąÉą¤. ąöąŠą╗ąČąĄąĮ ąČąĄ ą║č鹊-č鹊 ą▓čŗą┤ą░ą▓ą░čéčī "čåąĖčäčĆčā" ąĮą░ ą▓čŗčģąŠą┤čŗ ą¤ąøąśąĪ, ąĖ ą┐čĆąŠčēąĄ ą▓čüąĄą│ąŠ ąĄčæ č乊čĆą╝ąĖčĆąŠą▓ą░čéčī ą▓ ą▒ą╗ąŠą║ąĄ ą┐ą░ą╝čÅčéąĖ, ą░ą┤čĆąĄčü ą┤ą╗čÅ ą║ąŠč鹊čĆąŠą│ąŠ č乊čĆą╝ąĖčĆąŠą▓ą░čéčī čü ą┐ąŠą╝ąŠčēčīčÄ čüčćčæčéčćąĖą║ą░.

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

|

|

|

|

|

ąÉąĮą┤čĆčÄčłą║ą░

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re:  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪą▒ ą╝ą░čĆ 13, 2010 12:33:24 |

|

| ąØą░čłąĄą╗ čéčĆą░ąĮąĘąĖčüč鹊čĆ. ą¤ąŠąĮčÄčģą░ą╗. |

|

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤ąĮ čÅąĮą▓ 04, 2010 02:19:25

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 152

ą×čéą║čāą┤ą░: čģąĘ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

Spartan3E ą┐ąĖčüą░ą╗(ą░): ąÉąĮą┤čĆčÄčłą║ą░ ą┐ąĖčüą░ą╗(ą░): ą¤ąĖą╗čā č鹊 ą┤ą░, ą┐čĆąŠčüč鹊 čüč湥čéčćąĖą║ąŠą╝ čüčćąĖčéą░čéčī ą▓ "+", ą┐ąŠč鹊ą╝ ą▓ "-". ą¤ąĖą╗ą░ ą┤ąĄą╗ą░ąĄčéčüčÅ ą║ąŠą╗čīčåąĄą▓čŗą╝ čüč湥čéčćąĖą║ąŠą╝ ą▓ + ą┐ąŠč鹊ą╝ ą▓ ą╝ą░ą║čüąĖą╝čāą╝ąĄ 0 ąĖ ą┐ąŠ ą║čĆčāą│čā. ą» ąĮąĄ č鹊 ąĮą░ą┐ąĖčüą░ą╗, ąĖą╝ąĄą╗ ą▓ą▓ąĖą┤čā ąĮąĄ ą┐ąĖą╗čā, ą░ /\/\/\/\/\/ Nobodevi4, ąĄą│ąŠ ą┐ąŠ ąĖą┤ąĄąĄ ą╝ąŠąČąĮąŠ ąĮą░ ą╗ąĄčéčā čĆą░čüčüčćąĖčéčŗą▓ą░čéčī, ąĮąŠ čÅ čüąĄą╣čćą░čü ąĮąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄ ą║ą░ą║.

_________________

ą×ą┐čŗčé čĆą░čüč鹥čé ą┐čĆčÅą╝ąŠ ą┐čĆąŠą┐ąŠčĆčåąĖąŠąĮą░ą╗čīąĮąŠ ą▓čŗą▓ąĄą┤ąĄąĮąĮąŠą╝čā ąĖąĘ čüčéčĆąŠčÅ ąŠą▒ąŠčĆčāą┤ąŠą▓ą░ąĮąĖčÄ.

______________

Jedem das Seine

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

|

|

|

|

|

Nobodevi4

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: Xilinx ISE 11....ą║ą░ą║?  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčé ą╝ą░čĆ 16, 2010 21:41:07 |

|

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪą▒ ą╝ą░čĆ 06, 2010 18:35:33

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 7

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

čŹčŹčŹ.....ą░ ąĄčüą╗ąĖ čā ą╝ąĄąĮčÅ čāąČąĄ ąĄčüčéčī ą▓ąĄčĆąĖą╗ąŠą│ąŠą▓čüą║ąĖą╣ čäą░ą╣ą╗ č鹥čüčéą▒ąĄąĮčćą░ ąĖ ą┐čĆąŠąĄą║čéą░, ą║ą░ą║ ą╝ąĮąĄ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą▓čüąĄ čŹč鹊 ą┤ąĄą╗ąŠ čüčüąĖą╝čāą╗ąĖčĆąŠą▓ą░čéčī...ąĮąĄ ą╝ąŠą│čā čĆą░ąĘąŠą▒čĆą░čéčīčüčÅ....ąĪąĖą╝čāą╗ąĖčĆčāčÄ ą▓ ModelSime...

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĀąĄą║ą╗ą░ą╝ą░

|

|

|

|

|

|

|

|

|

chronoman

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: Xilinx ISE 11....ą║ą░ą║?  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ą╝ą░čĆ 19, 2010 16:15:16 |

|

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé ą╝ą░čĆ 19, 2010 16:12:03

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 1

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

ąĖą╝ąĄą╗ąŠčüčī ą▓ ą▓ąĖą┤čā čłąĖą╝ąŠą╝ ą┤ąĄą╗ą░čéčī čüąĖąĮčāčü, čüą║ą▓ą░ąČąĮąŠčüčéčī ą╝ąŠąČąĮąŠ ą▓čŗčéą░čüą║ąĖą▓ą░čéčī ą║ą░ą║ ąĖąĘ čéą░ą▒ą╗ąĖčåčŗ čüąĖąĮčāčüą░, čéą░ą║ ąĖ ą┐ąŠ čĆą░ąĘąĮąŠčüčéąĮąŠą╝čā čāčĆą░ą▓ąĮąĄąĮąĖčÄ čü ą┐čĆą░ą▓ąĖą╗čīąĮčŗą╝ ąŠą║čĆčāą│ą╗ąĄąĮąĖąĄą╝

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

Spartan3E

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: Xilinx ISE 11....ą║ą░ą║?  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪą▒ ą╝ą░čĆ 20, 2010 16:44:01 |

|

| ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā! |

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé ą┤ąĄą║ 24, 2009 23:50:46

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 34

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

Nobodevi4 ą┐ąĖčüą░ą╗(ą░): čŹčŹčŹ.....ą░ ąĄčüą╗ąĖ čā ą╝ąĄąĮčÅ čāąČąĄ ąĄčüčéčī ą▓ąĄčĆąĖą╗ąŠą│ąŠą▓čüą║ąĖą╣ čäą░ą╣ą╗ č鹥čüčéą▒ąĄąĮčćą░ ąĖ ą┐čĆąŠąĄą║čéą░, ą║ą░ą║ ą╝ąĮąĄ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą▓čüąĄ čŹč鹊 ą┤ąĄą╗ąŠ čüčüąĖą╝čāą╗ąĖčĆąŠą▓ą░čéčī...ąĮąĄ ą╝ąŠą│čā čĆą░ąĘąŠą▒čĆą░čéčīčüčÅ....ąĪąĖą╝čāą╗ąĖčĆčāčÄ ą▓ ModelSime... ąÆąŠčé ą┐ąŠčćąĖčéą░ą╣. http://electronix.ru/forum/index.php?ac ... st&id=1293

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

uldemir

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: Xilinx ISE 11....ą║ą░ą║?  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪą▒ čÅąĮą▓ 22, 2011 22:22:47 |

|

| ąöčĆčāą│ ąÜąŠčéą░ |

|

ąÜą░čĆą╝ą░: 46

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 1368

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé ą░ą▓ą│ 28, 2009 21:34:30

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 7217

ą×čéą║čāą┤ą░: 845-ą╣ ą║ą╝.

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą£ąĄą┤ą░ą╗ąĖ: 1

|

|

ą» ą▓čŗčāčćąĖą╗ ąĮą░ VHDL ąĄčēąĄ ąŠą┤ąĮąŠ čüą╗ąŠą▓ąŠ! Generic ąĘąŠą▓ąĄčéčüčÅ. ą║ąŠčĆąŠč湥, čÅ čģąŠčćčā ą┐ąŠą▓č鹊čĆąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą╝ąŠą┤čāą╗ąĖ, ąĖ ą┤ą╗čÅ čŹč鹊ą│ąŠ ą╝ąĮąĄ ąĖą╝ ąĮą░ą┤ąŠ ą┐ąĄčĆąĄą┤ą░čéčī ą┐ą░čĆą░ą╝ąĄčéčĆ. ąØąŠ, č鹊ą┐ąŠą▓čŗą╣ čāčĆąŠą▓ąĄąĮčī čā ą╝ąĄąĮčÅ - schematic. ą│ą┤ąĄ ą╝ąĮąĄ ą┐čĆąŠą┐ąĖčüą░čéčī čüą▓ąŠą╣ generic_map, čćč鹊ą▒čŗ čŹč鹊 ą┐ąĄčĆąĄą┤ą░ą╗ąŠčüčī ą▓čüąĄą╝ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ ą╝ąŠą┤čāą╗čÅą╝?

_________________

ąÉ ą╗čÄą┤ąĖ ą┐ąŠčüą╝ąŠčéčĆčÅčé ąĖ čüą║ą░ąČčāčé: "ąĪąŠą▒ą░ą║ąĖ ą╗ąĄčéčÅčé. ąÆąŠčé ąĖ ąŠčüąĄąĮčī."

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

Meteor

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: Xilinx ISE 11....ą║ą░ą║?  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčü čÅąĮą▓ 23, 2011 09:51:27 |

|

| ąöčĆčāą│ ąÜąŠčéą░ |

|

ąÜą░čĆą╝ą░: 9

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 96

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤ąĮ ąĖčÄą╗ 13, 2009 14:37:39

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 3961

ą×čéą║čāą┤ą░: ą£ąŠčüą║ąŠą▓čüą║ą░čÅ ąŠą▒ą╗ą░čüčéčī, ąĮą░čāą║ąŠą│čĆą░ą┤.....

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

Ulemir, čćč鹊 ą╝ąĄčłą░ąĄčé ą┤ąĄą╗ą░čéčī ą▓ąĄčĆčģąĮąĖą╣ čāčĆąŠą▓ąĄąĮčī ą┐čĆąŠąĄą║čéą░ ąĮą░ VHDL (č湥čĆąĄąĘ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ ą║ ą┐čĆąĖą╝ąĄčĆčā)? ąÆąĄą┤čī, ąĮą░ ą╝ąŠą╣ ą▓ąĘą│ą╗čÅą┤, ą┐ą╗čÄčüąŠą▓ ą▒ąŠą╗čīčłąĄ č湥ą╝ ą╝ąĖąĮčāčüąŠą▓: ąÆąŠ-ą┐ąĄčĆą▓čŗčģ ą▓čüąĄ ąŠą┤ąĮąŠą╝ čüčéąĖą╗ąĄ (č鹊ą╗čīą║ąŠ ąŠą┐ąĖčüą░ąĮąĖąĄ); ą▓ąŠ ą▓č鹊čĆčŗčģ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐čĆąŠą▓ąĄčĆą║ąĖ ą▓čüąĄą│ąŠ ą┐čĆąŠąĄą║čéą░ ą▓ ą╝ąŠą┤ąĄą╗čüąĖą╝. ąØą░čüą║ąŠą╗čīą║ąŠ ąĘąĮą░čÄ, čüčģąĄą╝ą░čéąĖą║čā ą╝ąŠą┤ąĄą╗čüąĖą╝ ąĮąĄ ąŠčéčĆą░ą▒ą░čéčŗą▓ą░ąĄčé. ąÆčüąĄą│ą┤ą░ čĆą░ą▒ąŠčéą░ą╗ čü ą║ą▓ą░čĆčéčāčüąŠą╝, ą▓ ąĮąĄą╝ ąĄčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ąŠčéčĆąĖčüąŠą▓ą║ąĖ RTL čüčģąĄą╝čŗ čüąĖąĮč鹥ąĘąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ąØąĖąČąĄ ą┐čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąÜąŠą┤: --ą×ą┐ąĖčüą░ąĮąĖąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓

COMPONENT Timer_control

PORT(

s1,s4,clr,wrr,wrt,clrr,clrt,ouen:in std_logic;

sl:in std_logic_vector(2 downto 0);

ovfst:out std_logic;

RT:out std_logic_vector(7 downto 0);

Tbus:inout std_logic_vector(31 downto 0)

);

END COMPONENT;

..............

--čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓

TMC:Timer_control

PORT MAP(

s1=>s_stf(1),

s4=>s_stf(4),

clr=>s_gclr,

wrr=>WRR,

wrt=>WRT,

clrr=>CLRR,

clrt=>CLRT,

ouen=>slouen,

sl=>SLTM,

ovfst=>s_ovfts,

RT=>S_RT,

Tbus=>S_TBUS

);

ąĀąĄąĘčāą╗čīčéą░čé čüąĖąĮč鹥ąĘą░

| ąÆą╗ąŠąČąĄąĮąĖčÅ: |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖą╣ ą║ čäą░ą╣ą╗čā: ąĪčģąĄą╝ą░čéąĖą║ą░ čüąĖąĮč鹥ąĘą░ ąŠą┐ąĖčüą░ąĮąĖčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ

RTL_Viewer.JPG [50.35 KiB]

RTL_Viewer.JPG [50.35 KiB]

ąĪą║ą░čćąĖą▓ą░ąĮąĖą╣: 1723

|

_________________

ąŚą░ą│čĆčāąČą░čÅ ąĮą░ ą▓čģąŠą┤ ą║ąŠą╝ą┐čīčÄč鹥čĆą░ "ą╝čāčüąŠčĆ", ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐ąŠą╗čāčćąĖą╝ "ą╝čāčüąŠčĆ^32".

PS. ąØąĄ čĆą░ą▒ąŠčéą░čÄ čü: Proteus, Multisim, EWB, Micro-Cap... ąĮąĄ čüą┐čĆą░čłąĖą▓ą░ą╣č鹥 ą┤ą░ąČąĄ

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

uldemir

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: Xilinx ISE 11....ą║ą░ą║?  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčü čÅąĮą▓ 23, 2011 10:29:17 |

|

| ąöčĆčāą│ ąÜąŠčéą░ |

|

ąÜą░čĆą╝ą░: 46

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 1368

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé ą░ą▓ą│ 28, 2009 21:34:30

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 7217

ą×čéą║čāą┤ą░: 845-ą╣ ą║ą╝.

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą£ąĄą┤ą░ą╗ąĖ: 1

|

ąØąĄ ą┐ąĄčĆąĄčāą▒ąĄą┤ąĖč鹥, čŹč鹊 čÅ čāąČąĄ ą┐čĆąŠą▒ąŠą▓ą░ą╗. ą╝ąĮąĄ čéą░ą║ą░čÅ ą║ą░čĆčéąĖąĮą║ą░ ąĮą░ą│ą╗čÅą┤ąĮąĄąĄ: http://haos.homeip.net/NixieClock3/CoolNixieClock_cpld.PNGąÆąŠčé ą║ą░ąČą┤čŗą╣ ą╝ąŠą┤čāą╗čī ą▓ąĮčāčéčĆąĖ čāą┤ąŠą▒ąĮąĄąĄ ąĮą░ą┐ąĖčüą░čéčī ąĮą░ VHDL. ąÉ ąĄčüą╗ąĖ ą╝ąĮąĄ čŹčéčā ą║ą░čĆčéąĖąĮą║čā ą┐ąĖčüą░čéčī ąĮą░ VHDL č鹊 ą╝ąĮąĄ ą┐čĆąĖą┤ąĄčéčüčÅ ąĖą╝ąĄąĮąŠą▓ą░čéčī čåąĄą┐čī čüąŠąĄą┤ąĖąĮčÅčÄčēčāčÄ ą┤ą▓ą░ ą┐ąĖąĮą░ ą╝ąĄąČą┤čā manual ąĖ, čüą║ą░ąČąĄą╝, cnt_hour. ąÉ ąŠąĮąŠ ą╝ąĮąĄ ąĮą░ą┤ąŠ? ą» ąĖą╝ąĄąĮčāčÄ č鹊ą╗čīą║ąŠ ąĘąĮą░čćąĖą╝čŗąĄ ą┤ą╗čÅ ą╝ąĄąĮčÅ čåąĄą┐ąĖ ąÆąŠčé ą┐ąŠč鹊ą╝čā ąĖ čüč鹊ąĖčé ą▓ąŠą┐čĆąŠčü, ą│ą┤ąĄ čŹč鹊 ą╝ąŠąČąĮąŠ čāą║ą░ąĘą░čéčī? ą▓ ą┐čĆąŠą┐ąĄčĆčéčÅčģ ąŠą▒čŖąĄą║čéą░? ą╝ąŠąČąĄčé ą▓ čäą░ą╣ą╗ąĄ ą║ąŠąĮčüčéčĆą░ą╣ąĮč鹊ą▓? p.s. ąØą░čłąĄą╗ ą▓ synthesis properties čüčéčĆąŠčćą║čā Generics, Parameters. ąóąŠą╗čīą║ąŠ ą┐ą╗ąĄą▓ą░čéčī ąŠąĮąŠ čģąŠč鹥ą╗ąŠ. ą┐ąĖčłčā output_type:integer:=1 - ą░ ą▓čüąĄ čĆą░ą▓ąĮąŠ ą│ąĄąĮąĄčĆąĖčéčüčÅ čü ą┤ąĄčäą░čāą╗čéąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ output_type=>0

_________________

ąÉ ą╗čÄą┤ąĖ ą┐ąŠčüą╝ąŠčéčĆčÅčé ąĖ čüą║ą░ąČčāčé: "ąĪąŠą▒ą░ą║ąĖ ą╗ąĄčéčÅčé. ąÆąŠčé ąĖ ąŠčüąĄąĮčī."

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

dimitriy91

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: Xilinx ISE 11....ą║ą░ą║?  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤ąĮ ąĮąŠčÅ 19, 2012 10:39:07 |

|

| ąÆčŗą╝ąŠą│ą░č鹥ą╗čī ą┐čĆąĖą┐ąŠčÅ |

|

ąÜą░čĆą╝ą░: 3

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 17

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪčĆ ąĖčÄąĮ 08, 2011 15:37:56

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 619

ą×čéą║čāą┤ą░: ąöąÆ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

ąÆčüąĄą╝ ą┐čĆąĖą▓ąĄčé, ą┐ąŠą┤čüą║ą░ąČąĖč鹥 ą┐ąŠąČą░ą╗čāą╣čüčéą░ ą║ąĮąĖą│čā ą│ą┤ąĄ čĆą░čüą┐ąĖčüą░ąĮąŠ ą║ą░ą║ čüąŠąĘą┤ą░ą▓ą░čéčī ą┐ąŠą▓ąĄą┤ąĄąĮč湥čüą║čāčÄ ą╝ąŠą┤ąĄą╗čī( ąĮą░ VHDL) ąĮą░ xilinx , ąĖąĮč鹥čĆąĄčüčāąĄčé ąĖą╝ąĄąĮąĮąŠ ą║ąĮąĖą│ąĖ ą│ą┤ąĄ čĆą░čüčüą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ą┐ąŠčŹčéą░ą┐ąĮąŠ ą║ą║ čüąŠąĘą┤ą░ą▓ą░čéčī ąĖ ą║ąŠą╝ą┐ąĖą╗ąĖčĆąŠą▓ą░čéčī, ą▓čüąĄ ą║ąĮąĖą│ąĖ ą║ąŠč鹊čĆčŗąĄ čüą║ą░čćąĖą▓ą░čÄ ąĖą╝ąĄąĮąĮąŠ ą┐čĆąŠ čüą░ą╝ čÅąĘčŗą║ ąĖ ą░čĆčģąĖč鹥ą║čéčāčĆčā xilinx

_________________

"ąøąĄąĮąĖą▓čŗą╣ č湥ą╗ąŠą▓ąĄą║ ą▓ ą▒ąĄčüč湥čüčéąĮąŠą╝ ą┐ąŠą║ąŠąĄ čüčģąŠą┤ąĄąĮ čü ąĮąĄą┐ąŠą┤ą▓ąĖąČąĮąŠčÄ ą▒ąŠą╗ąŠčéąĮąŠčÄ ą▓ąŠą┤ąŠčÄ, ą║ąŠč鹊čĆą░čÅ, ą║čĆąŠą╝ąĄ čüą╝čĆą░ą┤čā ąĖ ą┐čĆąĄąĘčĆąĄąĮąĮčŗčģ ą│ą░ą┤ąĖąĮ, ąĮąĖč湥ą│ąŠ ąĮąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčé". ą£.ąÆ. ąøąŠą╝ąŠąĮąŠčüąŠą▓

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

uldemir

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: Xilinx ISE 11....ą║ą░ą║?  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤ąĮ ąĮąŠčÅ 19, 2012 11:05:21 |

|

| ąöčĆčāą│ ąÜąŠčéą░ |

|

ąÜą░čĆą╝ą░: 46

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 1368

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé ą░ą▓ą│ 28, 2009 21:34:30

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 7217

ą×čéą║čāą┤ą░: 845-ą╣ ą║ą╝.

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą£ąĄą┤ą░ą╗ąĖ: 1

|

viewtopic.php?p=1042615#p1042615ąĢčēąĄ ą▓ąŠčüą┐ąŠą╗čīąĘčāą╣č鹥čüčī ą┐ąŠąĖčüą║ąŠą╝ VHDL ą║ąĮąĖąČ*, VHDL ą║ąĮąĖą│*, VHDL XILINX

_________________

ąÉ ą╗čÄą┤ąĖ ą┐ąŠčüą╝ąŠčéčĆčÅčé ąĖ čüą║ą░ąČčāčé: "ąĪąŠą▒ą░ą║ąĖ ą╗ąĄčéčÅčé. ąÆąŠčé ąĖ ąŠčüąĄąĮčī."

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

kaknaxtak

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: Xilinx ISE 11....ą║ą░ą║?  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ąĖčÄą╗ 10, 2014 16:29:11 |

|

ąÜą░čĆą╝ą░: -1

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: -1

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤ąĮ ąĖčÄą╗ 21, 2008 12:34:48

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 87

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

|

ąöąŠą▒čĆąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ čüčāč鹊ą║!

ąÉ ąĄčüčéčī čā Xilinx ą▓ąĮčāčéčĆąĖčüčģąĄą╝ąĮčŗą╣ ąŠčéą╗ą░ą┤čćąĖą║ čéąĖą┐ą░ ąÉą╗čīč鹥čĆąŠą▓čüą║ąŠą│ąŠ SignalTap? ąśą╗ąĖ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ą░ ą║ą░ą║ą░čÅ? ąÜą░ą║ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ?

ąĪą┐ą░čüąĖą▒ąŠ.

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

Meteor

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: Xilinx ISE 11....ą║ą░ą║?  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪą▒ ąĖčÄą╗ 12, 2014 14:02:35 |

|

| ąöčĆčāą│ ąÜąŠčéą░ |

|

ąÜą░čĆą╝ą░: 9

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 96

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤ąĮ ąĖčÄą╗ 13, 2009 14:37:39

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 3961

ą×čéą║čāą┤ą░: ą£ąŠčüą║ąŠą▓čüą║ą░čÅ ąŠą▒ą╗ą░čüčéčī, ąĮą░čāą║ąŠą│čĆą░ą┤.....

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

kaknaxtak ą┐ąĖčüą░ą╗(ą░): ąÉ ąĄčüčéčī čā Xilinx ą▓ąĮčāčéčĆąĖčüčģąĄą╝ąĮčŗą╣ ąŠčéą╗ą░ą┤čćąĖą║ čéąĖą┐ą░ ąÉą╗čīč鹥čĆąŠą▓čüą║ąŠą│ąŠ SignalTap? ąśą╗ąĖ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ą░ ą║ą░ą║ą░čÅ? ąÜą░ą║ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ? ąśą╝čÅ ąĄą╝čā Chipscope ąĄčüą╗ąĖ ąĮąĄ ąŠčłąĖą▒ą░čÄčüčī.

_________________

ąŚą░ą│čĆčāąČą░čÅ ąĮą░ ą▓čģąŠą┤ ą║ąŠą╝ą┐čīčÄč鹥čĆą░ "ą╝čāčüąŠčĆ", ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐ąŠą╗čāčćąĖą╝ "ą╝čāčüąŠčĆ^32".

PS. ąØąĄ čĆą░ą▒ąŠčéą░čÄ čü: Proteus, Multisim, EWB, Micro-Cap... ąĮąĄ čüą┐čĆą░čłąĖą▓ą░ą╣č鹥 ą┤ą░ąČąĄ

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

wss60

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: Xilinx ISE 11....ą║ą░ą║?  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčü č乥ą▓ 08, 2015 20:02:26 |

|

| ą¤ąŠčéčĆąŠą│ą░ą╗ ą╗ą░ą┐ąŠą╣ ą┐ą░čÅą╗čīąĮąĖą║ |

|

ąÜą░čĆą╝ą░: 4

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 44

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé čüąĄąĮ 10, 2010 20:48:01

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 350

ą×čéą║čāą┤ą░: ą£ąĖąĮčüą║

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

|

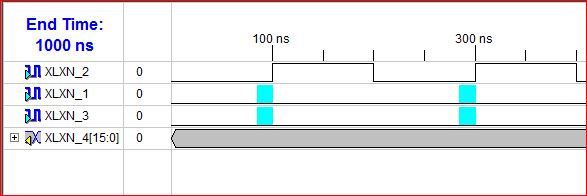

ąŚą┤čĆą░ą▓čüčéą▓čāą╣č鹥! ąÜč鹊 ąĮąĖą▒čāą┤čī ąĘąĮą░ąĄčé, ą║ą░ą║ ą▓ čüąĖą╝čāą╗čÅč鹊čĆąĄ Xilinx ISE čāą┐čĆą░ą▓ą╗čÅčéčī ą▓čģąŠą┤ą░ą╝ąĖ ŌĆō čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčī ą╗ąŠą│. 0/1 ąĖą╗ąĖ čéą░ą╣ą╝ąĄčĆ?

| ąÆą╗ąŠąČąĄąĮąĖčÅ: |

1.JPG [27.88 KiB]

1.JPG [27.88 KiB]

ąĪą║ą░čćąĖą▓ą░ąĮąĖą╣: 1042

|

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

uldemir

|

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: Xilinx ISE 11....ą║ą░ą║?  ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčü č乥ą▓ 08, 2015 20:48:07 |

|

| ąöčĆčāą│ ąÜąŠčéą░ |

|

ąÜą░čĆą╝ą░: 46

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 1368

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé ą░ą▓ą│ 28, 2009 21:34:30

ąĪąŠąŠą▒čēąĄąĮąĖą╣: 7217

ą×čéą║čāą┤ą░: 845-ą╣ ą║ą╝.

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą£ąĄą┤ą░ą╗ąĖ: 1

|

|

ąÜą░ą║ąŠą╣ ą▓ąĄčĆčüąĖąĖ? ą┐ąŠčüą╗ąĄ ą┤ąĄą▓čÅč鹊ą╣ č鹊ą╗čīą║ąŠ ą┐ąĖčüą░čéčī testbench ąĮą░ vhdl.

|

|

| ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ |

|

|

|

ąĪčéčĆą░ąĮąĖčåą░ 7 ąĖąĘ 8

|

[ ąĪąŠąŠą▒čēąĄąĮąĖą╣: 157 ] |

... , , , , |

ąÜč鹊 čüąĄą╣čćą░čü ąĮą░ č乊čĆčāą╝ąĄ |

ąĪąĄą╣čćą░čü čŹč鹊čé č乊čĆčāą╝ ą┐čĆąŠčüą╝ą░čéčĆąĖą▓ą░čÄčé: ąĮąĄčé ąĘą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╣ ąĖ ą│ąŠčüčéąĖ: 9 |

|

ąÆčŗ ąĮąĄ ą╝ąŠąČąĄč鹥 ąĮą░čćąĖąĮą░čéčī č鹥ą╝čŗ

ąÆčŗ ąĮąĄ ą╝ąŠąČąĄč鹥 ąŠčéą▓ąĄčćą░čéčī ąĮą░ čüąŠąŠą▒čēąĄąĮąĖčÅ

ąÆčŗ ąĮąĄ ą╝ąŠąČąĄč鹥 čĆąĄą┤ą░ą║čéąĖčĆąŠą▓ą░čéčī čüą▓ąŠąĖ čüąŠąŠą▒čēąĄąĮąĖčÅ

ąÆčŗ ąĮąĄ ą╝ąŠąČąĄč鹥 čāą┤ą░ą╗čÅčéčī čüą▓ąŠąĖ čüąŠąŠą▒čēąĄąĮąĖčÅ

ąÆčŗ ąĮąĄ ą╝ąŠąČąĄč鹥 ą┤ąŠą▒ą░ą▓ą╗čÅčéčī ą▓ą╗ąŠąČąĄąĮąĖčÅ

|

|

|