ążąŠčĆčāą╝ ąĀą░ą┤ąĖąŠąÜąŠčé • ą¤čĆąŠčüą╝ąŠčéčĆ č鹥ą╝čŗ - ąŻą╝ąĮąŠąČąĄąĮąĖąĄ ą╝ąĮąŠą│ąŠčćą╗ąĄąĮąŠą▓ ą║ąŠąĮąĄčćąĮąŠą│ąŠ ą┐ąŠą╗čÅ ą┐čĆąĖ ą┐ąŠą╝ąŠčēąĖ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓

ąĪąŠąŠą▒čēąĄąĮąĖčÅ ą▒ąĄąĘ ąŠčéą▓ąĄč鹊ą▓ | ąÉą║čéąĖą▓ąĮčŗąĄ č鹥ą╝čŗ

ąĪčéčĆą░ąĮąĖčåą░ 1 ąĖąĘ 1

[ ąĪąŠąŠą▒čēąĄąĮąĖą╣: 5 ]

ąÉą▓č鹊čĆ

ąĪąŠąŠą▒čēąĄąĮąĖąĄ

AngelicQuasar

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: ąŻą╝ąĮąŠąČąĄąĮąĖąĄ ą╝ąĮąŠą│ąŠčćą╗ąĄąĮąŠą▓ ą║ąŠąĮąĄčćąĮąŠą│ąŠ ą┐ąŠą╗čÅ ą┐čĆąĖ ą┐ąŠą╝ąŠčēąĖ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪčĆ č乥ą▓ 08, 2023 18:47:26

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪčĆ č乥ą▓ 08, 2023 01:13:37ąĪąŠąŠą▒čēąĄąĮąĖą╣: 11

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

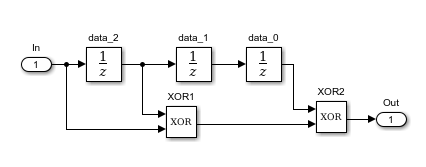

ąźąŠčćčā čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī čüčģąĄą╝čā ą┤ą╗čÅ čāą╝ąĮąŠąČąĄąĮąĖčÅ ą┐ąŠą╗ąĖąĮąŠą╝ąŠą▓ ąĮą░ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą┐ąŠą╗ąĖąĮąŠą╝ ą┐ąŠ ą║ąĮąĖą│ąĄ. ąØąĄ čāą▓ąĄčĆąĄąĮ, čćč鹊 ą▓čüąĄ ą┤ąĄą╗ą░čÄ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ. ą¤ąŠ ą╝ąĄč鹊ą┤ąĖčćą║ąĄ, ąĮą░ą│čāą│ą╗ąĄąĮąĮąŠą╣ ą▓ ąĖąĮč鹥čĆąĮąĄč鹥, ą┐čŗčéą░ą╗čüčÅ čĆą░ąĘąŠą▒čĆą░čéčīčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ čüą┤ą▓ąĖą│ą░ ąĖ ąĮą░ą┐ąĖčüą░ą╗ čéą░ą║ąŠą╣ ą║ąŠą┤:

ąÜąŠą┤:

module shift_reg(input logic clk,

ą» ą┐ą╗ąŠčģąŠ ą┐ąŠąĮąĖą╝ą░čÄ, ą║ą░ą║ ą▓ SystemVerilog ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą║ąŠąĮą║ą░č鹥ąĮą░čåąĖčÅ čłąĖąĮ:

ąÜąŠą┤:

data <= { in, data[2:1] };

ąŚą┤ąĄčüčī ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čłąĖąĮą░, ą│ą┤ąĄ in - čüčéą░čĆčłąĖą╣ čĆą░ąĘčĆčÅą┤, ą░ data[1] - čüą░ą╝čŗą╣ ą╝ą╗ą░ą┤čłąĖą╣? ą¦č鹊 ą▒čāą┤ąĄčé, ąĄčüą╗ąĖ ą┐ąŠą╝ąĄąĮčÅčéčī ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗąĄ ą╝ąĄčüčéą░ą╝ąĖ ąĖ ąĮą░ą┐ąĖčüą░čéčī:

ąÜąŠą┤:

data <= { data[2:1], in };

ąóąĄą┐ąĄčĆčī data[2] ąĖ data[1] ą▒čāą┤čāčé čüčéą░čĆčłąĖąĄ čĆą░ąĘčĆčÅą┤čŗ, ą░ in - čüą░ą╝čŗą╣ ą╝ą╗ą░ą┤čłąĖą╣?

ąæčāą┤ąĄčé ą╗ąĖ čüčģąĄą╝ą░ čĆą░ą▒ąŠčéą░čéčī ą┐ąŠ-ą┤čĆčāą│ąŠą╝čā, ąĄčüą╗ąĖ ąĮą░ą┐ąĖčüą░čéčī:

ąÜąŠą┤:

data <= { in, data[1:0],};

ąŚą┤ąĄčüčī čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ąĄčé ą┐ąŠą╗čāč湥ąĮąĮčŗąĄ ą▒ąĖčéčŗ ą▓ą╗ąĄą▓ąŠ, ą┐ąŠčŹč鹊ą╝čā ą║ąŠąĮą║ą░č鹥ąĮą░čåąĖčÅ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ, ą┐čĆąĖ ą║ąŠč鹊čĆąŠą╣ čŹčéąĖ ą▒ąĖčéčŗ čüą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ą╗ąĄą▓ąŠ.

ąś ąĄčēąĄ ą▓ąŠą┐čĆąŠčü. ąĢčüčéčī ą╗ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čüčĆą░ąĘčā ąĮą░ čłąĖčĆąŠą║čāčÄ čłąĖąĮčā (čüą║ą░ąČąĄą╝, 8 ą▒ąĖčé) ą▓čŗčüčéą░ą▓ąĖčéčī ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéčŗ ą╝ąĮąŠą│ąŠčćą╗ąĄąĮą░ ąĄą┤ąĖąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ, ą░ ąĮąĄ ą┐ąŠ ąŠą┤ąĮąŠą╝čā ą▒ąĖčéčā? ąÜą░ą║ čŹč鹊 čüą┤ąĄą╗ą░čéčī?

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ after 8 hours 39 minutes 47 seconds: ąś ąĄčēąĄ ą▓ąŠą┐čĆąŠčü

ąÜą░ą║ ąĘą░ą┤ą░čÄčéčüčÅ ąĖąĮą┤ąĄą║čüčŗ čłąĖąĮčŗ ą┐čĆąĖ ą║ąŠąĮą║ą░č鹥ąĮą░čåąĖąĖ čłąĖąĮ? ąÆąŠčé ąĮą░ą┐čĆąĖą╝ąĄčĆ:

wire [1:0] dataIn;

assign dataIn = {d1,d0};

ąóčāčé dataIn[0] čüąŠą┤ąĄčƹȹĖčé čüąĖą│ąĮą░ą╗ d0 ąĖą╗ąĖ d1? ąśą╗ąĖ čŹč鹊 ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ?

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

Gudd-Head

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąŻą╝ąĮąŠąČąĄąĮąĖąĄ ą╝ąĮąŠą│ąŠčćą╗ąĄąĮąŠą▓ ą║ąŠąĮąĄčćąĮąŠą│ąŠ ą┐ąŠą╗čÅ ą┐čĆąĖ ą┐ąŠą╝ąŠčēąĖ čĆąĄą│ąĖčüčéčĆą░

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé č乥ą▓ 09, 2023 18:05:18

ąöčĆčāą│ ąÜąŠčéą░

ąÜą░čĆą╝ą░: 67

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 1012

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé čüąĄąĮ 18, 2008 12:27:21ąĪąŠąŠą▒čēąĄąĮąĖą╣: 18798ą×čéą║čāą┤ą░: ąĪč鹊ą╗ąĖčåą░ ą£ąĖčĆą░ ąĪą░ąĮą║čé-ą¤ąĄč鹥čĆą▒čāčĆą│

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą£ąĄą┤ą░ą╗ąĖ: 1

ąóčāčé ąĮąĄ čüąŠą▓čüąĄą╝ čüą┤ą▓ąĖą│ąŠą▓čŗą╣ čĆąĄą│ąĖčüčéčĆ, čéčāčé ą┐čĆąŠčüč鹊 3 čéčĆąĖą│ą│ąĄčĆą░ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝.

ą£ąŠąČąĄč鹥 ą┐ąŠčüą╝ąŠčéčĆąĄčéčī ąĮą░ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą£ą░čéą╗ą░ą▒ąŠą╝ ą║ąŠą┤ ą┤ą╗čÅ čéą░ą║ąŠą│ąŠ ą╝ąŠą┤čāą╗čÅ:

ąóą░ą╝, ą║ąŠąĮąĄčćąĮąŠ, čüą╗ąĖčłą║ąŠą╝ ą╝ąĮąŠą│ąŠ ą╗ąĖčłąĮąĄą│ąŠ (ą║čāčćą░ ą░čüčüąĖą│ąĮąŠą▓, čĆąĄčüąĄčé, čåąĄ_ą░čāčé)... ąØąŠ ąĄčüą╗ąĖ ąĖčģ ą░ą║ą║čāčĆą░čéąĮąŠ ą┐ąŠčāą▒ąĖčĆą░čéčī, ą╝ąŠąČąĮąŠ ą┐čĆąĖą▒ą╗ąĖąĘąĖčéčī ą║ąŠą┤ ą║ ą▓ą░čłąĄą╝čā:

ąĪą┐ąŠą╣ą╗ąĄčĆ ąÜąŠą┤:

// ----------

ąśąĘą╝ąĄčĆąĖčéčī ąĮąĮąĮą░ą┤ą░?

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

AngelicQuasar

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąŻą╝ąĮąŠąČąĄąĮąĖąĄ ą╝ąĮąŠą│ąŠčćą╗ąĄąĮąŠą▓ ą║ąŠąĮąĄčćąĮąŠą│ąŠ ą┐ąŠą╗čÅ ą┐čĆąĖ ą┐ąŠą╝ąŠčēąĖ čĆąĄą│ąĖčüčéčĆą░

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé č乥ą▓ 09, 2023 20:49:50

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪčĆ č乥ą▓ 08, 2023 01:13:37ąĪąŠąŠą▒čēąĄąĮąĖą╣: 11

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą¤ąŠą╗čāčćą░ąĄčéčüčÅ, čćč鹊 ą╝ąŠąČąĮąŠ čüą┤ąĄą╗ą░čéčī čŹčéčā čüčģąĄą╝čā ąĖąĘ čéčĆąĄčģ ą┤-čéčĆąĖą│ą│ąĄčĆąŠą▓ ą▓ąŠčé čéą░ą║?

ąÜąŠą┤:

module flop(input logic clk, reset, in, output logic out);

ąÜąŠą┤:

module multiplier(input logic clk, reset, in,

ąÜąŠą┤:

module shift_reg_tb();

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ after 1 minute 36 seconds: Re: ąŻą╝ąĮąŠąČąĄąĮąĖąĄ ą╝ąĮąŠą│ąŠčćą╗ąĄąĮąŠą▓ ą║ąŠąĮąĄčćąĮąŠą│ąŠ ą┐ąŠą╗čÅ ą┐čĆąĖ ą┐ąŠą╝ąŠčēąĖ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ ą¦č鹊-č鹊 čüąĖą╝čāą╗čÅč鹊čĆ ą┐ąĄčćą░čéą░ąĄčé čüčéčĆą░ąĮąĮčŗąĄ čĆąĄąĘčāą╗čīčéą░čéčŗ. ą¤ąŠą┤ą░čÄ ąĮą░ ą▓čģąŠą┤ ą╝ąĮąŠą│ąŠčćą╗ąĄąĮ x^2 + 1 ą║ą░ą║ ą▒ąĖąĮą░čĆąĮčŗą╣ ą▓ąĄą║č鹊čĆ (1, 0, 1), čĆąĄąĘčāą╗čīčéą░č鹊ą╝ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą╝ąĮąŠą│ąŠčćą╗ąĄąĮ x^5 + x^4 + x^3 + 1 (ą▒ąĖąĮą░čĆąĮčŗą╣ ą▓ąĄą║č鹊čĆ 111001), ą░ čüąĖą╝čāą╗čÅč鹊čĆ ą┐ąĄčćą░čéą░ąĄčé 010111. ą¤ąŠčģąŠąČąĄ, ąĄčüą╗ąĖ čĆą░ąĘą▓ąĄčĆąĮčāčéčī ą▓ąĄą║č鹊čĆ, ąĮąŠ ąĮąĄ č鹊.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

Gudd-Head

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąŻą╝ąĮąŠąČąĄąĮąĖąĄ ą╝ąĮąŠą│ąŠčćą╗ąĄąĮąŠą▓ ą║ąŠąĮąĄčćąĮąŠą│ąŠ ą┐ąŠą╗čÅ ą┐čĆąĖ ą┐ąŠą╝ąŠčēąĖ čĆąĄą│ąĖčüčéčĆą░

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤ąĮ č乥ą▓ 13, 2023 18:14:45

ąöčĆčāą│ ąÜąŠčéą░

ąÜą░čĆą╝ą░: 67

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 1012

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé čüąĄąĮ 18, 2008 12:27:21ąĪąŠąŠą▒čēąĄąĮąĖą╣: 18798ą×čéą║čāą┤ą░: ąĪč鹊ą╗ąĖčåą░ ą£ąĖčĆą░ ąĪą░ąĮą║čé-ą¤ąĄč鹥čĆą▒čāčĆą│

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą£ąĄą┤ą░ą╗ąĖ: 1

ąöą░, ąĄčüą╗ąĖ ą▓čŗ ą┐ąŠą┤ą░čæč鹥 ąĮą░ ą▓čģąŠą┤ "101000", ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī "111001".

ąśąĘą╝ąĄčĆąĖčéčī ąĮąĮąĮą░ą┤ą░?

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĮą░ ąŠčüąĮąŠą▓ąĄ ąĮą░ą┤ąĄąČąĮčŗčģ ą╗ąĖčéąĖąĄą▓čŗčģ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆąŠą▓ EVE ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą░ąĘąĖą░čéčüą║ąŠą│ąŠ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░

ąÜą░č湥čüčéą▓ąĄąĮąĮąŠąĄ ąĖ ą▒ąĄąĘąŠą┐ą░čüąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, čĆą░ą▒ąŠčéą░čÄčēąĄąĄ ąŠčé ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░, ą┤ąŠą╗ąČąĮąŠ čāčćąĖčéčŗą▓ą░čéčī ąĄą│ąŠ čäąĖąĘąĖč湥čüą║ąĖąĄ ąĖ čģąĖą╝ąĖč湥čüą║ąĖąĄ čüą▓ąŠą╣čüčéą▓ą░, ą┐čĆąŠčäąĖą╗ąĖ ąĘą░čĆčÅą┤ą░ ąĖ čĆą░ąĘčĆčÅą┤ą░, ąĖčģ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ą▓ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąĖ ą┐ąŠą┤ ą▓ą╗ąĖčÅąĮąĖąĄą╝ čĆą░ąĘą╗ąĖčćąĮčŗčģ čāčüą╗ąŠą▓ąĖą╣, čéą░ą║ąĖčģ ą║ą░ą║ č鹥ą╝ą┐ąĄčĆą░čéčāčĆą░ ąĖ č鹊ą║ ąĮą░ą│čĆčāąĘą║ąĖ. ą£čŗ čĆą░čüčüą║ą░ąČąĄą╝ ąŠ ą╗ąĖčéąĖą╣-ąĖąŠąĮąĮčŗčģ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆąĮčŗčģ ą▒ą░čéą░čĆąĄčÅčģ EVE ąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čĆąĄčłąĄąĮąĖčÅčģ ąŠčé čĆą░ąĘą╗ąĖčćąĮčŗčģ ą║ąĖčéą░ą╣čüą║ąĖčģ ą║ąŠą╝ą┐ą░ąĮąĖą╣, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝čŗčģ ą┤ą╗čÅ čĆą░ąĘčĆą░ą▒ąŠč鹊ą║ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čŹčéąĖčģ ąÉąÜąæ. ą¤čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĮčŗąĄ ą▓ čüčéą░čéčīąĄ ą║ąĖčéą░ą╣čüą║ąĖąĄ ą░ąĮą░ą╗ąŠą│ąĖ ą┐ąŠą╝ąŠą│čāčé ąĘą░ą╝ąĄąĮąĖčéčī ą┐čĆąŠą┤čāą║čåąĖčÄ ąĘą░ą┐ą░ą┤ąĮčŗčģ ą▒čĆąĄąĮą┤ąŠą▓ čü ąŠą┐čéąĖą╝ąĖąĘą░čåąĖąĄą╣ čåąĄąĮčŗ ą▒ąĄąĘ ą┐ąŠč鹥čĆąĖ ą║ą░č湥čüčéą▓ą░.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ>>

AngelicQuasar

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ąŻą╝ąĮąŠąČąĄąĮąĖąĄ ą╝ąĮąŠą│ąŠčćą╗ąĄąĮąŠą▓ ą║ąŠąĮąĄčćąĮąŠą│ąŠ ą┐ąŠą╗čÅ ą┐čĆąĖ ą┐ąŠą╝ąŠčēąĖ čĆąĄą│ąĖčüčéčĆą░

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą╝ą░čĆ 30, 2023 19:05:55

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪčĆ č乥ą▓ 08, 2023 01:13:37ąĪąŠąŠą▒čēąĄąĮąĖą╣: 11

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąŻ ą╝ąĄąĮčÅ ąĮąĄ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čāą╝ąĮąŠąČą░čéčī ą╝ąĮąŠą│ąŠčćą╗ąĄąĮčŗ ą┐ąŠ čŹč鹊ą╣ čüčģąĄą╝ąĄ. ąÜą░ą║ ąĄąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ąĖ ą┐čĆąŠčüąĖą╝čāą╗ąĖčĆąŠą▓ą░čéčī?

ą» ą▓ąŠčé čéą░ą║ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ą╗ ąĄąĄ ąĮą░ ą▓ąĄčĆąĖą╗ąŠą│ąĄ:

ąÜąŠą┤:

module multiplier(

ąś ąĮą░ą┐ąĖčüą░ą╗ čéą░ą║ąŠą╣ č鹥čüčéą▒ąĄąĮčć:

ąÜąŠą┤:

module multiplier_tb();

ąØąŠ ąĮą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ f(x) = 1000 čüčģąĄą╝ą░ čĆą░ą▒ąŠčéą░ąĄčé ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠ. ą¤ąŠ ą╝ą░č鹥ą╝ą░čéąĖč湥čüą║ąĖą╣ čĆą░čüč湥čéą░ą╝ ą┤ąŠą╗ąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčīčüčÅ 1101000 - čĆąĄąĘčāą╗čīčéą░čé čāą╝ąĮąŠąČąĄąĮąĖčÅ ą╝ąĮąŠą│ąŠčćą╗ąĄąĮą░ g(x) = x^3 + x^2 + 1 ąĮą░ x^3, ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĮčŗą╣ ą▓ ą▓ąĖą┤ąĄ ą▓ąĄą║č鹊čĆą░ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą▓. ąÆ ą╗ąŠą│ąĄ čüąĖą╝čāą╗čÅč鹊čĆą░ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čéą░ą║ąŠąĄ: x00010000$stop ąóčāčé ąĮąĄą┐ąŠąĮčÅčéąĮąŠ ąŠčéą║čāą┤ą░ ą┐ąŠčÅą▓ąĖą╗čüčÅ ąĖą║čü, ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▒ąĖčé ą▓ąŠąŠą▒čēąĄ ą┤čĆčāą│ą░čÅ ą║ą░ą║ą░čÅ-č鹊. ąĪą║ą░ąČąĖč鹥, ą┐ąŠąČą░ą╗čāą╣čüčéą░, ą║ą░ą║ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī čŹčéčā čüčģąĄą╝čā ąĖ čüąĖą╝čāą╗ąĖčĆąŠą▓ą░čéčī ąĄąĄ, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖą╗čüčÅ ą▓ąĄčĆąĮčŗą╣ čĆąĄąĘčāą╗čīčéą░čé.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

ąĀąĄą║ą╗ą░ą╝ą░

ąØąŠą▓čŗą╣ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ EVE čüąĄčĆąĖąĖ PLM ą┤ą╗čÅ GSM-čéčĆąĄą║ąĄčĆąŠą▓, čĆą░ą▒ąŠčéą░čÄčēąĖčģ ą▓ ąČčæčüčéą║ąĖčģ čāčüą╗ąŠą▓ąĖčÅčģ (ą┤ąŠ -40┬░ąĪ)

ąÜąŠą╝ą┐ą░ąĮąĖčÅ EVE ą▓čŗą┐čāčüčéąĖą╗ą░ ąĮąŠą▓čŗą╣ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ čüąĄčĆąĖąĖ PLM, čüąŠč湥čéą░čÄčēąĖą╣ ą▓ čüąĄą▒ąĄ ą▓čŗčüąŠą║čāčÄ ą▒ąĄąĘąŠą┐ą░čüąĮąŠčüčéčī, ą┤ą╗ąĖč鹥ą╗čīąĮčŗą╣ čüčĆąŠą║ čüą╗čāąČą▒čŗ, čłąĖčĆąŠą║ąĖą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĮčŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĖ ą▓čŗčüąŠą║čāčÄ č鹊ą║ąŠąŠčéą┤ą░čćčā ą┤ą░ąČąĄ ą┐čĆąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ.

ąŁčéąĖ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆčŗ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąĘą░čĆčÅą┤ ą┐čĆąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ ąŠčé -40/-20┬░ąĪ (čüąĮąĖąČąĄąĮąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ č鹊ą║ą░), ą▒ąĄąĘąŠą┐ą░čüąĮčŗ (ąĮąĄ ą▓ąŠčüą┐ą╗ą░ą╝ąĄąĮčÅčÄčéčüčÅ ąĖ ąĮąĄ ą▓ąĘčĆčŗą▓ą░čÄčéčüčÅ) ą┐čĆąĖ ą╝ąĄčģą░ąĮąĖč湥čüą║ąŠą╝ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖąĖ (ą┐čĆąŠčéčŗą║ą░ąĮąĖąĄ ąĖ čüą┤ą░ą▓ą╗ąĖą▓ą░ąĮąĖąĄ), čāčüč鹊ą╣čćąĖą▓čŗ ą║ ą▓ąĖą▒čĆą░čåąĖąĖ. ą×ąĮąĖ ą╝ąŠą│čāčé ą┐čĆąĖą╝ąĄąĮčÅčéčīčüčÅ ą║ą░ą║ ą┤ą╗čÅ ą░ą▓č鹊čéčĆą░ąĮčüą┐ąŠčĆčéą░ (čéčĆąĄą║ąĄčĆčŗ, ą╝ą░čÅčćą║ąĖ, čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖčÅ), čéą░ą║ ąĖ ą┤ą╗čÅ ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░, IoT-čāčüčéčĆąŠą╣čüčéą▓.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ>>

ąĪčéčĆą░ąĮąĖčåą░ 1 ąĖąĘ 1

[ ąĪąŠąŠą▒čēąĄąĮąĖą╣: 5 ]

ąÜč鹊 čüąĄą╣čćą░čü ąĮą░ č乊čĆčāą╝ąĄ

ąĪąĄą╣čćą░čü čŹč鹊čé č乊čĆčāą╝ ą┐čĆąŠčüą╝ą░čéčĆąĖą▓ą░čÄčé: ąĮąĄčé ąĘą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╣ ąĖ ą│ąŠčüčéąĖ: 3

ąÆčŗ ąĮąĄ ą╝ąŠąČąĄč鹥 ąĮą░čćąĖąĮą░čéčī č鹥ą╝čŗąĮąĄ ą╝ąŠąČąĄč鹥 ąŠčéą▓ąĄčćą░čéčī ąĮą░ čüąŠąŠą▒čēąĄąĮąĖčÅąĮąĄ ą╝ąŠąČąĄč鹥 čĆąĄą┤ą░ą║čéąĖčĆąŠą▓ą░čéčī čüą▓ąŠąĖ čüąŠąŠą▒čēąĄąĮąĖčÅąĮąĄ ą╝ąŠąČąĄč鹥 čāą┤ą░ą╗čÅčéčī čüą▓ąŠąĖ čüąŠąŠą▒čēąĄąĮąĖčÅąĮąĄ ą╝ąŠąČąĄč鹥 ą┤ąŠą▒ą░ą▓ą╗čÅčéčī ą▓ą╗ąŠąČąĄąĮąĖčÅ