ążąŠčĆčāą╝ ąĀą░ą┤ąĖąŠąÜąŠčé • ą¤čĆąŠčüą╝ąŠčéčĆ č鹥ą╝čŗ - ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąĪąŠąŠą▒čēąĄąĮąĖčÅ ą▒ąĄąĘ ąŠčéą▓ąĄč鹊ą▓ | ąÉą║čéąĖą▓ąĮčŗąĄ č鹥ą╝čŗ

ąĪčéčĆą░ąĮąĖčåą░ 3 ąĖąĘ 4

[ ąĪąŠąŠą▒čēąĄąĮąĖą╣: 68 ]

, , ,

ąÉą▓č鹊čĆ

ąĪąŠąŠą▒čēąĄąĮąĖąĄ

Nevox

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé č乥ą▓ 01, 2013 17:50:31

ą£čāčćąĖč鹥ą╗čī ą╝ąĖą║čĆąŠčüčģąĄą╝

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé ą░ą▓ą│ 09, 2012 08:57:20ąĪąŠąŠą▒čēąĄąĮąĖą╣: 424

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą┐čĆąĖą┤ąĄčéčüčÅ ą┤čāą╝ą░čéčī čćč鹊-č鹊 ą│ąĄąĮąĖą░ą╗čīąĮąŠąĄ....

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

Pe3ucTop

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé č乥ą▓ 01, 2013 19:10:00

ą¤čĆąŠčĆąĄąĘą░ą╗ąĖčüčī ąĘčāą▒čŗ

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤čé ąĮąŠčÅ 16, 2007 13:52:44ąĪąŠąŠą▒čēąĄąĮąĖą╣: 231ą×čéą║čāą┤ą░: ąĀąĖą│ą░, ąøą░čéą▓ąĖčÅ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąÜą░ąČąĄčéčüčÅ ą▓čŗ ąĮąĄ ą▓ąĮąĖą╝ą░č鹥ą╗čīąĮčŗ!

1) ąÆ ąĖčüčģąŠą┤ąĮąŠą╝ ą║ąŠą┤ąĄ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ čĆąĄą│ąĖčüčéčĆ ! IN_REG[15..0] , ąŠčüčéą░ą╗čīąĮąŠąĄ ą▓čüčæ ą╗ąŠą│ąĖč湥čüą║ąĖąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ !

2) ąÆčŗ ąĮąĄ čĆą░ąĘąŠą▒čĆą░ą╗ąĖčüčī ą║ą░ą║ čĆą░ą▒ąŠčéą░čéčī čü ą┐ąŠčĆč鹊ą╝ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ čé.ąĄ. ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╝, ąĖ ą┐ąŠčŹč鹊ą╝čā ąĮą░ą▓ąĄčĆąĮąŠąĄ ą║ąŠą┤ ąĮąĄ čĆą░ą▒ąŠčéą░ąĄčé..

ą¤čĆąĖą╝ąĄčĆ ąŠčé ąÉą╗č鹥čĆčŗ:

ąÜąŠą┤:

module bidirec (oe, clk, inp, outp, bidir);

ąóąŠąĄčüčéčī čćąĖčéą░ąĄą╝ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčĆčéą░ ą║ąŠą│ą┤ą░ ąĄą╝čā ą┐čĆąĖčüą▓ąŠąĄąĮąŠ čüąŠčüč鹊čÅąĮąĖąĄ "Z"

ąÆ ąŠčüčéą░ą╗čīąĮąŠą╝, čģąŠčĆąŠčłąŠ čćč鹊 ą┤ą▓ąĖą│ą░ąĄč鹥čüčī ą▓ą┐ąĄčĆčæą┤..

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

ąĀą░ą┤ąĖąŠąøąŠą╝ą░č鹥ą╗čī

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą░ą▓ą│ 22, 2013 22:59:01

ą£čāą┤čĆčŗą╣ ą║ąŠčé

ąÜą░čĆą╝ą░: 11

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 21

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé ą░ą▓ą│ 21, 2008 22:03:30ąĪąŠąŠą▒čēąĄąĮąĖą╣: 1733ą×čéą║čāą┤ą░: ą×ą┤ąĄčüčüą░(ąŻą║čĆą░ąĖąĮą░)

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąöąŠą▒čĆčŗą╣ ą┤ąĄąĮčī! ąóą░ą║ą░čÅ ą┐čĆąŠą▒ą╗ąĄą╝ą░. ąĢčüčéčī ą║ąŠą┤ ąĮą░ Verilog, ą║ąŠč鹊čĆčŗą╣, ą┐ąŠ ąĖą┤ąĄąĄ, čĆąĄą░ą╗ąĖąĘčāąĄčé ą╝ą░čłąĖąĮčā čüąŠčüč鹊čÅąĮąĖą╣ ą┤ą╗čÅ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą╣ ą┐ą░ą╝čÅčéąĖ. ą¤čĆąŠą▒ą╗ąĄą╝ą░ ą▓ č鹊ą╝, čćč鹊 ą┐čĆąĖ ą║ąŠą╝ą┐ąĖą╗čÅčåąĖąĖ ą▓ State Machine Viewer-ąĄ čŹčéą░ ą╝ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ ą┐čĆąŠčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ ą║ą░ą║ ą┐čāčüčéą░čÅ. ąĪąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ, ą▓ ąČąĄą╗ąĄąĘą║ąĄ ąĮąĖč湥ą│ąŠ ąĮąĄ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé. ąŻą╝ąĄąĮčīčłąĖą╗ ą║ąŠą┤ ą┤ąŠ čéą░ą║ąŠą│ąŠ:

ąĪą┐ąŠą╣ą╗ąĄčĆ ąÜąŠą┤:

module MemInit (

ąÆčüąĄ čĆą░ą▓ąĮąŠ, ą╝ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ ąŠčüčéą░čæčéčüčÅ ą┐čāčüč鹊ą╣, čĆąĄą│ąĖčüčéčĆ init_done_reg ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĄą┤ąĖąĮąĖčåąĄą╣, čģąŠčéčÅ ąŠčłąĖą▒ąĖčéčüčÅ čéčāčé čéčĆčāą┤ąĮąŠ, ą▓čĆąŠą┤ąĄ ą║ą░ą║. ąŻąČąĄ ą▒čīčÄčüčī ą│ąŠą╗ąŠą▓ąŠą╣ ąŠą▒ čüč鹥ąĮčā. ą¦č鹊 čÅ ą┤ąĄą╗ą░čÄ ąĮąĄ čéą░ą║?

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

Pawel91

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčé ąŠą║čé 22, 2013 18:42:43

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčé ąŠą║čé 22, 2013 18:20:52ąĪąŠąŠą▒čēąĄąĮąĖą╣: 10

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąźąŠčćčā ąŠčüą▓ąŠąĖčéčī verilog

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĮą░ ąŠčüąĮąŠą▓ąĄ ąĮą░ą┤ąĄąČąĮčŗčģ ą╗ąĖčéąĖąĄą▓čŗčģ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆąŠą▓ EVE ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą░ąĘąĖą░čéčüą║ąŠą│ąŠ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░

ąÜą░č湥čüčéą▓ąĄąĮąĮąŠąĄ ąĖ ą▒ąĄąĘąŠą┐ą░čüąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, čĆą░ą▒ąŠčéą░čÄčēąĄąĄ ąŠčé ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░, ą┤ąŠą╗ąČąĮąŠ čāčćąĖčéčŗą▓ą░čéčī ąĄą│ąŠ čäąĖąĘąĖč湥čüą║ąĖąĄ ąĖ čģąĖą╝ąĖč湥čüą║ąĖąĄ čüą▓ąŠą╣čüčéą▓ą░, ą┐čĆąŠčäąĖą╗ąĖ ąĘą░čĆčÅą┤ą░ ąĖ čĆą░ąĘčĆčÅą┤ą░, ąĖčģ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ą▓ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąĖ ą┐ąŠą┤ ą▓ą╗ąĖčÅąĮąĖąĄą╝ čĆą░ąĘą╗ąĖčćąĮčŗčģ čāčüą╗ąŠą▓ąĖą╣, čéą░ą║ąĖčģ ą║ą░ą║ č鹥ą╝ą┐ąĄčĆą░čéčāčĆą░ ąĖ č鹊ą║ ąĮą░ą│čĆčāąĘą║ąĖ. ą£čŗ čĆą░čüčüą║ą░ąČąĄą╝ ąŠ ą╗ąĖčéąĖą╣-ąĖąŠąĮąĮčŗčģ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆąĮčŗčģ ą▒ą░čéą░čĆąĄčÅčģ EVE ąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čĆąĄčłąĄąĮąĖčÅčģ ąŠčé čĆą░ąĘą╗ąĖčćąĮčŗčģ ą║ąĖčéą░ą╣čüą║ąĖčģ ą║ąŠą╝ą┐ą░ąĮąĖą╣, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝čŗčģ ą┤ą╗čÅ čĆą░ąĘčĆą░ą▒ąŠč鹊ą║ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čŹčéąĖčģ ąÉąÜąæ. ą¤čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĮčŗąĄ ą▓ čüčéą░čéčīąĄ ą║ąĖčéą░ą╣čüą║ąĖąĄ ą░ąĮą░ą╗ąŠą│ąĖ ą┐ąŠą╝ąŠą│čāčé ąĘą░ą╝ąĄąĮąĖčéčī ą┐čĆąŠą┤čāą║čåąĖčÄ ąĘą░ą┐ą░ą┤ąĮčŗčģ ą▒čĆąĄąĮą┤ąŠą▓ čü ąŠą┐čéąĖą╝ąĖąĘą░čåąĖąĄą╣ čåąĄąĮčŗ ą▒ąĄąĘ ą┐ąŠč鹥čĆąĖ ą║ą░č湥čüčéą▓ą░.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ>>

ąĀą░ą┤ąĖąŠąøąŠą╝ą░č鹥ą╗čī

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąÆčé ąŠą║čé 22, 2013 20:37:51

ą£čāą┤čĆčŗą╣ ą║ąŠčé

ąÜą░čĆą╝ą░: 11

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 21

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé ą░ą▓ą│ 21, 2008 22:03:30ąĪąŠąŠą▒čēąĄąĮąĖą╣: 1733ą×čéą║čāą┤ą░: ą×ą┤ąĄčüčüą░(ąŻą║čĆą░ąĖąĮą░)

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

Pawel91 ą┐ąĖčüą░ą╗(ą░):

ą¤ąŠč湥ą╝čā ąĘą░ą┤ąĄčƹȹ║ą░ ąĮąĄ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé?

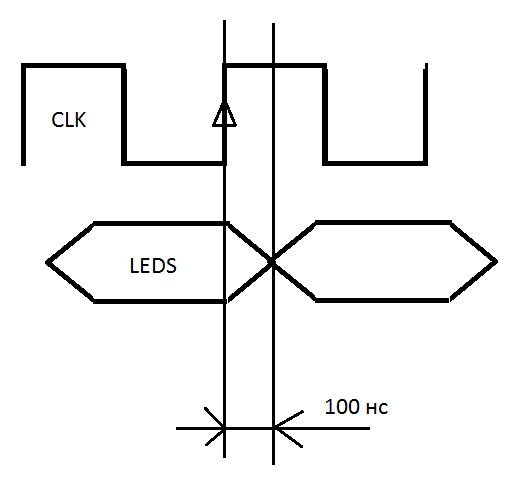

ą¦č鹊 ąĘąĮą░čćąĖčé, ąĮąĄ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé? ąØą░ą┐ąĖčüą░ąĮąĮąŠąĄ ą▓ą░ą╝ąĖ ąĘąĮą░čćąĖčé, čćč鹊 ą╝ąĄąČą┤čā ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╝ čäčĆąŠąĮč鹊ą╝ clk ąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄą╝ ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ leds ą▒čāą┤ąĄčé ąĘą░ą┤ąĄčƹȹ║ą░ 100 ąĮčü. ąØąŠ čćą░čüč鹊čéą░ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣ čĆąĄą│ąĖčüčéčĆą░ leds ą▒čāą┤ąĄčé ąŠą┐čĆąĄą┤ąĄą╗čÅčéčīčüčÅ čćą░čüč鹊č鹊ą╣ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ clk. ąÆąŠčé ą▓ą░ą╝ ą║ą░čĆčéąĖąĮą║ą░ ą┤ą╗čÅ ą┐ąŠčÅčüąĮąĄąĮąĖčÅ:

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

ąĀąĄą║ą╗ą░ą╝ą░

ąØąŠą▓čŗą╣ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ EVE čüąĄčĆąĖąĖ PLM ą┤ą╗čÅ GSM-čéčĆąĄą║ąĄčĆąŠą▓, čĆą░ą▒ąŠčéą░čÄčēąĖčģ ą▓ ąČčæčüčéą║ąĖčģ čāčüą╗ąŠą▓ąĖčÅčģ (ą┤ąŠ -40┬░ąĪ)

ąÜąŠą╝ą┐ą░ąĮąĖčÅ EVE ą▓čŗą┐čāčüčéąĖą╗ą░ ąĮąŠą▓čŗą╣ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ čüąĄčĆąĖąĖ PLM, čüąŠč湥čéą░čÄčēąĖą╣ ą▓ čüąĄą▒ąĄ ą▓čŗčüąŠą║čāčÄ ą▒ąĄąĘąŠą┐ą░čüąĮąŠčüčéčī, ą┤ą╗ąĖč鹥ą╗čīąĮčŗą╣ čüčĆąŠą║ čüą╗čāąČą▒čŗ, čłąĖčĆąŠą║ąĖą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĮčŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĖ ą▓čŗčüąŠą║čāčÄ č鹊ą║ąŠąŠčéą┤ą░čćčā ą┤ą░ąČąĄ ą┐čĆąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ.

ąŁčéąĖ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆčŗ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąĘą░čĆčÅą┤ ą┐čĆąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ ąŠčé -40/-20┬░ąĪ (čüąĮąĖąČąĄąĮąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ č鹊ą║ą░), ą▒ąĄąĘąŠą┐ą░čüąĮčŗ (ąĮąĄ ą▓ąŠčüą┐ą╗ą░ą╝ąĄąĮčÅčÄčéčüčÅ ąĖ ąĮąĄ ą▓ąĘčĆčŗą▓ą░čÄčéčüčÅ) ą┐čĆąĖ ą╝ąĄčģą░ąĮąĖč湥čüą║ąŠą╝ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖąĖ (ą┐čĆąŠčéčŗą║ą░ąĮąĖąĄ ąĖ čüą┤ą░ą▓ą╗ąĖą▓ą░ąĮąĖąĄ), čāčüč鹊ą╣čćąĖą▓čŗ ą║ ą▓ąĖą▒čĆą░čåąĖąĖ. ą×ąĮąĖ ą╝ąŠą│čāčé ą┐čĆąĖą╝ąĄąĮčÅčéčīčüčÅ ą║ą░ą║ ą┤ą╗čÅ ą░ą▓č鹊čéčĆą░ąĮčüą┐ąŠčĆčéą░ (čéčĆąĄą║ąĄčĆčŗ, ą╝ą░čÅčćą║ąĖ, čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖčÅ), čéą░ą║ ąĖ ą┤ą╗čÅ ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░, IoT-čāčüčéčĆąŠą╣čüčéą▓.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ>>

Pawel91

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪčĆ ąŠą║čé 23, 2013 11:25:13

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčé ąŠą║čé 22, 2013 18:20:52ąĪąŠąŠą▒čēąĄąĮąĖą╣: 10

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą» čéą░ą║ ąĖ ą┐čĆąĄą┤ą┐ąŠą╗ą░ą│ą░ą╗, ąĮąŠ čüąĖą╝čāą╗čÅčåąĖčÅ ą▓ ą║ą▓ą░čĆčéčāčü ą▓čŗą┤ą░ąĄčé ą┤čĆčāą│ąŠąĄ.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

Meteor

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪčĆ ąŠą║čé 23, 2013 19:20:08

ąöčĆčāą│ ąÜąŠčéą░

ąÜą░čĆą╝ą░: 9

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 96

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤ąĮ ąĖčÄą╗ 13, 2009 14:37:39ąĪąŠąŠą▒čēąĄąĮąĖą╣: 3961ą×čéą║čāą┤ą░: ą£ąŠčüą║ąŠą▓čüą║ą░čÅ ąŠą▒ą╗ą░čüčéčī, ąĮą░čāą║ąŠą│čĆą░ą┤.....

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąØąĄ čāą▓ąĄčĆąĄąĮ čćč鹊 ą▓ąĄčĆąĖą╗ąŠą│ čüąĖą╗čīąĮąŠ ąŠčéą╗ąĖčćą░ąĄčéčüčÅ, ąĮąŠ ą▓ ą▓čģą┤ą╗, ąĘą░ą┤ąĄčƹȹ║ą░ ąĖą╝ąĄąĄčé čüą╝čŗčüą╗ č鹊ą╗čīą║ąŠ ą▓ ą╝ąŠą┤ąĄą╗ąĖčĆąŠą▓ą░ąĮąĖąĖ (ąĮą░ą┐čĆąĖą╝ąĄčĆ čćč鹊 ą▒čŗ ąĘą░ą┤ą░čéčī čüą╝ąĄčēąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓), ą░ ą▓ čüąĖąĮč鹥ąĘąĄ (čĆąĄčćčī ą║ą░ą║ čÅ ą┐ąŠąĮčÅą╗ ąĖą╝ąĄąĮąĮąŠ ąŠ čüąĖąĮč鹥ąĘąĄ) ą║ąŠą╝ą░ąĮą┤ą░ ąĘą░ą┤ąĄčƹȹ║ąĖ ąĮąĄ čĆą░ą▒ąŠčéą░ąĄčé.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

Pawel91

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪčĆ ąŠą║čé 23, 2013 19:28:33

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčé ąŠą║čé 22, 2013 18:20:52ąĪąŠąŠą▒čēąĄąĮąĖą╣: 10

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą» ą▓ąŠčé ą║ą░ą║ čĆą░ąĘ ąĖ ą┤ąĄą╗ą░ą╗ ą╝ąŠą┤ąĄą╗ąĖčĆąŠą▓ą░ąĮąĖąĄ

, modelsim ą┐ąŠą║ą░ ąĮąĄ ąŠčüąĖą╗ąĖą╗, ą┤ąĄą╗ą░ą╗ ą▓ąŠ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą▓ 13 ą║ą▓ą░čĆčéčāčüąĄ čüąĖčüč鹥ą╝ąĄ ą╝ąŠą┤ąĄą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ(waveform editor), čāą║ą░ąĘą░ą╗ ąĮą░ ą║ąŠąĮą║čĆąĄčéąĮąŠ ą▓čĆąĄą╝ąĄąĮąĮąŠąĄ ą╝ąŠą┤ąĄą╗ąĖčĆąŠą▓ą░ąĮąĖąĄ, čÅ ą▓ąŠąŠą▒čēąĄ ą┤ąĄą╗ą░čÄ ą╗ą░ą▒čŗ čüčéčāą┤ąĄąĮčéą░ą╝, ą╝ąĮąĄ ąĮčāąČąĮąŠ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąĖąĘčāčćąĖčéčī čŹč鹊čé čÅąĘčŗą║, čéą░ą║ ą║ą░ą║ ą╗ą░ą▒čŗ ą▒čāą┤čāčé ąĮą░ ąŠčüą▓ąŠąĄąĮąĖąĄ čŹč鹊ą│ąŠ čÅąĘčŗą║ą░. ąÆąŠčé čģąŠčćčā ąĮą░čāčćąĖčéčīčüčÅ ą║ą░ą║ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą┐ąĖčüą░čéčī ąĘą░ą┤ąĄčƹȹ║ąĖ ą┤ą╗čÅ ą╝ąŠą┤čāą╗ąĄą╣.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

ąĀą░ą┤ąĖąŠąøąŠą╝ą░č鹥ą╗čī

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ąĪčĆ ąŠą║čé 23, 2013 22:50:37

ą£čāą┤čĆčŗą╣ ą║ąŠčé

ąÜą░čĆą╝ą░: 11

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 21

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé ą░ą▓ą│ 21, 2008 22:03:30ąĪąŠąŠą▒čēąĄąĮąĖą╣: 1733ą×čéą║čāą┤ą░: ą×ą┤ąĄčüčüą░(ąŻą║čĆą░ąĖąĮą░)

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

Pawel91 ą┐ąĖčüą░ą╗(ą░):

ą» ą▓ąŠčé ą║ą░ą║ čĆą░ąĘ ąĖ ą┤ąĄą╗ą░ą╗ ą╝ąŠą┤ąĄą╗ąĖčĆąŠą▓ą░ąĮąĖąĄ

ąÉ ą║ą░ą║ąŠą╣ ą┐ąĄčĆąĖąŠą┤ čā ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░? ą£ąŠąČąĄčé, ą▓ą░čłą░ ąĘą░ą┤ąĄčƹȹ║ą░ ą║čĆą░čéąĮą░ čŹč鹊ą╝čā ą┐ąĄčĆąĖąŠą┤čā?

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

Pawel91

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ąŠą║čé 24, 2013 06:02:40

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčé ąŠą║čé 22, 2013 18:20:52ąĪąŠąŠą▒čēąĄąĮąĖą╣: 10

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą¤ąĄčĆąĖąŠą┤ čĆą░ąĘąĮčŗą╣ ą┤ąĄą╗ą░ą╗ ąĖ 200 ąĖ 500 ąĮčü. ąŚą░ą┤ąĄčƹȹ║ą░ ąŠą┤ąĮą░ ąĖ čéą░ąČąĄ

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

Nevox

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ąŠą║čé 25, 2013 08:31:33

ą£čāčćąĖč鹥ą╗čī ą╝ąĖą║čĆąŠčüčģąĄą╝

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé ą░ą▓ą│ 09, 2012 08:57:20ąĪąŠąŠą▒čēąĄąĮąĖą╣: 424

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąŚą┤čĆą░ą▓čüčéą▓čāą╣č鹥! ą¤ąŠą╝ąŠą│ąĖč鹥 čĆą░ąĘąŠą▒čĆą░čéčīčüčÅ ą▓ ą║ąŠąĮąĄčćąĮčŗčģ ą░ą▓č鹊ą╝ą░čéą░čģ ąĮą░ ą▓ąĄčĆąĖą╗ąŠą│ąĄ ą┤ą╗čÅ ą░ą╗čīč鹥čĆčŗ.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

Pawel91

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ąŠą║čé 25, 2013 22:05:29

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčé ąŠą║čé 22, 2013 18:20:52ąĪąŠąŠą▒čēąĄąĮąĖą╣: 10

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄ ą▓ąŠą┐čĆąŠčü ą┐ąŠčĆąĄą║ąŠą╝ąĄąĮą┤čāą╣č鹥 ą┐ąŠąČą░ą╗čāą╣čüčéą░ čĆčāčüčüą║ąŠčÅąĘčŗčćąĮčāčÄ ą╗ąĖč鹥čĆą░čéčāčĆčā, čĆą░čüą║čĆčŗą▓ą░čÄčēčāčÄ čüąĖąĮčéą░ą║čüąĖčü ąĖ čüąĄą╝ą░ąĮčéąĖą║čā čÅąĘčŗą║ą░ Verilog HDL, ą░ č鹊 ą┤ąŠ čüąĖčģ ą┐ąŠčĆ ąĮąĄ ą╝ąŠą│čā čĆą░ąĘąŠą▒čĆą░čéčīčüčÅ čü čäčāąĮą║čåąĖčÅą╝ąĖ čüą╗ąĄą┤čāčÄčēąĖčģ ą║ąŠą╝ą░ąĮą┤

:

cmos

deassign

pmos

pull0

pull1

pullup

pulldown

rcmos

release

rnmos

rpmos

rtran

rtranif0

rtranif1

specparam

strength

strong

notif0

notif1

strong1

tran

tranif0

tranif1

small

medium

large

force

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

Nevox

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ąĮąŠčÅ 01, 2013 14:20:30

ą£čāčćąĖč鹥ą╗čī ą╝ąĖą║čĆąŠčüčģąĄą╝

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé ą░ą▓ą│ 09, 2012 08:57:20ąĪąŠąŠą▒čēąĄąĮąĖą╣: 424

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą¤ąŠą╝ąŠą│ąĖč鹥 čü ą╝ąĄą╗ąŠčćčīčÄ.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

Pawel91

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ąĮąŠčÅ 01, 2013 14:22:19

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčé ąŠą║čé 22, 2013 18:20:52ąĪąŠąŠą▒čēąĄąĮąĖą╣: 10

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą¤ąŠą┐čĆąŠą▒čāą╣č鹥

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

Nevox

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ąĮąŠčÅ 01, 2013 14:53:13

ą£čāčćąĖč鹥ą╗čī ą╝ąĖą║čĆąŠčüčģąĄą╝

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé ą░ą▓ą│ 09, 2012 08:57:20ąĪąŠąŠą▒čēąĄąĮąĖą╣: 424

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

čéą░ą║ ąĮąĄ čĆą░ą▒ąŠčéą░ąĄčé,ą╝ąĮąĄ ąĮą░ą┤ąŠ ą▓čģąŠą┤ čü ą▓čŗčģąŠą┤ąŠą╝ ąĮą░ą┐čĆčÅą╝čāčÄ čüą▓čÅąĘą░čéčī(

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

Pawel91

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ąĮąŠčÅ 01, 2013 14:55:32

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčé ąŠą║čé 22, 2013 18:20:52ąĪąŠąŠą▒čēąĄąĮąĖą╣: 10

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąó.ąĄ čüąŠąĘą┤ą░čéčī ąŠą▒čĆą░čéąĮčāčÄ čüą▓čÅąĘčī?

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

Nevox

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ąĮąŠčÅ 01, 2013 15:12:42

ą£čāčćąĖč鹥ą╗čī ą╝ąĖą║čĆąŠčüčģąĄą╝

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé ą░ą▓ą│ 09, 2012 08:57:20ąĪąŠąŠą▒čēąĄąĮąĖą╣: 424

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąĪą┤ąĄą╗ą░čéčī ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ) ąó.ąĄ ąĄčüčéčī ą░ą╗čīč鹥čĆą║ą░, ąĮą░ ąŠą┤ąĮčā ąĮąŠą│čā ą┐čĆąĖčģąŠą┤ąĖčé ąŠą┤ąĮąŠ, čü ą┤čĆčāą│ąŠą╣ ąĮąŠą│ąĖ ą▓čŗčģąŠą┤ąĖčé č鹊ąČąĄ čüą░ą╝ąŠąĄ, ą▓ ą┤ą░ąĮąĮąŠą╝ čüą╗čāčćą░ąĄ ą║ą╗ąŠą║.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

Pawel91

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ąĮąŠčÅ 01, 2013 15:20:51

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčé ąŠą║čé 22, 2013 18:20:52ąĪąŠąŠą▒čēąĄąĮąĖą╣: 10

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą┐ąŠą┐čĆąŠą▒čāą╣č鹥

assign CLK2=CLK1

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

Nevox

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ąĮąŠčÅ 01, 2013 15:28:31

ą£čāčćąĖč鹥ą╗čī ą╝ąĖą║čĆąŠčüčģąĄą╝

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¦čé ą░ą▓ą│ 09, 2012 08:57:20ąĪąŠąŠą▒čēąĄąĮąĖą╣: 424

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

čéą░ą║ č鹊ąČąĄ ąĮąĄ ą┐čĆąŠą║ą░čéčŗą▓ą░ąĄčé,ą┤ąĄą╗ą░ą╗ čāąČąĄ)

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

Pawel91

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠ Verilog

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ąĮąŠčÅ 01, 2013 15:37:03

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčé ąŠą║čé 22, 2013 18:20:52ąĪąŠąŠą▒čēąĄąĮąĖą╣: 10

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąÉ ą║ą░ą║ą░čÅ čćą░čüč鹊čéą░ ?

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĪčéčĆą░ąĮąĖčåą░ 3 ąĖąĘ 4

[ ąĪąŠąŠą▒čēąĄąĮąĖą╣: 68 ]

, , ,

ąÜč鹊 čüąĄą╣čćą░čü ąĮą░ č乊čĆčāą╝ąĄ

ąĪąĄą╣čćą░čü čŹč鹊čé č乊čĆčāą╝ ą┐čĆąŠčüą╝ą░čéčĆąĖą▓ą░čÄčé: ąĮąĄčé ąĘą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╣ ąĖ ą│ąŠčüčéąĖ: 5

ąÆčŗ ąĮąĄ ą╝ąŠąČąĄč鹥 ąĮą░čćąĖąĮą░čéčī č鹥ą╝čŗąĮąĄ ą╝ąŠąČąĄč鹥 ąŠčéą▓ąĄčćą░čéčī ąĮą░ čüąŠąŠą▒čēąĄąĮąĖčÅąĮąĄ ą╝ąŠąČąĄč鹥 čĆąĄą┤ą░ą║čéąĖčĆąŠą▓ą░čéčī čüą▓ąŠąĖ čüąŠąŠą▒čēąĄąĮąĖčÅąĮąĄ ą╝ąŠąČąĄč鹥 čāą┤ą░ą╗čÅčéčī čüą▓ąŠąĖ čüąŠąŠą▒čēąĄąĮąĖčÅąĮąĄ ą╝ąŠąČąĄč鹥 ą┤ąŠą▒ą░ą▓ą╗čÅčéčī ą▓ą╗ąŠąČąĄąĮąĖčÅ