–í—Å–µ —á—Ç–æ –¥–æ Stimulus process —Å–≥–µ–Ω–µ—Ä–∏–ª ise.

–ö–æ–¥:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY lab_test IS

END lab_test;

ARCHITECTURE behavior OF lab_test IS

COMPONENT lab4

PORT(

CLK : IN std_logic;

CE : IN std_logic;

SRST : IN std_logic;

Q : OUT std_logic

);

END COMPONENT;

--Inputs

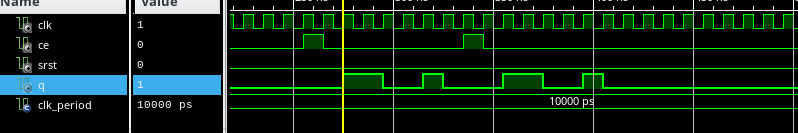

signal CLK : std_logic := '0';

signal CE : std_logic := '0';

signal SRST : std_logic := '1';

--Outputs

signal Q : std_logic;

-- Clock period definitions

constant CLK_period : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: lab4 PORT MAP (

CLK => CLK,

CE => CE,

SRST => SRST,

Q => Q

);

-- Clock process definitions

CLK_process :process

begin

CLK <= '0';

wait for CLK_period/2;

CLK <= '1';

wait for CLK_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

wait for 100 ns;

srst<='0';

wait for CLK_period*10;

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

ce<='1';

wait until rising_edge(clk);

ce<='0';

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

ce<='1';

wait until rising_edge(clk);

ce<='0';

wait until rising_edge(clk);

-- insert stimulus here

wait;

end process;

END;