–§–æ—Ä—É–º –Ý–∞–¥–∏–æ–ö–æ—Ç • –ü—Ä–æ—Å–º–æ—Ç—Ä —Ç–µ–º—ã - –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–°–æ–æ–±—â–µ–Ω–∏—è –±–µ–∑ –æ—Ç–≤–µ—Ç–æ–≤ | –ê–∫—Ç–∏–≤–Ω—ã–µ —Ç–µ–º—ã

–°—Ç—Ä–∞–Ω–∏—Ü–∞ 3 –∏–∑ 4

[ –°–æ–æ–±—â–µ–Ω–∏–π: 68 ]

, , ,

–ê–≤—Ç–æ—Ä

–°–æ–æ–±—â–µ–Ω–∏–µ

Nevox

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç —Ñ–µ–≤ 01, 2013 17:50:31

–ú—É—á–∏—Ç–µ–ª—å –º–∏–∫—Ä–æ—Å—Ö–µ–º

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ß—Ç –∞–≤–≥ 09, 2012 08:57:20–°–æ–æ–±—â–µ–Ω–∏–π: 426

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

–ø—Ä–∏–¥–µ—Ç—Å—è –¥—É–º–∞—Ç—å —á—Ç–æ-—Ç–æ –≥–µ–Ω–∏–∞–ª—å–Ω–æ–µ....

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

–Ý–µ–∫–ª–∞–º–∞

Pe3ucTop

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç —Ñ–µ–≤ 01, 2013 19:10:00

–ü—Ä–æ—Ä–µ–∑–∞–ª–∏—Å—å –∑—É–±—ã

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ü—Ç –Ω–æ—è 16, 2007 13:52:44–°–æ–æ–±—â–µ–Ω–∏–π: 231–û—Ç–∫—É–¥–∞: –Ý–∏–≥–∞, –õ–∞—Ç–≤–∏—è

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

–ö–∞–∂–µ—Ç—Å—è –≤—ã –Ω–µ –≤–Ω–∏–º–∞—Ç–µ–ª—å–Ω—ã!

1) –í –∏—Å—Ö–æ–¥–Ω–æ–º –∫–æ–¥–µ —Ç–æ–ª—å–∫–æ –æ–¥–∏–Ω —Ä–µ–≥–∏—Å—Ç—Ä ! IN_REG[15..0] , –æ—Å—Ç–∞–ª—å–Ω–æ–µ –≤—Å—ë –ª–æ–≥–∏—á–µ—Å–∫–∏–µ –¥–µ–π—Å—Ç–≤–∏—è !

2) –í—ã –Ω–µ —Ä–∞–∑–æ–±—Ä–∞–ª–∏—Å—å –∫–∞–∫ —Ä–∞–±–æ—Ç–∞—Ç—å —Å –ø–æ—Ä—Ç–æ–º –≤–≤–æ–¥–∞/–≤—ã–≤–æ–¥–∞ —Ç.–µ. –¥–≤—É–Ω–∞–ø—Ä–∞–≤–ª–µ–Ω–Ω—ã–º, –∏ –ø–æ—ç—Ç–æ–º—É –Ω–∞–≤–µ—Ä–Ω–æ–µ –∫–æ–¥ –Ω–µ —Ä–∞–±–æ—Ç–∞–µ—Ç..

–ü—Ä–∏–º–µ—Ä –æ—Ç –ê–ª—Ç–µ—Ä—ã:

–ö–æ–¥:

module bidirec (oe, clk, inp, outp, bidir);

–¢–æ–µ—Å—Ç—å —á–∏—Ç–∞–µ–º —Å–æ—Å—Ç–æ—è–Ω–∏–µ –ø–æ—Ä—Ç–∞ –∫–æ–≥–¥–∞ –µ–º—É –ø—Ä–∏—Å–≤–æ–µ–Ω–æ —Å–æ—Å—Ç–æ—è–Ω–∏–µ "Z"

–í –æ—Å—Ç–∞–ª—å–Ω–æ–º, —Ö–æ—Ä–æ—à–æ —á—Ç–æ –¥–≤–∏–≥–∞–µ—Ç–µ—Å—å –≤–ø–µ—Ä—ë–¥..

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

–Ý–µ–∫–ª–∞–º–∞

–Ý–∞–¥–∏–æ–õ–æ–º–∞—Ç–µ–ª—å

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –ß—Ç –∞–≤–≥ 22, 2013 22:59:01

–ú—É–¥—Ä—ã–π –∫–æ—Ç

–ö–∞—Ä–º–∞: 11

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 21

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ß—Ç –∞–≤–≥ 21, 2008 22:03:30–°–æ–æ–±—â–µ–Ω–∏–π: 1733–û—Ç–∫—É–¥–∞: –û–¥–µ—Å—Å–∞(–£–∫—Ä–∞–∏–Ω–∞)

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

–î–æ–±—Ä—ã–π –¥–µ–Ω—å! –¢–∞–∫–∞—è –ø—Ä–æ–±–ª–µ–º–∞. –ï—Å—Ç—å –∫–æ–¥ –Ω–∞ Verilog, –∫–æ—Ç–æ—Ä—ã–π, –ø–æ –∏–¥–µ–µ, —Ä–µ–∞–ª–∏–∑—É–µ—Ç –º–∞—à–∏–Ω—É —Å–æ—Å—Ç–æ—è–Ω–∏–π –¥–ª—è –∏–Ω–∏—Ü–∏–∞–ª–∏–∑–∞—Ü–∏–∏ –¥–∏–Ω–∞–º–∏—á–µ—Å–∫–æ–π –ø–∞–º—è—Ç–∏. –ü—Ä–æ–±–ª–µ–º–∞ –≤ —Ç–æ–º, —á—Ç–æ –ø—Ä–∏ –∫–æ–º–ø–∏–ª—è—Ü–∏–∏ –≤ State Machine Viewer-–µ —ç—Ç–∞ –º–∞—à–∏–Ω–∞ —Å–æ—Å—Ç–æ—è–Ω–∏–π –ø—Ä–æ—Å–º–∞—Ç—Ä–∏–≤–∞–µ—Ç—Å—è –∫–∞–∫ –ø—É—Å—Ç–∞—è. –°–æ–æ—Ç–≤–µ—Ç—Å—Ç–≤–µ–Ω–Ω–æ, –≤ –∂–µ–ª–µ–∑–∫–µ –Ω–∏—á–µ–≥–æ –Ω–µ —Å—Ä–∞–±–∞—Ç—ã–≤–∞–µ—Ç. –£–º–µ–Ω—å—à–∏–ª –∫–æ–¥ –¥–æ —Ç–∞–∫–æ–≥–æ:

–°–ø–æ–π–ª–µ—Ä –ö–æ–¥:

module MemInit (

–í—Å–µ —Ä–∞–≤–Ω–æ, –º–∞—à–∏–Ω–∞ —Å–æ—Å—Ç–æ—è–Ω–∏–π –æ—Å—Ç–∞—ë—Ç—Å—è –ø—É—Å—Ç–æ–π, —Ä–µ–≥–∏—Å—Ç—Ä init_done_reg –Ω–∏–∫–æ–≥–¥–∞ –Ω–µ —Å—Ç–∞–Ω–æ–≤–∏—Ç—Å—è –µ–¥–∏–Ω–∏—Ü–µ–π, —Ö–æ—Ç—è –æ—à–∏–±–∏—Ç—Å—è —Ç—É—Ç —Ç—Ä—É–¥–Ω–æ, –≤—Ä–æ–¥–µ –∫–∞–∫. –£–∂–µ –±—å—é—Å—å –≥–æ–ª–æ–≤–æ–π –æ–± —Å—Ç–µ–Ω—É. –ß—Ç–æ —è –¥–µ–ª–∞—é –Ω–µ —Ç–∞–∫?

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

Pawel91

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –í—Ç –æ–∫—Ç 22, 2013 18:42:43

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Ç –æ–∫—Ç 22, 2013 18:20:52–°–æ–æ–±—â–µ–Ω–∏–π: 10

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

–•–æ—á—É –æ—Å–≤–æ–∏—Ç—å verilog

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

–Ý–µ–∫–ª–∞–º–∞

–Ý–∞–¥–∏–æ–õ–æ–º–∞—Ç–µ–ª—å

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –í—Ç –æ–∫—Ç 22, 2013 20:37:51

–ú—É–¥—Ä—ã–π –∫–æ—Ç

–ö–∞—Ä–º–∞: 11

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 21

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ß—Ç –∞–≤–≥ 21, 2008 22:03:30–°–æ–æ–±—â–µ–Ω–∏–π: 1733–û—Ç–∫—É–¥–∞: –û–¥–µ—Å—Å–∞(–£–∫—Ä–∞–∏–Ω–∞)

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

Pawel91 –ø–∏—Å–∞–ª(–∞):

–ü–æ—á–µ–º—É –∑–∞–¥–µ—Ä–∂–∫–∞ –Ω–µ —Å—Ä–∞–±–∞—Ç—ã–≤–∞–µ—Ç?

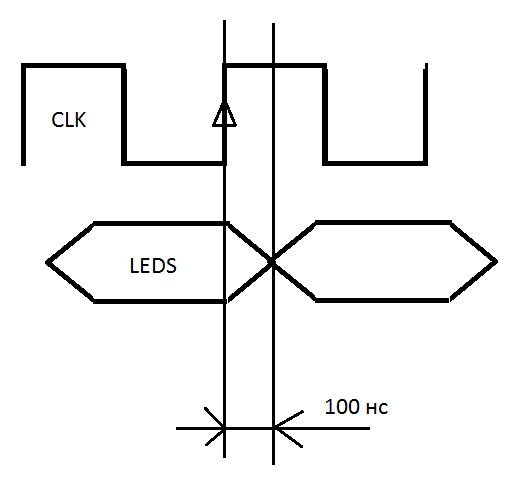

–ß—Ç–æ –∑–Ω–∞—á–∏—Ç, –Ω–µ —Å—Ä–∞–±–∞—Ç—ã–≤–∞–µ—Ç? –ù–∞–ø–∏—Å–∞–Ω–Ω–æ–µ –≤–∞–º–∏ –∑–Ω–∞—á–∏—Ç, —á—Ç–æ –º–µ–∂–¥—É –ø–æ–ª–æ–∂–∏—Ç–µ–ª—å–Ω—ã–º —Ñ—Ä–æ–Ω—Ç–æ–º clk –∏ –∏–∑–º–µ–Ω–µ–Ω–∏–µ–º –∑–Ω–∞—á–µ–Ω–∏—è —Ä–µ–≥–∏—Å—Ç—Ä–∞ leds –±—É–¥–µ—Ç –∑–∞–¥–µ—Ä–∂–∫–∞ 100 –Ω—Å. –ù–æ —á–∞—Å—Ç–æ—Ç–∞ –∏–∑–º–µ–Ω–µ–Ω–∏–π —Ä–µ–≥–∏—Å—Ç—Ä–∞ leds –±—É–¥–µ—Ç –æ–ø—Ä–µ–¥–µ–ª—è—Ç—å—Å—è —á–∞—Å—Ç–æ—Ç–æ–π —Ç–∞–∫—Ç–∏—Ä–æ–≤–∞–Ω–∏—è clk. –í–æ—Ç –≤–∞–º –∫–∞—Ä—Ç–∏–Ω–∫–∞ –¥–ª—è –ø–æ—è—Å–Ω–µ–Ω–∏—è:

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

–Ý–µ–∫–ª–∞–º–∞

Pawel91

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –°—Ä –æ–∫—Ç 23, 2013 11:25:13

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Ç –æ–∫—Ç 22, 2013 18:20:52–°–æ–æ–±—â–µ–Ω–∏–π: 10

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

–Ø —Ç–∞–∫ –∏ –ø—Ä–µ–¥–ø–æ–ª–∞–≥–∞–ª, –Ω–æ —Å–∏–º—É–ª—è—Ü–∏—è –≤ –∫–≤–∞—Ä—Ç—É—Å –≤—ã–¥–∞–µ—Ç –¥—Ä—É–≥–æ–µ.

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

–Ý–µ–∫–ª–∞–º–∞

Meteor

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –°—Ä –æ–∫—Ç 23, 2013 19:20:08

–î—Ä—É–≥ –ö–æ—Ç–∞

–ö–∞—Ä–º–∞: 9

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 96

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ü–Ω –∏—é–ª 13, 2009 14:37:39–°–æ–æ–±—â–µ–Ω–∏–π: 3961–û—Ç–∫—É–¥–∞: –ú–æ—Å–∫–æ–≤—Å–∫–∞—è –æ–±–ª–∞—Å—Ç—å, –Ω–∞—É–∫–æ–≥—Ä–∞–¥.....

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

–ù–µ —É–≤–µ—Ä–µ–Ω —á—Ç–æ –≤–µ—Ä–∏–ª–æ–≥ —Å–∏–ª—å–Ω–æ –æ—Ç–ª–∏—á–∞–µ—Ç—Å—è, –Ω–æ –≤ –≤—Ö–¥–ª, –∑–∞–¥–µ—Ä–∂–∫–∞ –∏–º–µ–µ—Ç —Å–º—ã—Å–ª —Ç–æ–ª—å–∫–æ –≤ –º–æ–¥–µ–ª–∏—Ä–æ–≤–∞–Ω–∏–∏ (–Ω–∞–ø—Ä–∏–º–µ—Ä —á—Ç–æ –±—ã –∑–∞–¥–∞—Ç—å —Å–º–µ—â–µ–Ω–∏–µ —Å–∏–≥–Ω–∞–ª–æ–≤), –∞ –≤ —Å–∏–Ω—Ç–µ–∑–µ (—Ä–µ—á—å –∫–∞–∫ —è –ø–æ–Ω—è–ª –∏–º–µ–Ω–Ω–æ –æ —Å–∏–Ω—Ç–µ–∑–µ) –∫–æ–º–∞–Ω–¥–∞ –∑–∞–¥–µ—Ä–∂–∫–∏ –Ω–µ —Ä–∞–±–æ—Ç–∞–µ—Ç.

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

Pawel91

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –°—Ä –æ–∫—Ç 23, 2013 19:28:33

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Ç –æ–∫—Ç 22, 2013 18:20:52–°–æ–æ–±—â–µ–Ω–∏–π: 10

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

–Ø –≤–æ—Ç –∫–∞–∫ —Ä–∞–∑ –∏ –¥–µ–ª–∞–ª –º–æ–¥–µ–ª–∏—Ä–æ–≤–∞–Ω–∏–µ

, modelsim –ø–æ–∫–∞ –Ω–µ –æ—Å–∏–ª–∏–ª, –¥–µ–ª–∞–ª –≤–æ –≤—Å—Ç—Ä–æ–µ–Ω–Ω–æ–π –≤ 13 –∫–≤–∞—Ä—Ç—É—Å–µ —Å–∏—Å—Ç–µ–º–µ –º–æ–¥–µ–ª–∏—Ä–æ–≤–∞–Ω–∏—è(waveform editor), —É–∫–∞–∑–∞–ª –Ω–∞ –∫–æ–Ω–∫—Ä–µ—Ç–Ω–æ –≤—Ä–µ–º–µ–Ω–Ω–æ–µ –º–æ–¥–µ–ª–∏—Ä–æ–≤–∞–Ω–∏–µ, —è –≤–æ–æ–±—â–µ –¥–µ–ª–∞—é –ª–∞–±—ã —Å—Ç—É–¥–µ–Ω—Ç–∞–º, –º–Ω–µ –Ω—É–∂–Ω–æ –ø–æ–ª–Ω–æ—Å—Ç—å—é –∏–∑—É—á–∏—Ç—å —ç—Ç–æ—Ç —è–∑—ã–∫, —Ç–∞–∫ –∫–∞–∫ –ª–∞–±—ã –±—É–¥—É—Ç –Ω–∞ –æ—Å–≤–æ–µ–Ω–∏–µ —ç—Ç–æ–≥–æ —è–∑—ã–∫–∞. –í–æ—Ç —Ö–æ—á—É –Ω–∞—É—á–∏—Ç—å—Å—è –∫–∞–∫ –ø—Ä–∞–≤–∏–ª—å–Ω–æ –ø–∏—Å–∞—Ç—å –∑–∞–¥–µ—Ä–∂–∫–∏ –¥–ª—è –º–æ–¥—É–ª–µ–π.

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

–Ý–∞–¥–∏–æ–õ–æ–º–∞—Ç–µ–ª—å

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –°—Ä –æ–∫—Ç 23, 2013 22:50:37

–ú—É–¥—Ä—ã–π –∫–æ—Ç

–ö–∞—Ä–º–∞: 11

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 21

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ß—Ç –∞–≤–≥ 21, 2008 22:03:30–°–æ–æ–±—â–µ–Ω–∏–π: 1733–û—Ç–∫—É–¥–∞: –û–¥–µ—Å—Å–∞(–£–∫—Ä–∞–∏–Ω–∞)

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

Pawel91 –ø–∏—Å–∞–ª(–∞):

–Ø –≤–æ—Ç –∫–∞–∫ —Ä–∞–∑ –∏ –¥–µ–ª–∞–ª –º–æ–¥–µ–ª–∏—Ä–æ–≤–∞–Ω–∏–µ

–ê –∫–∞–∫–æ–π –ø–µ—Ä–∏–æ–¥ —É –∏—Å—Ç–æ—á–Ω–∏–∫–∞ —Ç–∞–∫—Ç–æ–≤–æ–≥–æ —Å–∏–≥–Ω–∞–ª–∞? –ú–æ–∂–µ—Ç, –≤–∞—à–∞ –∑–∞–¥–µ—Ä–∂–∫–∞ –∫—Ä–∞—Ç–Ω–∞ —ç—Ç–æ–º—É –ø–µ—Ä–∏–æ–¥—É?

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

–Ý–µ–∫–ª–∞–º–∞

Pawel91

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –ß—Ç –æ–∫—Ç 24, 2013 06:02:40

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Ç –æ–∫—Ç 22, 2013 18:20:52–°–æ–æ–±—â–µ–Ω–∏–π: 10

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

–ü–µ—Ä–∏–æ–¥ —Ä–∞–∑–Ω—ã–π –¥–µ–ª–∞–ª –∏ 200 –∏ 500 –Ω—Å. –ó–∞–¥–µ—Ä–∂–∫–∞ –æ–¥–Ω–∞ –∏ —Ç–∞–∂–µ

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

Nevox

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –æ–∫—Ç 25, 2013 08:31:33

–ú—É—á–∏—Ç–µ–ª—å –º–∏–∫—Ä–æ—Å—Ö–µ–º

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ß—Ç –∞–≤–≥ 09, 2012 08:57:20–°–æ–æ–±—â–µ–Ω–∏–π: 426

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

–ó–¥—Ä–∞–≤—Å—Ç–≤—É–π—Ç–µ! –ü–æ–º–æ–≥–∏—Ç–µ —Ä–∞–∑–æ–±—Ä–∞—Ç—å—Å—è –≤ –∫–æ–Ω–µ—á–Ω—ã—Ö –∞–≤—Ç–æ–º–∞—Ç–∞—Ö –Ω–∞ –≤–µ—Ä–∏–ª–æ–≥–µ –¥–ª—è –∞–ª—å—Ç–µ—Ä—ã.

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

Pawel91

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –æ–∫—Ç 25, 2013 22:05:29

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Ç –æ–∫—Ç 22, 2013 18:20:52–°–æ–æ–±—â–µ–Ω–∏–π: 10

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

–ü–æ–¥–¥–µ—Ä–∂–∏–≤–∞—é –≤–æ–ø—Ä–æ—Å –ø–æ—Ä–µ–∫–æ–º–µ–Ω–¥—É–π—Ç–µ –ø–æ–∂–∞–ª—É–π—Å—Ç–∞ —Ä—É—Å—Å–∫–æ—è–∑—ã—á–Ω—É—é –ª–∏—Ç–µ—Ä–∞—Ç—É—Ä—É, —Ä–∞—Å–∫—Ä—ã–≤–∞—é—â—É—é —Å–∏–Ω—Ç–∞–∫—Å–∏—Å –∏ —Å–µ–º–∞–Ω—Ç–∏–∫—É —è–∑—ã–∫–∞ Verilog HDL, –∞ —Ç–æ –¥–æ —Å–∏—Ö –ø–æ—Ä –Ω–µ –º–æ–≥—É —Ä–∞–∑–æ–±—Ä–∞—Ç—å—Å—è —Å —Ñ—É–Ω–∫—Ü–∏—è–º–∏ —Å–ª–µ–¥—É—é—â–∏—Ö –∫–æ–º–∞–Ω–¥

:

cmos

deassign

pmos

pull0

pull1

pullup

pulldown

rcmos

release

rnmos

rpmos

rtran

rtranif0

rtranif1

specparam

strength

strong

notif0

notif1

strong1

tran

tranif0

tranif1

small

medium

large

force

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

Nevox

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –Ω–æ—è 01, 2013 14:20:30

–ú—É—á–∏—Ç–µ–ª—å –º–∏–∫—Ä–æ—Å—Ö–µ–º

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ß—Ç –∞–≤–≥ 09, 2012 08:57:20–°–æ–æ–±—â–µ–Ω–∏–π: 426

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

–ü–æ–º–æ–≥–∏—Ç–µ —Å –º–µ–ª–æ—á—å—é.

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

Pawel91

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –Ω–æ—è 01, 2013 14:22:19

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Ç –æ–∫—Ç 22, 2013 18:20:52–°–æ–æ–±—â–µ–Ω–∏–π: 10

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

–ü–æ–ø—Ä–æ–±—É–π—Ç–µ

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

Nevox

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –Ω–æ—è 01, 2013 14:53:13

–ú—É—á–∏—Ç–µ–ª—å –º–∏–∫—Ä–æ—Å—Ö–µ–º

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ß—Ç –∞–≤–≥ 09, 2012 08:57:20–°–æ–æ–±—â–µ–Ω–∏–π: 426

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

—Ç–∞–∫ –Ω–µ —Ä–∞–±–æ—Ç–∞–µ—Ç,–º–Ω–µ –Ω–∞–¥–æ –≤—Ö–æ–¥ —Å –≤—ã—Ö–æ–¥–æ–º –Ω–∞–ø—Ä—è–º—É—é —Å–≤—è–∑–∞—Ç—å(

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

Pawel91

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –Ω–æ—è 01, 2013 14:55:32

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Ç –æ–∫—Ç 22, 2013 18:20:52–°–æ–æ–±—â–µ–Ω–∏–π: 10

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

–¢.–µ —Å–æ–∑–¥–∞—Ç—å –æ–±—Ä–∞—Ç–Ω—É—é —Å–≤—è–∑—å?

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

Nevox

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –Ω–æ—è 01, 2013 15:12:42

–ú—É—á–∏—Ç–µ–ª—å –º–∏–∫—Ä–æ—Å—Ö–µ–º

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ß—Ç –∞–≤–≥ 09, 2012 08:57:20–°–æ–æ–±—â–µ–Ω–∏–π: 426

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

–°–¥–µ–ª–∞—Ç—å –ø–µ—Ä–µ–Ω–∞–ø—Ä–∞–≤–ª–µ–Ω–∏–µ) –¢.–µ –µ—Å—Ç—å –∞–ª—å—Ç–µ—Ä–∫–∞, –Ω–∞ –æ–¥–Ω—É –Ω–æ–≥—É –ø—Ä–∏—Ö–æ–¥–∏—Ç –æ–¥–Ω–æ, —Å –¥—Ä—É–≥–æ–π –Ω–æ–≥–∏ –≤—ã—Ö–æ–¥–∏—Ç —Ç–æ–∂–µ —Å–∞–º–æ–µ, –≤ –¥–∞–Ω–Ω–æ–º —Å–ª—É—á–∞–µ –∫–ª–æ–∫.

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

Pawel91

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –Ω–æ—è 01, 2013 15:20:51

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Ç –æ–∫—Ç 22, 2013 18:20:52–°–æ–æ–±—â–µ–Ω–∏–π: 10

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

–ø–æ–ø—Ä–æ–±—É–π—Ç–µ

assign CLK2=CLK1

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

Nevox

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –Ω–æ—è 01, 2013 15:28:31

–ú—É—á–∏—Ç–µ–ª—å –º–∏–∫—Ä–æ—Å—Ö–µ–º

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ß—Ç –∞–≤–≥ 09, 2012 08:57:20–°–æ–æ–±—â–µ–Ω–∏–π: 426

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

—Ç–∞–∫ —Ç–æ–∂–µ –Ω–µ –ø—Ä–æ–∫–∞—Ç—ã–≤–∞–µ—Ç,–¥–µ–ª–∞–ª —É–∂–µ)

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

Pawel91

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –≤–æ–ø—Ä–æ—Å—ã –ø–æ Verilog

–î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –Ω–æ—è 01, 2013 15:37:03

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Ç –æ–∫—Ç 22, 2013 18:20:52–°–æ–æ–±—â–µ–Ω–∏–π: 10

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

–ê –∫–∞–∫–∞—è —á–∞—Å—Ç–æ—Ç–∞ ?

–í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö

–°—Ç—Ä–∞–Ω–∏—Ü–∞ 3 –∏–∑ 4

[ –°–æ–æ–±—â–µ–Ω–∏–π: 68 ]

, , ,

–ö—Ç–æ —Å–µ–π—á–∞—Å –Ω–∞ —Ñ–æ—Ä—É–º–µ

–°–µ–π—á–∞—Å —ç—Ç–æ—Ç —Ñ–æ—Ä—É–º –ø—Ä–æ—Å–º–∞—Ç—Ä–∏–≤–∞—é—Ç: –Ω–µ—Ç –∑–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω–Ω—ã—Ö –ø–æ–ª—å–∑–æ–≤–∞—Ç–µ–ª–µ–π –∏ –≥–æ—Å—Ç–∏: 9

–í—ã –Ω–µ –º–æ–∂–µ—Ç–µ –Ω–∞—á–∏–Ω–∞—Ç—å —Ç–µ–º—ã–Ω–µ –º–æ–∂–µ—Ç–µ –æ—Ç–≤–µ—á–∞—Ç—å –Ω–∞ —Å–æ–æ–±—â–µ–Ω–∏—è–Ω–µ –º–æ–∂–µ—Ç–µ —Ä–µ–¥–∞–∫—Ç–∏—Ä–æ–≤–∞—Ç—å —Å–≤–æ–∏ —Å–æ–æ–±—â–µ–Ω–∏—è–Ω–µ –º–æ–∂–µ—Ç–µ —É–¥–∞–ª—è—Ç—å —Å–≤–æ–∏ —Å–æ–æ–±—â–µ–Ω–∏—è–Ω–µ –º–æ–∂–µ—Ç–µ –¥–æ–±–∞–≤–ª—è—Ç—å –≤–ª–æ–∂–µ–Ω–∏—è