| –§–æ—Ä—É–º –Ý–∞–¥–∏–æ–ö–æ—Ç https://radiokot.ru/forum/ |

|

| –°—Ö–µ–º–∞ –≤—ã–¥–∞—é—â–∞—è –ø–æ—Å–ª–µ–¥–æ–≤–∞—Ç–µ–ª—å–Ω–æ –Ω–æ–º–µ—Ä https://radiokot.ru/forum/viewtopic.php?f=60&t=150134 |

–°—Ç—Ä–∞–Ω–∏—Ü–∞ 1 –∏–∑ 1 |

| –ê–≤—Ç–æ—Ä: | Dimson12 [ –í—Ç –Ω–æ—è 21, 2017 11:13:39 ] | ||

| –ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: | –°—Ö–µ–º–∞ –≤—ã–¥–∞—é—â–∞—è –ø–æ—Å–ª–µ–¥–æ–≤–∞—Ç–µ–ª—å–Ω–æ –Ω–æ–º–µ—Ä | ||

–î–æ–±—Ä—ã–π –¥–µ–Ω—å, –Ω–µ –º–æ–≥—É –≤—ã–ø–æ–ª–Ω–∏—Ç—å –∑–∞–¥–∞–Ω–∏–µ, —Ç.–∫. —Ç–æ–ª—å–∫–æ –Ω–∞—á–∞–ª –∏–∑—É—á–∞—Ç—å VHDL. –¢—Ä–µ–±—É–µ—Ç—Å—è –ø–æ—Å—Ç—Ä–æ–∏—Ç—å —Å—Ö–µ–º—É, –≤—ã–¥–∞—é—â—É—é –≤ –ø–æ—Å–ª–µ–¥–æ–≤–∞—Ç–µ–ª—å–Ω–æ–º –≤–∏–¥–µ —á–∏—Å–ª–æ 10011 –ø–æ –∑–∞–ø—É—Å–∫–∞—é—â–µ–º—É –æ–¥–∏–Ω–æ—á–Ω–æ–º—É –∏–º–ø—É–ª—å—Å—É –¥–ª–∏—Ç–µ–ª—å–Ω–æ—Å—Ç—å—é 1 –ø–µ—Ä–∏–æ–¥ —Ç–∞–∫—Ç–æ–≤–æ–π —á–∞—Å—Ç–æ—Ç—ã. –Ø –Ω–∞–ø–∏—Å–∞–ª –∫–æ–¥ –∫–∞–∫ —Å–º–æ–≥, –Ω–æ –∫–æ–º–ø–∏–ª—è—Ç–æ—Ä –ø–∏—à–µ—Ç —á—Ç–æ —É –º–µ–Ω—è —Ä–µ–≥–∏—Å—Ç—Ä N(4) –Ω–µ –∏—Å–ø–æ–ª—å–∑—É–µ—Ç—Å—è. –ü–æ–º–æ–≥–∏—Ç–µ —Ä–∞–∑–æ–±—Ä–∞—Ç—å—Å—è, —Ä–∏—Å—É–Ω–æ–∫ –≤—Ä–µ–º–µ–Ω–Ω—ã—Ö –¥–∏–∞–≥—Ä–∞–º–º –ø—Ä–∏–ª–∞–≥–∞—é. –ö–æ–¥ library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity lab4 is Port ( CLK : in STD_LOGIC; CE, SRST : in STD_LOGIC; Q: out STD_LOGIC_VECTOR(4 downto 0)); end lab4; architecture rtl of lab4 is signal N: STD_LOGIC_VECTOR(4 downto 0); begin process(CLK) begin if rising_edge(CLK) then if SRST = '1' then N <= (others => '0'); elsif CE = '1' then if N = "11001" then N <= (others => '0'); else N(0) <= '1'; N <= N(4 downto 1)& N(0); end if; end if; end if; Q <= N; end process; end rtl;

|

|||

| –ê–≤—Ç–æ—Ä: | kolpakchi [ –í—Ç –Ω–æ—è 21, 2017 16:21:19 ] |

| –ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: | Re: –°—Ö–µ–º–∞ –≤—ã–¥–∞—é—â–∞—è –ø–æ—Å–ª–µ–¥–æ–≤–∞—Ç–µ–ª—å–Ω–æ –Ω–æ–º–µ—Ä |

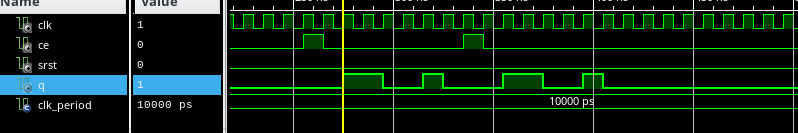

–ö–æ–¥: library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity lab4 is Port ( CLK : in STD_LOGIC; CE, SRST : in STD_LOGIC; Q: out STD_LOGIC); end lab4; architecture rtl of lab4 is signal N: STD_LOGIC_VECTOR(4 downto 0); signal i: integer range 0 to 5; begin process(CLK) begin if rising_edge(CLK) then if SRST = '1' then i<=5; N<="10011"; Q<='0'; else if CE = '1' then i<=0; end if; if i=5 then Q<='0'; else i<=i+1; Q<=N(i); end if; end if; end if; end process; end rtl;  –¢–∞–∫? |

|

| –ê–≤—Ç–æ—Ä: | Dimson12 [ –í—Ç –Ω–æ—è 21, 2017 23:59:30 ] |

| –ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: | Re: –°—Ö–µ–º–∞ –≤—ã–¥–∞—é—â–∞—è –ø–æ—Å–ª–µ–¥–æ–≤–∞—Ç–µ–ª—å–Ω–æ –Ω–æ–º–µ—Ä |

–ë–ª–∞–≥–æ–¥–∞—Ä—é –∑–∞ –æ—Ç–≤–µ—Ç, —ç—Ç–æ —Ç–æ —á—Ç–æ –Ω—É–∂–Ω–æ –î–æ–±–∞–≤–ª–µ–Ω–æ after 21 minute 16 seconds: –£–≤–∞–∂–∞–µ–º—ã–π kolpakchi, –º–æ–≥–ª–∏ –±—ã –≤—ã —Å–∫–∏–Ω—É—Ç—å test bench –∫ –¥–∞–Ω–Ω–æ–º—É –º–æ–¥—É–ª—é ??? |

|

| –ê–≤—Ç–æ—Ä: | kolpakchi [ –°—Ä –Ω–æ—è 22, 2017 15:56:25 ] |

| –ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: | Re: –°—Ö–µ–º–∞ –≤—ã–¥–∞—é—â–∞—è –ø–æ—Å–ª–µ–¥–æ–≤–∞—Ç–µ–ª—å–Ω–æ –Ω–æ–º–µ—Ä |

–í—Å–µ —á—Ç–æ –¥–æ Stimulus process —Å–≥–µ–Ω–µ—Ä–∏–ª ise. –ö–æ–¥: LIBRARY ieee;

USE ieee.std_logic_1164.ALL; ENTITY lab_test IS END lab_test; ARCHITECTURE behavior OF lab_test IS COMPONENT lab4 PORT( CLK : IN std_logic; CE : IN std_logic; SRST : IN std_logic; Q : OUT std_logic ); END COMPONENT; --Inputs signal CLK : std_logic := '0'; signal CE : std_logic := '0'; signal SRST : std_logic := '1'; --Outputs signal Q : std_logic; -- Clock period definitions constant CLK_period : time := 10 ns; BEGIN -- Instantiate the Unit Under Test (UUT) uut: lab4 PORT MAP ( CLK => CLK, CE => CE, SRST => SRST, Q => Q ); -- Clock process definitions CLK_process :process begin CLK <= '0'; wait for CLK_period/2; CLK <= '1'; wait for CLK_period/2; end process; -- Stimulus process stim_proc: process begin -- hold reset state for 100 ns. wait for 100 ns; srst<='0'; wait for CLK_period*10; wait until rising_edge(clk); wait until rising_edge(clk); wait until rising_edge(clk); wait until rising_edge(clk); wait until rising_edge(clk); wait until rising_edge(clk); ce<='1'; wait until rising_edge(clk); ce<='0'; wait until rising_edge(clk); wait until rising_edge(clk); wait until rising_edge(clk); wait until rising_edge(clk); wait until rising_edge(clk); wait until rising_edge(clk); wait until rising_edge(clk); ce<='1'; wait until rising_edge(clk); ce<='0'; wait until rising_edge(clk); -- insert stimulus here wait; end process; END; |

|

| –ê–≤—Ç–æ—Ä: | Dimson12 [ –°—Ä –Ω–æ—è 22, 2017 21:15:04 ] |

| –ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: | Re: –°—Ö–µ–º–∞ –≤—ã–¥–∞—é—â–∞—è –ø–æ—Å–ª–µ–¥–æ–≤–∞—Ç–µ–ª—å–Ω–æ –Ω–æ–º–µ—Ä |

–°–ø–∞—Å–∏–±–æ –∑–∞ –ø–æ–º–æ—â—å! |

|

| –°—Ç—Ä–∞–Ω–∏—Ü–∞ 1 –∏–∑ 1 | –ß–∞—Å–æ–≤–æ–π –ø–æ—è—Å: UTC + 3 —á–∞—Å–∞ |

| Powered by phpBB © 2000, 2002, 2005, 2007 phpBB Group http://www.phpbb.com/ |

|