–ü–æ—á–µ–º—É —É –≤–∞—Å –≤—Ö–æ–¥ KEYs, –∞ –ø—Ä–∏—Å–≤–∞–Ω–∏–≤–∞–Ω–∏–µ –∏–¥—ë—Ç –ø–æ KEY?

–ö–∞–∫–æ–π —Å–∏–≥–Ω–∞–ª –∏–¥—ë—Ç –Ω–∞ –≤—ã–≤–æ–¥ rst_n?

–ß—Ç–æ —Ç–∞–∫–æ–µ –∏ –æ—Ç–∫—É–¥–∞ –≤–∑—è–ª–æ—Å—å LED[0]?

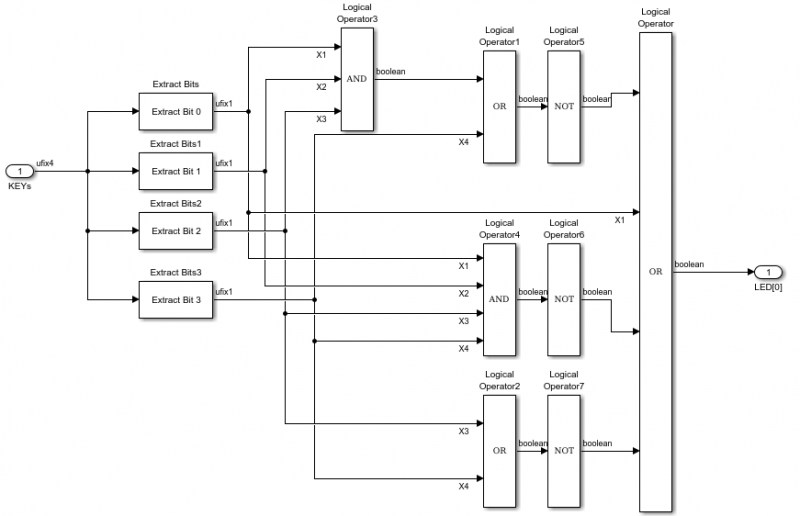

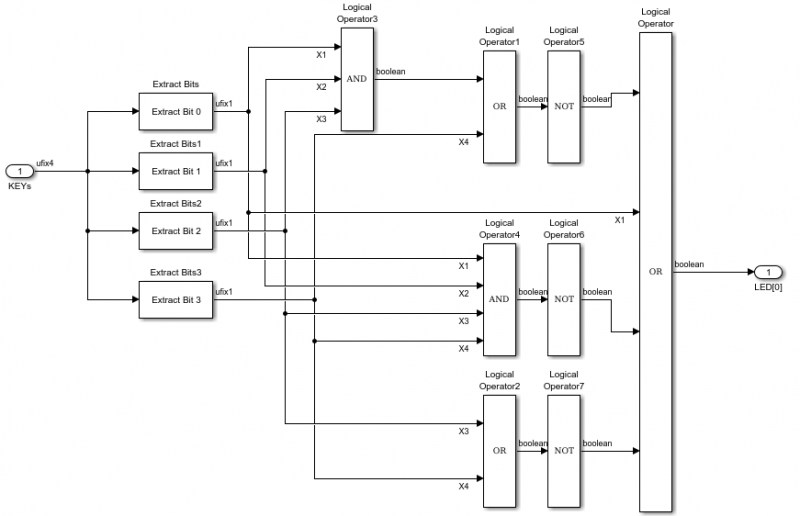

–í –æ–±—â–µ–º, —Å–º–æ—Ç—Ä–∏—Ç–µ —á—Ç–æ –Ω–∞–≥–µ–Ω–µ—Ä–∏–ª –ú–∞—Ç–ª–∞–± –¥–ª—è —Ç–∞–∫–æ–π —Å—Ö–µ–º—ã:

–°–ø–æ–π–ª–µ—Ä

–ö–æ–¥:

// ----------

//

// Generated by MATLAB 9.1 and HDL Coder 3.9

//

//

// -- ----------

// -- Rate and Clocking Details

// -- ----------

// Model base rate: 0

// Target subsystem base rate: 1.#INF

//

// ----------

// ----------

//

// Module: lab3

// Source Path: lab3/lab3

// Hierarchy Level: 0

//

// ----------

`timescale 1 ns / 1 ns

module lab3

(

KEYs,

LED_0

);

input [3:0] KEYs; // ufix4

output LED_0;

wire dtc1; // ufix1

wire X1; // ufix1

wire dtc1_1; // ufix1_E1

wire X2; // ufix1

wire dtc1_2; // ufix1_E2

wire X3; // ufix1

wire Logical_Operator3_out1;

wire X4; // ufix1

wire Logical_Operator1_out1;

wire Logical_Operator5_out1;

wire Logical_Operator4_out1;

wire Logical_Operator6_out1;

wire Logical_Operator2_out1;

wire Logical_Operator7_out1;

wire Logical_Operator_out1;

assign dtc1 = KEYs[0];

assign X1 = dtc1;

assign dtc1_1 = KEYs[1];

assign X2 = dtc1_1;

assign dtc1_2 = KEYs[2];

assign X3 = dtc1_2;

assign Logical_Operator3_out1 = X3 & (X1 & X2);

assign X4 = KEYs[3];

assign Logical_Operator1_out1 = Logical_Operator3_out1 | X4;

assign Logical_Operator5_out1 = ~ Logical_Operator1_out1;

assign Logical_Operator4_out1 = X4 & (X3 & (X1 & X2));

assign Logical_Operator6_out1 = ~ Logical_Operator4_out1;

assign Logical_Operator2_out1 = X3 | X4;

assign Logical_Operator7_out1 = ~ Logical_Operator2_out1;

assign Logical_Operator_out1 = Logical_Operator7_out1 | (Logical_Operator6_out1 | (Logical_Operator5_out1 | X1));

assign LED_0 = Logical_Operator_out1;

endmodule // lab3