|

–§–æ—Ä—É–º –Ý–∞–¥–∏–æ–ö–æ—Ç • –ü—Ä–æ—Å–º–æ—Ç—Ä —Ç–µ–º—ã - EEPROM 24LC04B

–°–æ–æ–±—â–µ–Ω–∏—è –±–µ–∑ –æ—Ç–≤–µ—Ç–æ–≤ | –ê–∫—Ç–∏–≤–Ω—ã–µ —Ç–µ–º—ã

|

–°—Ç—Ä–∞–Ω–∏—Ü–∞ 1 –∏–∑ 2

|

[ –°–æ–æ–±—â–µ–Ω–∏–π: 23 ] |

, |

| –ê–≤—Ç–æ—Ä |

–°–æ–æ–±—â–µ–Ω–∏–µ |

Trioni

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –°—Ä –¥–µ–∫ 04, 2024 19:39:14 |

|

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°—Ä –¥–µ–∫ 04, 2024 19:24:18

–°–æ–æ–±—â–µ–Ω–∏–π: 8

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

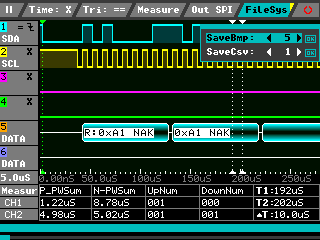

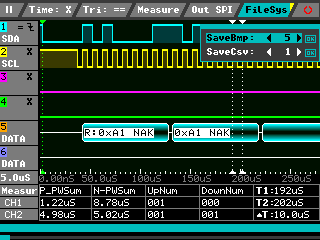

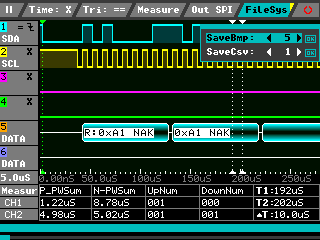

–î–æ–±—Ä–æ–≥–æ –¥–Ω—è. –ù–∞—á–∞–ª –∏–∑—É—á–∞—Ç—å i2c –∏ –Ω–∞ –æ—Ç–ª–∞–¥–∫–µ —É—Å—Ç–∞–Ω–æ–≤–ª–µ–Ω–∞ EEPROM 24LC04B. –°—Ç–æ–ª–∫–Ω—É–ª—Å—è —Å —Ç–µ–º —á—Ç–æ –Ω–µ –ø–æ–ª—É—á–∞—é –æ—Ç –Ω–µ—ë –±–∏—Ç ACK. –ü–æ —Å–∫–æ–ª—å–∫—É —Ä–∞–±–æ—Ç–∞—é –≤ –ø–µ—Ä–≤—ã–π —Ä–∞–∑ —Ç–æ –Ω–µ –º–æ–≥—É –ø–æ–Ω—è—Ç—å –Ω–µ –∏—Å–ø—Ä–∞–≤–Ω–∞ –∂–µ —Å–∞–º–∞ –º–∏–∫—Ä–æ—Å—Ö–µ–º–∞/–æ—Ç–ª–∞–¥–∫–∞ –∏–ª–∏ —è –≤—ã—Å—Ç–∞–≤–∏–ª –Ω–µ –≤–µ—Ä–Ω—ã–µ –∞–¥—Ä–µ—Å–∞/—Ç–∞–π–º–∏–Ω–≥–∏ –¥–∞—Ç–∞—à–∏—Ç: https://static.chipdip.ru/lib/938/DOC011938526.pdf–ö–∞—Ä—Ç–∏–Ω–∫–∞ —Å –∞–Ω–∞–ª–∏–∑–∞—Ç–æ—Ä–∞:  (–æ—Ç–ª–∞–¥–∫–∞ AX309, SPARTAN6, –≤—ã—Ö–æ–¥—ã –≤—Ä–æ–¥–µ –≤—ã—Å—Ç–∞–≤–∏–ª –∫–æ—Ä—Ä–µ–∫—Ç–Ω–æ: SDA P12, SCL N12)

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

|

–Ý–µ–∫–ª–∞–º–∞

|

|

|

|

|

|

|

|

|

BOB51

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –°—Ä –¥–µ–∫ 04, 2024 22:43:09 |

|

| –î—Ä—É–≥ –ö–æ—Ç–∞ |

|

–ö–∞—Ä–º–∞: 94

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 1466

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Ç –º–∞—Ä 16, 2010 22:02:27

–°–æ–æ–±—â–µ–Ω–∏–π: 15038

–û—Ç–∫—É–¥–∞: –î–û–ù–ï–¶–ö

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

–ò–ª–∏ –æ—à–∏–±–∫–∞ –≤ –ø—Ä–æ–≥—Ä–∞–º–º–µ...

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

|

–Ý–µ–∫–ª–∞–º–∞

|

|

|

|

|

|

|

|

|

Martian

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –°—Ä –¥–µ–∫ 04, 2024 22:52:35 |

|

–ö–∞—Ä–º–∞: 68

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 1958

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°–± –¥–µ–∫ 18, 2021 19:25:32

–°–æ–æ–±—â–µ–Ω–∏–π: 12867

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

|

–î–∞, –Ω–æ —ç—Ç–æ –±—ã–ª–æ –±—ã –ª—É—á—à–µ –≤–∏–¥–Ω–æ –æ—Å—Ü–∏–ª–ª–æ–≥—Ä–∞—Ñ–æ–º, –µ—Å–ª–∏ –∏–º–µ–µ—Ç—Å—è –≤–≤–∏–¥—É, —á—Ç–æ —É –º–∞—Å—Ç–µ—Ä–∞ –ø–∏–Ω –æ—Å—Ç–∞–ª—Å—è –≤—ã—Ö–æ–¥–æ–º —Å –≤—ã—Å–æ–∫–∏–º —É—Ä–æ–≤–Ω–µ–º.

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

Trioni

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ß—Ç –¥–µ–∫ 05, 2024 04:32:27 |

|

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°—Ä –¥–µ–∫ 04, 2024 19:24:18

–°–æ–æ–±—â–µ–Ω–∏–π: 8

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

–ò–ª–∏ –æ—à–∏–±–∫–∞ –≤ –ø—Ä–æ–≥—Ä–∞–º–º–µ...  –ê —á—Ç–æ –º–æ–∂–µ—Ç –Ω–µ —Ç–∞–∫ –±—ã—Ç—å? –ü–æ —Å–∏–º—É–ª—è—Ü–∏–∏ –≤—ã—Ö–æ–¥ —É—Ö–æ–¥–∏—Ç –≤ 'z' , –¥–∞ –∏ –∫–∞–∫ —è –ø–æ–Ω—è–ª slave –∂–µ –º–æ–∂–µ—Ç –≤—Å—ë —Ä–∞–≤–Ω–æ –ø—Ä–æ—Å—Ç–æ –Ω–∞ –∑–µ–º–ª—é —É—Ä–æ–Ω–∏—Ç—å –ª–∏–Ω–∏—é, –¥–∞–∂–µ –µ—Å–ª–∏ –º–∞—Å—Ç–µ—Ä –æ—Å—Ç–∞–≤–∏—Ç –≤—ã—Å–æ–∫–∏–π —É—Ä–æ–≤–µ–Ω—å. –û—Å—Ü–∏–ª–æ–≥–æ–∞—Ñ–∞ –Ω–µ—Ç—É –ø—Ä–æ–≤–µ—Ä–∏—Ç—å. –î–µ–ª–∞–ª –Ω–∞ –∞—Ä–¥—É–∏–Ω–∫–µ i2c —Å–∫–∞–Ω–µ—Ä –∏ –ø–æ–ª—É—á–∞–ª –ø—Ä–∏–º–µ—Ä–Ω–æ —Ç–∞–∫—É—é –∂–µ –∫–∞—Ä—Ç–∏–Ω—É, –∏–∑ –∑–∞ —á–µ–≥–æ —Å–µ–π—á–∞—Å –≤ —Å—Ç—É–ø–æ—Ä–µ, –≤–µ–¥—å –ø–æ –º–æ–µ–π –ª–æ–≥–∏–∫–µ –≤—Å—ë –¥–æ–ª–∂–Ω–æ –±—ã–ª–æ —Ä–∞–±–æ—Ç–∞—Ç—å...

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

shonty

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ß—Ç –¥–µ–∫ 05, 2024 05:58:08 |

|

| –ú—É—á–∏—Ç–µ–ª—å –º–∏–∫—Ä–æ—Å—Ö–µ–º |

|

–ö–∞—Ä–º–∞: 1

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 38

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°—Ä —è–Ω–≤ 11, 2012 18:20:26

–°–æ–æ–±—â–µ–Ω–∏–π: 473

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

Trioni –ø–∏—Å–∞–ª(–∞): –ê —á—Ç–æ –º–æ–∂–µ—Ç –Ω–µ —Ç–∞–∫ –±—ã—Ç—å? –í—Å—ë —á—Ç–æ —É–≥–æ–¥–Ω–æ. –ú—ã –¥–∞–∂–µ –Ω–µ –∑–Ω–∞–µ–º, —á—Ç–æ —É –≤–∞—Å "—Ç–∞–∫")) Trioni –ø–∏—Å–∞–ª(–∞): –≤–µ–¥—å –ø–æ –º–æ–µ–π –ª–æ–≥–∏–∫–µ –≤—Å—ë –¥–æ–ª–∂–Ω–æ –±—ã–ª–æ —Ä–∞–±–æ—Ç–∞—Ç—å.. –ª–æ–≥–∏–∫–∞ —Ç—É—Ç –Ω–∏ –ø—Ä–∏ —á—ë–º. –í—ã –ª—É—á—à–µ –ø–æ—Å–ª–µ–¥–æ–≤–∞—Ç–µ–ª—å–Ω–æ—Å—Ç—å –≤–∞—à–∏—Ö –¥–µ–π—Å—Ç–≤–∏–π –æ–ø–∏—à–∏—Ç–µ, –Ω–∞—á–∏–Ω–∞—è —Å –ø–µ—Ä–≤–æ–≥–æ –∏ –¥–æ —Ç–æ–≥–æ –∫–∞–∫ –æ–∂–∏–¥–∞–µ—Ç–µ ACK. Trioni –ø–∏—Å–∞–ª(–∞): –∏–ª–∏ —è –≤—ã—Å—Ç–∞–≤–∏–ª –Ω–µ –≤–µ—Ä–Ω—ã–µ –∞–¥—Ä–µ—Å–∞/—Ç–∞–π–º–∏–Ω–≥–∏ –ò –ø—Ä–æ —ç—Ç–æ —Ä–∞—Å—Å–∫–∞–∂–∏—Ç–µ. –ö–∞–∫—É—é —Å–∫–æ—Ä–æ—Å—Ç—å –∑–∞–¥–∞—ë—Ç–µ?

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

|

–Ý–µ–∫–ª–∞–º–∞

|

|

|

|

|

|

|

|

|

Martian

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ß—Ç –¥–µ–∫ 05, 2024 06:43:37 |

|

–ö–∞—Ä–º–∞: 68

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 1958

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°–± –¥–µ–∫ 18, 2021 19:25:32

–°–æ–æ–±—â–µ–Ω–∏–π: 12867

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

–¥–∞ –∏ –∫–∞–∫ —è –ø–æ–Ω—è–ª slave –∂–µ –º–æ–∂–µ—Ç –≤—Å—ë —Ä–∞–≤–Ω–æ –ø—Ä–æ—Å—Ç–æ –Ω–∞ –∑–µ–º–ª—é —É—Ä–æ–Ω–∏—Ç—å –ª–∏–Ω–∏—é, –¥–∞–∂–µ –µ—Å–ª–∏ –º–∞—Å—Ç–µ—Ä –æ—Å—Ç–∞–≤–∏—Ç –≤—ã—Å–æ–∫–∏–π —É—Ä–æ–≤–µ–Ω—å. –ö–∞–∫–∏–º –æ–±—Ä–∞–∑–æ–º? –°–æ–ø—Ä–æ—Ç–∏–≤–ª–µ–Ω–∏–µ –≤–µ—Ä—Ö–Ω–µ–≥–æ –∫–ª—é—á–∞ master –ø—Ä–æ—Ç–∏–≤ —Å–æ–ø—Ä–æ—Ç–∏–≤–ª–µ–Ω–∏—è –Ω–∏–∂–Ω–µ–≥–æ –∫–ª—é—á–∞ slave. –ß—Ç–æ –±—É–¥–µ—Ç –ø–æ—Å–µ—Ä–µ–¥–∏–Ω–µ? –ë—É–¥–µ—Ç —Ö—Ä–µ–Ω—å, –∏–Ω—Ç–µ—Ä–ø—Ä–µ—Ç–∞—Ü–∏—è –∫–æ—Ç–æ—Ä–æ–π –ª–æ–≥–∏—á–µ—Å–∫–∏–º –∞–Ω–∞–ª–∏–∑–∞—Ç–æ—Ä–æ–º –Ω–µ–ø—Ä–µ–¥—Å–∫–∞–∑—É–µ–º–∞. Trioni –ø–∏—Å–∞–ª(–∞): –ü–æ —Å–∏–º—É–ª—è—Ü–∏–∏ –≤—ã—Ö–æ–¥ —É—Ö–æ–¥–∏—Ç –≤ 'z' —Ç–∞–∫ —ç—Ç–æ —Å–∏–º—É–ª—è—Ü–∏—è –∏–ª–∏ —Ä–µ–∞–ª—å–Ω–æ–µ —É—Å—Ç—Ä–æ–π—Å—Ç–≤–æ?

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

|

–Ý–µ–∫–ª–∞–º–∞

|

|

|

|

|

|

|

|

|

Trioni

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ß—Ç –¥–µ–∫ 05, 2024 07:32:51 |

|

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°—Ä –¥–µ–∫ 04, 2024 19:24:18

–°–æ–æ–±—â–µ–Ω–∏–π: 8

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

–¥–∞ –∏ –∫–∞–∫ —è –ø–æ–Ω—è–ª slave –∂–µ –º–æ–∂–µ—Ç –≤—Å—ë —Ä–∞–≤–Ω–æ –ø—Ä–æ—Å—Ç–æ –Ω–∞ –∑–µ–º–ª—é —É—Ä–æ–Ω–∏—Ç—å –ª–∏–Ω–∏—é, –¥–∞–∂–µ –µ—Å–ª–∏ –º–∞—Å—Ç–µ—Ä –æ—Å—Ç–∞–≤–∏—Ç –≤—ã—Å–æ–∫–∏–π —É—Ä–æ–≤–µ–Ω—å. –ö–∞–∫–∏–º –æ–±—Ä–∞–∑–æ–º? –°–æ–ø—Ä–æ—Ç–∏–≤–ª–µ–Ω–∏–µ –≤–µ—Ä—Ö–Ω–µ–≥–æ –∫–ª—é—á–∞ master –ø—Ä–æ—Ç–∏–≤ —Å–æ–ø—Ä–æ—Ç–∏–≤–ª–µ–Ω–∏—è –Ω–∏–∂–Ω–µ–≥–æ –∫–ª—é—á–∞ slave. –ß—Ç–æ –±—É–¥–µ—Ç –ø–æ—Å–µ—Ä–µ–¥–∏–Ω–µ? –ë—É–¥–µ—Ç —Ö—Ä–µ–Ω—å, –∏–Ω—Ç–µ—Ä–ø—Ä–µ—Ç–∞—Ü–∏—è –∫–æ—Ç–æ—Ä–æ–π –ª–æ–≥–∏—á–µ—Å–∫–∏–º –∞–Ω–∞–ª–∏–∑–∞—Ç–æ—Ä–æ–º –Ω–µ–ø—Ä–µ–¥—Å–∫–∞–∑—É–µ–º–∞. Trioni –ø–∏—Å–∞–ª(–∞): –ü–æ —Å–∏–º—É–ª—è—Ü–∏–∏ –≤—ã—Ö–æ–¥ —É—Ö–æ–¥–∏—Ç –≤ 'z' —Ç–∞–∫ —ç—Ç–æ —Å–∏–º—É–ª—è—Ü–∏—è –∏–ª–∏ —Ä–µ–∞–ª—å–Ω–æ–µ —É—Å—Ç—Ä–æ–π—Å—Ç–≤–æ? 1) –î—É–º–∞–ª –±—É–¥–µ—Ç –ø—Ä–æ—Å—Ç–æ '–∫–∑' —á–µ—Ä–µ–∑ –ø–æ–¥—Ç—è–≥–∏–≤–∞—é—â–∏–π —Ä–µ–∑–∏—Å—Ç–æ—Ä –∏ —Ç—Ä–∞–Ω–∑–∏—Å—Ç–æ—Ä slave => –ª–∏–Ω–∏—è –ø—Ä–æ—Å—Ç–æ –ª–µ–∂–∏—Ç –≤ –Ω—É–ª–µ 2) —É—Å—Ç—Ä–æ–π—Å—Ç–≤–æ. (–ö–æ–¥ –∏ —Å–∏–º—É–ª—è—Ü–∏—é —Å–∫–∏–Ω—É –ø–æ—Å–ª–µ —Ä–∞–±–æ—Ç—ã —É–∂–µ —Ç–æ–ª—å–∫–æ. –ù–µ –¥—É–º–∞–ª —á—Ç–æ –¥–æ–π–¥—ë—Ç)

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

shonty

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ß—Ç –¥–µ–∫ 05, 2024 11:11:56 |

|

| –ú—É—á–∏—Ç–µ–ª—å –º–∏–∫—Ä–æ—Å—Ö–µ–º |

|

–ö–∞—Ä–º–∞: 1

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 38

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°—Ä —è–Ω–≤ 11, 2012 18:20:26

–°–æ–æ–±—â–µ–Ω–∏–π: 473

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

Trioni –ø–∏—Å–∞–ª(–∞): (–ö–æ–¥ –∏ —Å–∏–º—É–ª—è—Ü–∏—é —Å–∫–∏–Ω—É –ø–æ—Å–ª–µ —Ä–∞–±–æ—Ç—ã —É–∂–µ —Ç–æ–ª—å–∫–æ. –ù–µ –¥—É–º–∞–ª —á—Ç–æ –¥–æ–π–¥—ë—Ç) –ö–æ–¥ –≤—Ç–æ—Ä–∏—á–µ–Ω. –≠—Ç–æ –≤—Å–µ–≥–æ –Ω–∞–≤—Å–µ–≥–æ —Ä–µ–∞–ª–∏–∑–∞—Ü–∏—è –∞–ª–≥–æ—Ä–∏—Ç–º–∞. –ê –≤—ã —Å–ª–æ–≤–∞–º–∏ –Ω–µ –º–æ–∂–µ—Ç–µ –≤—ã—Ä–∞–∑–∏—Ç—å, —á—Ç–æ –≤—ã –¥–µ–ª–∞–µ—Ç–µ –∏ –≤ –∫–∞–∫–æ–π –ø–æ—Å–ª–µ–¥–æ–≤–∞—Ç–µ–ª—å–Ω–æ—Å—Ç–∏. Trioni –ø–∏—Å–∞–ª(–∞): –î–µ–ª–∞–ª –Ω–∞ –∞—Ä–¥—É–∏–Ω–∫–µ i2c —Å–∫–∞–Ω–µ—Ä –∏ –ø–æ–ª—É—á–∞–ª –ø—Ä–∏–º–µ—Ä–Ω–æ —Ç–∞–∫—É—é –∂–µ –∫–∞—Ä—Ç–∏–Ω—É, –∏–∑ –∑–∞ —á–µ–≥–æ —Å–µ–π—á–∞—Å –≤ —Å—Ç—É–ø–æ—Ä–µ, –í–æ–∑–º–æ–∂–Ω–æ –ø–æ —ç—Ç–æ–º—É —Ä–µ–∑—É–ª—å—Ç–∞—Ç –∏ —Å—Ç–∞–±–∏–ª–µ–Ω

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

jcxz

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –¥–µ–∫ 06, 2024 00:36:50 |

|

| –≠—Ç–æ –Ω–µ —Ö–≤–æ—Å—Ç, —ç—Ç–æ –∞–Ω—Ç–µ–Ω–Ω–∞ |

–ö–∞—Ä–º–∞: -10

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 171

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Ç –∞–≤–≥ 15, 2017 10:51:13

–°–æ–æ–±—â–µ–Ω–∏–π: 1482

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

–ö–∞—Ä—Ç–∏–Ω–∫–∞ —Å –∞–Ω–∞–ª–∏–∑–∞—Ç–æ—Ä–∞:  –ö–∞–∫–æ–µ-—Ç–æ —Å—Ç—Ä–∞–Ω–Ω–æ –¥–ª–∏–Ω–Ω–æ–µ —Å—Ç–∞—Ä—Ç-—É—Å–ª–æ–≤–∏–µ....  –•–æ—Ç—è –∫–æ–Ω–µ—á–Ω–æ –∫—Ä–∏–º–∏–Ω–∞–ª–∞ –∑–¥–µ—Å—å –Ω–µ—Ç. –Ý–∞–∑—Ä–µ—à–µ–Ω–∏–µ –∫–∞—Ä—Ç–∏–Ω–∫–∏ —Ç–∞–∫–æ–µ, —á—Ç–æ –ø–æ–Ω—è—Ç—å –ø–æ –Ω–µ–π —á—Ç–æ-–ª–∏–±–æ —Ç—Ä—É–¥–Ω–æ. –ù–∞–ø—Ä–∏–º–µ—Ä - –Ω–µ –ø—Ä–æ–∏—Å—Ö–æ–¥—è—Ç –ª–∏ —Ñ—Ä–æ–Ω—Ç—ã –ø–æ SDA –∏ SCL –æ–¥–Ω–æ–≤—Ä–µ–º–µ–Ω–Ω–æ? –≠—Ç–æ –º–æ–∂–µ—Ç –≤–æ—Å–ø—Ä–∏–Ω–∏–º–∞—Ç—å—Å—è –≤–µ–¥–æ–º—ã–º –∫–∞–∫ —Å—Ç–æ–ø-—É—Å–ª–æ–≤–∏–µ –∏ —Ç–æ–≥–¥–∞ –æ–Ω –∫–æ–Ω–µ—á–Ω–æ –Ω–µ —Å—Ç–∞–Ω–µ—Ç –≤—ã—Å—Ç–∞–≤–ª—è—Ç—å ACK. –í–Ω—É—Ç—Ä–∏ –≤–µ–¥–æ–º–æ–≥–æ —Ñ—Ä–æ–Ω—Ç –ø–æ SDA –º–æ–∂–µ—Ç —á—É—Ç—å –∑–∞–ø–æ–∑–¥–∞—Ç—å, –∏ —ç—Ç–æ –±—É–¥–µ—Ç –≤—ã–≥–ª—è–¥–µ—Ç—å –¥–ª—è –Ω–µ–≥–æ –∫–∞–∫ –°–¢–û–ü.

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

|

–Ý–µ–∫–ª–∞–º–∞

|

|

|

|

|

|

|

|

|

Trioni

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –¥–µ–∫ 06, 2024 14:39:36 |

|

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°—Ä –¥–µ–∫ 04, 2024 19:24:18

–°–æ–æ–±—â–µ–Ω–∏–π: 8

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

–ö–∞–∫–æ–µ-—Ç–æ —Å—Ç—Ä–∞–Ω–Ω–æ –¥–ª–∏–Ω–Ω–æ–µ —Å—Ç–∞—Ä—Ç-—É—Å–ª–æ–≤–∏–µ....  –•–æ—Ç—è –∫–æ–Ω–µ—á–Ω–æ –∫—Ä–∏–º–∏–Ω–∞–ª–∞ –∑–¥–µ—Å—å –Ω–µ—Ç. –ò–≥—Ä–∞–ª—Å—è –ø—Ä–æ—Å—Ç–æ —Å —Ä–∞–∑–Ω—ã–º–∏ —Ç–∞–π–º–∏–Ω–≥–∞–º–∏, –≤ —Ç–æ–º —á–∏—Å–ª–µ –¥–∞–≤–∞—è –±–æ–ª—å—à–µ –≤—Ä–µ–º–µ–Ω–∏ –Ω–∞ —Å—Ç–∞—Ä—Ç. –Ý–∞–∑—Ä–µ—à–µ–Ω–∏–µ –∫–∞—Ä—Ç–∏–Ω–∫–∏ —Ç–∞–∫–æ–µ, —á—Ç–æ –ø–æ–Ω—è—Ç—å –ø–æ –Ω–µ–π —á—Ç–æ-–ª–∏–±–æ —Ç—Ä—É–¥–Ω–æ. –ù–∞–ø—Ä–∏–º–µ—Ä - –Ω–µ –ø—Ä–æ–∏—Å—Ö–æ–¥—è—Ç –ª–∏ —Ñ—Ä–æ–Ω—Ç—ã –ø–æ SDA –∏ SCL –æ–¥–Ω–æ–≤—Ä–µ–º–µ–Ω–Ω–æ? –≠—Ç–æ –º–æ–∂–µ—Ç –≤–æ—Å–ø—Ä–∏–Ω–∏–º–∞—Ç—å—Å—è –≤–µ–¥–æ–º—ã–º –∫–∞–∫ —Å—Ç–æ–ø-—É—Å–ª–æ–≤–∏–µ –∏ —Ç–æ–≥–¥–∞ –æ–Ω –∫–æ–Ω–µ—á–Ω–æ –Ω–µ —Å—Ç–∞–Ω–µ—Ç –≤—ã—Å—Ç–∞–≤–ª—è—Ç—å ACK. –í–Ω—É—Ç—Ä–∏ –≤–µ–¥–æ–º–æ–≥–æ —Ñ—Ä–æ–Ω—Ç –ø–æ SDA –º–æ–∂–µ—Ç —á—É—Ç—å –∑–∞–ø–æ–∑–¥–∞—Ç—å, –∏ —ç—Ç–æ –±—É–¥–µ—Ç –≤—ã–≥–ª—è–¥–µ—Ç—å –¥–ª—è –Ω–µ–≥–æ –∫–∞–∫ –°–¢–û–ü. –°–∫—Ä–∏–Ω —Å–∏–º—É–ª—è—Ü–∏–∏, –≤—Ä–æ–¥–µ –Ω–∞–ª–æ–∂–µ–Ω–∏–π –Ω–µ—Ç, –æ–¥–∏–Ω —Ç–∞–∫—Ç scl —Ä–∞–∑–±–∏–≤–∞–ª –Ω–∞ 4 –º–∏–Ω–∏-—Ç–∞–∫—Ç–∫–∞

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

Martian

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –¥–µ–∫ 06, 2024 16:39:10 |

|

–ö–∞—Ä–º–∞: 68

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 1958

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°–± –¥–µ–∫ 18, 2021 19:25:32

–°–æ–æ–±—â–µ–Ω–∏–π: 12867

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

|

–ù–µ –ø–æ–Ω–∏–º–∞—é. –¢–æ —É—Å—Ç—Ä–æ–π—Å—Ç–≤–æ, —Ç–æ –æ–ø—è—Ç—å —Å–∏–º—É–ª—è—Ü–∏—è... –í—ã —É–∂ –æ–ø—Ä–µ–¥–µ–ª–∏—Ç–µ—Å—å, –≥–¥–µ –Ω–µ —Ä–∞–±–æ—Ç–∞–µ—Ç.

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

Trioni

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –¥–µ–∫ 06, 2024 17:13:01 |

|

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°—Ä –¥–µ–∫ 04, 2024 19:24:18

–°–æ–æ–±—â–µ–Ω–∏–π: 8

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

|

–ò–∑–Ω–∞—á–∞–ª—å–Ω–æ –∂–µ —Å–∫–∞–∑–∞–ª: –Ω–∞ —É—Å—Ç—Ä–æ–π—Å—Ç–≤–µ –Ω–µ –ø–æ–ª—É—á–∞—é –±–∏—Ç ACK.

–°–∏–º—É–ª—è—Ü–∏—é —Å–∫–∏–Ω—É–ª –ø—Ä–æ—Å—Ç–æ –≤–º–µ—Å—Ç–æ —Å–æ—Ç–µ–Ω —Å—Ç—Ä–æ—á–µ–∫ –∫–æ–¥–∞, —è—Å–Ω–æ–µ –¥–µ–ª–æ —Ç–∞–º –Ω–∏–∫–∞–∫–æ–≥–æ –æ—Ç–≤–µ—Ç–Ω–æ–≥–æ —Å–∏–≥–Ω–∞–ª–∞ –Ω–µ –±—É–¥–µ—Ç.

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

veso74

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –¥–µ–∫ 06, 2024 17:23:01 |

|

| –ì–æ–≤–æ—Ä—è—â–∏–π —Å —Ç–µ–∫—Å—Ç–æ–ª–∏—Ç–æ–º |

–ö–∞—Ä–º–∞: 25

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 450

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°–± –º–∞–π 05, 2012 20:24:52

–°–æ–æ–±—â–µ–Ω–∏–π: 1612

–û—Ç–∫—É–¥–∞: KN34PC, –ë–æ–ª–≥–∞—Ä–∏—è

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

–ß–∏—Ç–∞–µ—Ç–µ –∏–ª–∏ –ø–∏—à–µ—Ç–µ –≤ EEPROM? –ö–∞–∫–∞—è —á–∞—Å—Ç–æ—Ç–∞ SCL? –ü—Ä–æ–≥—Ä–∞–º–º–Ω–æ–π —Ä–µ–∞–ª–∏–∑–∞—Ü–∏–µ–π I2C –∏–ª–∏ –∞–ø–ø–∞—Ä–∞—Ç–Ω–æ–π? –Ø–≤–ª—è—é—Ç—Å—è –ª–∏ –≤—ã–≤–æ–¥—ã SDA –∏ SCL –æ—Ç–∫—Ä—ã—Ç—ã–º —Å—Ç–æ–∫–æ–º? –ï—Å—Ç—å –ø–æ–¥—Ç—è–≥–∏–≤–∞—é—â–∏–µ —Ä–µ–∑–∏—Å—Ç–æ—Ä—ã? –ö—É–¥–∞ –æ–Ω–∏ –≤–∫–ª—é—á–µ–Ω—ã –∏ –∫–∞–∫–æ–µ –∑–Ω–∞—á–µ–Ω–∏–µ? –§–æ—Ç–æ —ç–∫—Å–ø–µ—Ä–∏–º–µ–Ω—Ç–∞–ª—å–Ω–æ–π —É—Å—Ç–∞–Ω–æ–≤–∫–∏? –•–æ—Ç—è –±—ã —Ñ—Ä–∞–≥–º–µ–Ω—Ç —Ä–µ–∞–ª–∏–∑–∞—Ü–∏–∏ I2C? –ù–∞–ø—Ä. –¥–∞–Ω–Ω—ã–µ –Ω–∏–∂–µ –≤–∑—è—Ç—ã –∏–∑ –ª–æ–≥. –∞–Ω–∞–ª–∏–∑–∞—Ç–æ—Ä–∞. –î–µ—Ç–∞–ª–∏ –∫–æ–º—É–Ω–∏–∫–∞—Ü–∏–∏ –≤–∏–¥–Ω—ã, –∞ —Ç–∞–∫–∂–µ —Ä–∞—Å–ø–æ–∑–Ω–∞–≤–∞–Ω–∏–µ —Ñ—É–Ω–∫—Ü–∏–π –≤ I2C (–∫ PCF8574). –í –≤–∞—à–µ–º —Å–ª—É—á–∞–µ —á—Ç–æ –µ—Å—Ç—å —á—Ç–æ, —Ç–æ–ª—å–∫–æ –¥–æ–≥–∞–¥—ã–≤–∞–µ–º—Å—è –∏ –ø—Ä–µ–¥–ø–æ–ª–∞–≥–∞–µ–º.  ,

–ü–æ—Å–ª–µ–¥–Ω–∏–π —Ä–∞–∑ —Ä–µ–¥–∞–∫—Ç–∏—Ä–æ–≤–∞–ª–æ—Å—å veso74 –°–± –¥–µ–∫ 07, 2024 11:10:32, –≤—Å–µ–≥–æ —Ä–µ–¥–∞–∫—Ç–∏—Ä–æ–≤–∞–ª–æ—Å—å 1 —Ä–∞–∑.

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

Martian

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –¥–µ–∫ 06, 2024 18:18:55 |

|

–ö–∞—Ä–º–∞: 68

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 1958

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°–± –¥–µ–∫ 18, 2021 19:25:32

–°–æ–æ–±—â–µ–Ω–∏–π: 12867

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

–ò–∑–Ω–∞—á–∞–ª—å–Ω–æ –∂–µ —Å–∫–∞–∑–∞–ª: –Ω–∞ —É—Å—Ç—Ä–æ–π—Å—Ç–≤–µ –Ω–µ –ø–æ–ª—É—á–∞—é –±–∏—Ç ACK.

–°–∏–º—É–ª—è—Ü–∏—é —Å–∫–∏–Ω—É–ª –ø—Ä–æ—Å—Ç–æ –≤–º–µ—Å—Ç–æ —Å–æ—Ç–µ–Ω —Å—Ç—Ä–æ—á–µ–∫ –∫–æ–¥–∞, —è—Å–Ω–æ–µ –¥–µ–ª–æ —Ç–∞–º –Ω–∏–∫–∞–∫–æ–≥–æ –æ—Ç–≤–µ—Ç–Ω–æ–≥–æ —Å–∏–≥–Ω–∞–ª–∞ –Ω–µ –±—É–¥–µ—Ç. –Ø—Å–Ω–æ. –ù—É, —à–ª–∏—Ç–µ –¥–∞–ª—å—à–µ –∫—Ä–∞—Å–∏–≤—ã–µ –∫–∞—Ä—Ç–∏–Ω–∫–∏.

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

jcxz

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç –¥–µ–∫ 06, 2024 22:22:12 |

|

| –≠—Ç–æ –Ω–µ —Ö–≤–æ—Å—Ç, —ç—Ç–æ –∞–Ω—Ç–µ–Ω–Ω–∞ |

–ö–∞—Ä–º–∞: -10

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 171

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Ç –∞–≤–≥ 15, 2017 10:51:13

–°–æ–æ–±—â–µ–Ω–∏–π: 1482

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 5

|

–°–∫—Ä–∏–Ω —Å–∏–º—É–ª—è—Ü–∏–∏, –≤—Ä–æ–¥–µ –Ω–∞–ª–æ–∂–µ–Ω–∏–π –Ω–µ—Ç, –æ–¥–∏–Ω —Ç–∞–∫—Ç scl —Ä–∞–∑–±–∏–≤–∞–ª –Ω–∞ 4 –º–∏–Ω–∏-—Ç–∞–∫—Ç–∫–∞  –ù–µ –ø–æ–Ω—è–ª - –∞ –∫–∞–∫–æ–µ –æ—Ç–Ω–æ—à–µ–Ω–∏–µ –∏–º–µ–µ—Ç —ç—Ç–∞ –∫–∞—Ä—Ç–∏–Ω–∫–∞ –∫ —Å–∫—Ä–∏–Ω—à–æ—Ç—É –æ—Å—Ü–∏–ª–ª–æ–≥—Ä–∞—Ñ–∞ –∏–∑ –ø–µ—Ä–≤–æ–≥–æ –ø–æ—Å—Ç–∞? –¢–∞–º —Å–æ–≤–µ—Ä—à–µ–Ω–Ω–æ —è—Å–Ω–æ –≤–∏–¥–Ω—ã —Å–æ–≤–µ—Ä—à–µ–Ω–Ω–æ –¥—Ä—É–≥–∏–µ –≤—Ä–µ–º–µ–Ω–Ω—ã–µ —Å–æ–æ—Ç–Ω–æ—à–µ–Ω–∏—è. –ö —Ç–æ–º—É-–∂–µ - –¥–∞–∂–µ –ø–æ —ç—Ç–æ–π –∫–∞—Ä—Ç–∏–Ω–∫–µ - —Ä–∞–∑–≤–µ –Ω–µ –≤–∏–¥–∏—Ç–µ —Å—Ç—Ä–∞–Ω–Ω–æ—Å—Ç–µ–π? –ú–µ–∂–¥—É —Ä–∏—Å–∫–∞–º–∏ "1 –º–∫—Å" –∏ "19 –º–∫—Å" –ø–æ–ø–∞–¥–∞–µ—Ç –ø—Ä–∏–º–µ—Ä–Ω–æ ~8.5 –ø–µ—Ä–∏–æ–¥–æ–≤ SCLK. –¢.–µ. = 8.5/18e-6 = ~472 –∫–ì—Ü. –ü—Ä–∏ —Ç–æ–º —á—Ç–æ –ø–æ –¥–∞—Ç–∞—à–∏—Ç—É 24LC04B —É–º–µ–µ—Ç –º–∞–∫—Å–∏–º—É–º 400 –∫–ì—Ü. –ù–µ –º–Ω–æ–≥–æ–≤–∞—Ç–æ –≤—ã —Ö–æ—Ç–∏—Ç–µ –æ—Ç 24LC04B? –ù–∞ —Ç–∞–∫—É—é –æ—Å—Ü. –æ–Ω–∞ –∏–º–µ–µ—Ç –ø–æ–ª–Ω–æ–µ –ø—Ä–∞–≤–æ –æ—Ç–≤–µ—á–∞—Ç—å NACK. –î–æ–±–∞–≤–ª–µ–Ω–æ after 6 minutes 29 seconds:–°–∏–º—É–ª—è—Ü–∏—é —Å–∫–∏–Ω—É–ª –ø—Ä–æ—Å—Ç–æ –≤–º–µ—Å—Ç–æ —Å–æ—Ç–µ–Ω —Å—Ç—Ä–æ—á–µ–∫ –∫–æ–¥–∞, —è—Å–Ω–æ–µ –¥–µ–ª–æ —Ç–∞–º –Ω–∏–∫–∞–∫–æ–≥–æ –æ—Ç–≤–µ—Ç–Ω–æ–≥–æ —Å–∏–≥–Ω–∞–ª–∞ –Ω–µ –±—É–¥–µ—Ç. –î–∞ —É–∂.... —Å –ª–æ–≥–∏–∫–æ–π —è–≤–Ω–æ —Å–µ—Ä—å—ë–∑–Ω—ã–µ –ø—Ä–æ–±–ª–µ–º—ã....  –í—ã –∫–æ–≥–¥–∞ –ø—Ä–∏–¥—ë—Ç–µ –∫ –≤—Ä–∞—á—É –ª–µ—á–∏—Ç—å –∫–∞–∫—É—é-—Ç–æ –±–æ–ª—è—á–∫—É, –Ω–∞–ø—Ä–∏–º–µ—Ä - –ø–µ—Ä–µ–ª–æ–º, —Ç–æ–∂–µ —Å–∫–∞–∂–µ—Ç–µ: "–î–æ–∫—Ç–æ—Ä, –¥–∞–≤–∞–π—Ç–µ –Ω–µ –±—É–¥–µ–º –¥–µ–ª–∞—Ç—å —Ä–µ–Ω—Ç–≥–µ–Ω –ø–µ—Ä–µ–ª–æ–º–∞, —è –≤–∞–º –ø—Ä–æ—Å—Ç–æ –Ω–∞—Ä–∏—Å—É—é –∫–∞–∫ —è –¥—É–º–∞—é –≤—ã–≥–ª—è–¥–∏—Ç –∫–æ—Å—Ç—å, –∞ –≤—ã –ø–æ –º–æ–µ–º—É —Ä–∏—Å—É–Ω–∫—É –∏ –ª–µ—á–∏—Ç–µ".

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

Trioni

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –°–± –¥–µ–∫ 07, 2024 10:44:20 |

|

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°—Ä –¥–µ–∫ 04, 2024 19:24:18

–°–æ–æ–±—â–µ–Ω–∏–π: 8

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

|

–ù—É –Ω–∞–≤–µ—Ä–Ω–æ –º–æ–∂–Ω–æ –∑–∞–≤–µ—Ä—à–∞—Ç—å. –ù–æ—Ä–º–∞–ª—å–Ω—ã—Ö –æ—Ç–≤–µ—Ç–æ–≤ —è —Ç–∞–∫ –∏ –Ω–µ –ø–æ–ª—É—á—É –≤—Å—ë —Ä–∞–≤–Ω–æ.

–ê —Å–∫–∏–¥—ã–≤–∞—Ç—å –∫–æ–¥ –Ω–∞ 300+ —Å—Ç—Ä–æ–∫ –≤—ã–∑–æ–≤–µ—Ç –ª–∏—à—å –æ—á–µ—Ä–µ–¥–Ω–æ–π –≤–∏—Ç–æ–∫ –≤–æ–ø—Ä–æ—Å–æ–≤ –æ –≤–µ—á–Ω–æ–º, –∞ –µ—Å–ª–∏ —Å–∫–∏–Ω—É –∫—Ä–∞—Ç–∫–∏–µ –≤—ã–¥–µ—Ä–∂–∫–∏ —Ç–æ –≤–æ–ø—Ä–æ—Å—ã —á—Ç–æ "–∫–æ–¥ –Ω–µ –≤–µ—Å—å".

–ü—Ä–æ —Ç–∞–π–º–∏–Ω–≥–∏ –æ—Ç–≤–µ—á–∞–ª –µ—â—ë –≤ –ø–µ—Ä–≤–æ–º –ø–æ—Å—Ç–µ. –ì–¥–µ –Ω–∞ –∫–∞—Ä—Ç–∏–Ω–∫–µ –≤–∏–¥–Ω–æ "T = 10uS", —Å–∫—Ä–∏–Ω —Å–∏–º—É–ª—è—Ü–∏–∏ –±—ã–ª –ø—Ä–∏–ª–µ–ø–ª–µ–Ω —á—Ç–æ –±—ã –ø–æ–∫–∞–∑–∞—Ç—å –∏—Ç–æ–≥–æ–≤–æ–µ –∑–Ω–∞—á–µ–Ω–∏–µ –∫–æ–¥–∞ (–Ω–∞–ø—Ä–∏–º–µ—Ä —á—Ç–æ sda —É—Ö–æ–¥–∏—Ç –≤ Z-—Å—Ç–µ–π—Ç) (–¥–∞–ª–µ–µ —É–∂–µ —Å–∞–º–æ—Å—Ç–æ—è—Ç–µ–ª—å–Ω–æ –Ω–µ —Ä–∞–∑ –º–µ–Ω—è–ª —Ç–∞–π–º–∏–Ω–≥–∏ –ø—Ä–æ–≤–µ—Ä—è—è –Ω–∞ 100 –∏ 400–∫–ì—Ü - –æ—Ç—Å—é–¥–∞ –∏ —Ä–∞–∑–Ω–æ—Å—Ç–∏ –º–µ–∂–¥—É –∫–∞—Ä—Ç–∏–Ω–∫–æ–π –∏ —Å–∏–º—É–ª—è—Ü–∏–µ–π)

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

jcxz

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –°–± –¥–µ–∫ 07, 2024 11:11:02 |

|

| –≠—Ç–æ –Ω–µ —Ö–≤–æ—Å—Ç, —ç—Ç–æ –∞–Ω—Ç–µ–Ω–Ω–∞ |

–ö–∞—Ä–º–∞: -10

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 171

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Ç –∞–≤–≥ 15, 2017 10:51:13

–°–æ–æ–±—â–µ–Ω–∏–π: 1482

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

–ù—É –Ω–∞–≤–µ—Ä–Ω–æ –º–æ–∂–Ω–æ –∑–∞–≤–µ—Ä—à–∞—Ç—å. –ù–æ—Ä–º–∞–ª—å–Ω—ã—Ö –æ—Ç–≤–µ—Ç–æ–≤ —è —Ç–∞–∫ –∏ –Ω–µ –ø–æ–ª—É—á—É –≤—Å—ë —Ä–∞–≤–Ω–æ. –ß—Ç–æ–±—ã –ø–æ–ª—É—á–∏—Ç—å "–Ω–æ—Ä–º–∞–ª—å–Ω—ã–π –æ—Ç–≤–µ—Ç", –Ω—É–∂–Ω–æ —Å–Ω–∞—á–∞–ª–∞ –∑–∞–¥–∞—Ç—å "–Ω–æ—Ä–º–∞–ª—å–Ω—ã–π –≤–æ–ø—Ä–æ—Å". –ß–µ–≥–æ –≤—ã –¥–æ —Å–∏—Ö –ø–æ—Ä —Ç–∞–∫ –∏ –Ω–µ —Å–¥–µ–ª–∞–ª–∏. –ò –¥–∞–∂–µ –∫–∞–∫ –≤–∏–¥–Ω–æ - –Ω–µ —Å—Ç—Ä–µ–º–∏—Ç–µ—Å—å —ç—Ç–æ —Å–¥–µ–ª–∞—Ç—å.  –ü—Ä–∏—á—ë–º —Ç—É—Ç –Ω–µ–∫–∏–π "–∫–æ–¥ –Ω–∞ 300+ —Å—Ç—Ä–æ–∫", –∫–æ—Ç–æ—Ä—ã–º –≤—ã –≤—Å—ë –ø—É–≥–∞–µ—Ç–µ - –≤–æ–æ–±—â–µ –Ω–µ –ø–æ–Ω—è—Ç–Ω–æ.

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

shonty

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –°–± –¥–µ–∫ 07, 2024 14:58:11 |

|

| –ú—É—á–∏—Ç–µ–ª—å –º–∏–∫—Ä–æ—Å—Ö–µ–º |

|

–ö–∞—Ä–º–∞: 1

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 38

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°—Ä —è–Ω–≤ 11, 2012 18:20:26

–°–æ–æ–±—â–µ–Ω–∏–π: 473

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

Trioni –ø–∏—Å–∞–ª(–∞): –ê —Å–∫–∏–¥—ã–≤–∞—Ç—å –∫–æ–¥ –Ω–∞ 300+ —Å—Ç—Ä–æ–∫ –≤—ã–∑–æ–≤–µ—Ç –ª–∏—à—å –æ—á–µ—Ä–µ–¥–Ω–æ–π –≤–∏—Ç–æ–∫ –≤–æ–ø—Ä–æ—Å–æ–≤ –æ –≤–µ—á–Ω–æ–º, –∞ –µ—Å–ª–∏ —Å–∫–∏–Ω—É –∫—Ä–∞—Ç–∫–∏–µ –≤—ã–¥–µ—Ä–∂–∫–∏ —Ç–æ –≤–æ–ø—Ä–æ—Å—ã —á—Ç–æ "–∫–æ–¥ –Ω–µ –≤–µ—Å—å". –ù—É –µ—Å–ª–∏ —Å—Ç–∞—Ä—Ç–æ–≤–æ–µ_—É—Å–ª–æ–≤–∏–µ+–∞–¥—Ä–µ—Å+–ø—Ä–æ–≤–µ—Ä–∫–∞_—Å–æ—Å—Ç–æ—è–Ω–∏—è —ç—Ç–æ 300+ —Å—Ç—Ä–æ–∫, —Ç–æ–≥–¥–∞ –ª—É—á—à–µ –Ω–µ –Ω—É–∂–Ω–æ —Å–∫–∏–¥—ã–≤–∞—Ç—å)) –ù–æ –∫–æ–¥ –≤—Å–µ–≥–¥–∞ –≤—Ç–æ—Ä–∏—á–µ–Ω) –¥–∞–∂–µ —Ç—Ä–µ—Ç–∏—á–µ–Ω, –µ—Å–ª–∏ –Ω–µ —á–µ—Ç–≤–µ—Ä–∏—á–µ–Ω –∏–ª–∏ –ø—è—Ç–µ—Ä–∏—á–µ–Ω))

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

Trioni

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –°–± –¥–µ–∫ 07, 2024 21:38:03 |

|

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°—Ä –¥–µ–∫ 04, 2024 19:24:18

–°–æ–æ–±—â–µ–Ω–∏–π: 8

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

|

–í—Å–µ–º —Å–ø–∞—Å–∏–±–æ. –Ý–∞–∑–æ–±—Ä–∞–ª—Å—è —Å–∞–º - –Ω–µ–∏—Å–ø—Ä–∞–≤–Ω–∞ –º–∏–∫—Ä–æ—Å—Ö–µ–º–∞ EEPROM –ø–æ—Ö–æ–∂–µ(–∏–ª–∏ –µ—ë –∞–¥—Ä–µ—Å).

–°–º–æ–≥ –¥–æ—Å—Ç–∞—Ç—å –¥–∏—Å–ø–ª–µ–π –Ω–∞ i2c –∏ –æ–Ω –≤–ø–æ–ª–Ω–µ –æ—Ç–∑—ã–≤–∞–µ—Ç—Å—è.

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

Martian

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: EEPROM 24LC04B  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –°–± –¥–µ–∫ 07, 2024 21:43:01 |

|

–ö–∞—Ä–º–∞: 68

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 1958

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°–± –¥–µ–∫ 18, 2021 19:25:32

–°–æ–æ–±—â–µ–Ω–∏–π: 12867

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

|

–£–≤—ã, –Ω–æ —ç—Ç–æ –Ω–µ —É–∫–∞–∑—ã–≤–∞–µ—Ç –Ω–∞ –Ω–µ–∏—Å–ø—Ä–∞–≤–Ω–æ—Å—Ç—å EEPROM

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

|

–°—Ç—Ä–∞–Ω–∏—Ü–∞ 1 –∏–∑ 2

|

[ –°–æ–æ–±—â–µ–Ω–∏–π: 23 ] |

, |

–ö—Ç–æ —Å–µ–π—á–∞—Å –Ω–∞ —Ñ–æ—Ä—É–º–µ |

–°–µ–π—á–∞—Å —ç—Ç–æ—Ç —Ñ–æ—Ä—É–º –ø—Ä–æ—Å–º–∞—Ç—Ä–∏–≤–∞—é—Ç: –Ω–µ—Ç –∑–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω–Ω—ã—Ö –ø–æ–ª—å–∑–æ–≤–∞—Ç–µ–ª–µ–π –∏ –≥–æ—Å—Ç–∏: 10 |

|

–í—ã –Ω–µ –º–æ–∂–µ—Ç–µ –Ω–∞—á–∏–Ω–∞—Ç—å —Ç–µ–º—ã

–í—ã –Ω–µ –º–æ–∂–µ—Ç–µ –æ—Ç–≤–µ—á–∞—Ç—å –Ω–∞ —Å–æ–æ–±—â–µ–Ω–∏—è

–í—ã –Ω–µ –º–æ–∂–µ—Ç–µ —Ä–µ–¥–∞–∫—Ç–∏—Ä–æ–≤–∞—Ç—å —Å–≤–æ–∏ —Å–æ–æ–±—â–µ–Ω–∏—è

–í—ã –Ω–µ –º–æ–∂–µ—Ç–µ —É–¥–∞–ª—è—Ç—å —Å–≤–æ–∏ —Å–æ–æ–±—â–µ–Ω–∏—è

–í—ã –Ω–µ –º–æ–∂–µ—Ç–µ –¥–æ–±–∞–≤–ª—è—Ç—å –≤–ª–æ–∂–µ–Ω–∏—è

|

|

|