BOB51 писал(а):Досрочное окончание запроса (недостаток тактовых импульсов в частности) может привести к сбою во внешнем устройстве (сбой последовательности адресации, незавершенность последней операции и/или из оного проистекаюшши).

Гораздо вернее выполнить полный цикл по протоколу, а затем, уже в процессе обработки принятых данных, "отбросить лишнее" методами самого МК.

Нет, Вы кажется, не поняли мой вопрос. Я хочу оборвать тактовые импульсы не с целью ДОСРОЧНО прервать передачу байта для более удобной обработки данных. Пишу на ассемблере и пару строчек кода перекидки битов с байта на байт меня не напрягут совершенно.

Спойлер

Отклоняясь от темы замечу, что Microchip и это продумала.

Код: Выделить всё

After the second eight clocks have been sent to the device, the MCU receive register will contain the lowest-order seven bits and the B1 bit repeated as the A/D Converter has begun to shift out LSB first data with the extra clock.

Typical procedure would then call for the lower-order byte of data to be shifted right by one bit to remove the extra B1 bit. The B7 bit is then transferred from the high-order byte to the lower-order byte, and then the higher-order byte is shifted one bit to the right as well. Easier manipulation of the converted data can be obtained by using this method.

Тут говорится, что после приёма двух байт данных АЦП, если не отключать клоки и сигнал выбора, продолжит сдвигать биты вправо и после первого же сдвига бит B0 станет самым правым в младшем байте , а бит 7 перейдет из старшего байта в младший и станет там самым левым, соответственно. И тогда младший байт уже не нужно никак обрабатывать - он готов родименький к использованию.Но я спрашиваю про реализацию ЗАЯВЛЕННОЙ Microchip-ом задержки тактового импульса при передачи бита

B6 (см. временную диаграмму, такт 9). Связано эта задержка с тем, как я понял, что после приёма старшего байта я не отключаю микрсхему, как обычно делается в однобайтной передаче, а продолжаю считывать всё слово целиком. И мне нужно быстро снять данные из сдвигового регистра SPI контроллера, пока данные в нём не изменились, иначе я потеряю информацию. Поэтому в девятом такте генерация импульсов прекращается. В принципе, я могу заранее поставить частоту тактовых импульсов такой (скажем, Fclk = Fcpu/4 или Fclk = Fcpu/8) , чтобы за время одного клока я успел скопировать сдвиговый регистр и тогда мне не надо тормозить импульсы. Но если я хочу работать на частоте Fclk = Fcpu/2, тогда после приёма первого байта нужно что-то думать. Например, следующей командой изменить частоту с Fcpu/2 до Fcpu/16, например. То есть, временно затянуть генератор импульсов SPI. На самом деле, мне не критично, Fcpu/4 или Fcpu/2, так что могу поставить Fcpu/4 и не мучится, просто спортивный интерес -- как сделать, если я не успеваю скопировать регистр.

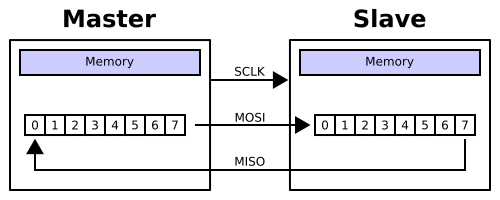

Добавлено after 5 hours 24 minutes 35 seconds: Создается ощущение, что разобрался с обеими вопросами. По поводу расположения первого вошедшего бита в регистр сдвига. Я, как "Master", сам решаю, первый вошедший бит будет расположен в конце слева или в конце справа регистра. То есть, я решаю в какую сторону будет "двигаться" карусель MISO-MISO, MOSI-MOSI.

На рисунке направление выбрано так, чтобы первый вошедший бит из Slave был слева. Из переводной инструкции к AVR от Евстифеева:

Порядок передачи разрядов данных определяется состоянием разряда DORD регистра SPCR. Если разряд установлен в «1», пер�вым передается младший разряд байта, если же сброшен в «0» — старший разряд.

По поводу второго вопроса: как остановить CLOCK, после передачи первого байта. Я невнимательно читал документацию к AVR:

Передача данных осуществляется следующим образом. При записи в регистр данных SPI ведущего микроконтроллера запускается генератор тактового сигнала модуля SPI, и данные начинают поразрядно выдаваться на вы�вод MOSI и соответственно поступать на вывод MOSI ведомого микроконтроллера. После выдачи последнего разряда текущего байта генератор тактового сигнала останавливается с одновременной установкой в «1» флага «Конец передачи» (SPIF). После этого ведущий микроконтроллер может начать передачу следующего байта.

Одновременно с передачей данных от ведущего к ведомому происходит передача и в обратном направлении при условии, что на входе SS ведомого присутствует напряжение НИЗКОГО уровня.

То есть, после приёма первого байта, тактовые импульсы автоматически прекращаются. Для приёма второго байта мне нужно загрузить в регистр данных SPI какое-либо число и "карусель" опять начнет крутиться.