Код: Выделить всё

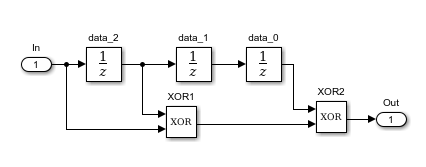

module shift_reg(input logic clk,

input logic in,

input logic enable,

output logic out);

reg [2:0] data = 3'b000;

always @(posedge clk) begin

if (enable)

data <= { in, data[2:1] };

end

assign out = in ^ data[2] ^ data[0];

endmodule

Код: Выделить всё

data <= { in, data[2:1] };Код: Выделить всё

data <= { data[2:1], in };Будет ли схема работать по-другому, если написать:

Код: Выделить всё

data <= { in, data[1:0],};И еще вопрос. Есть ли возможность сразу на широкую шину (скажем, 8 бит) выставить коэффициенты многочлена единовременно, а не по одному биту? Как это сделать?

Добавлено after 8 hours 39 minutes 47 seconds:

И еще вопрос

Как задаются индексы шины при конкатенации шин? Вот например:

wire [1:0] dataIn;

assign dataIn = {d1,d0};

Тут dataIn[0] содержит сигнал d0 или d1? Или это не имеет значения?