Нужно реализовать задержку между сигналами DIR и STEP, от 7000 до 10000 наносекунд. Точность не важна.

Главное, чтобы было в этом диапазоне.

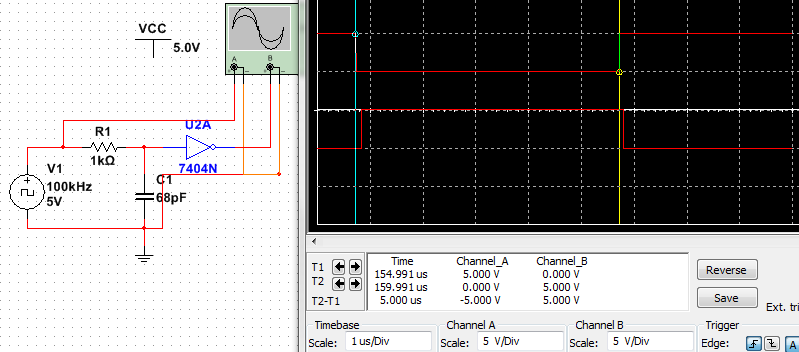

При этом, форма сигнала должна не испортится. и на выходе, так же как и на входе, нужно получить амплитуду 4,5-5,5 вольт.

Засада в том, что контроллер, как раз таки, не может осуществить задержку, более 1000 нс. По причинам, которые преодолеть пока не получается.

Хотелось бы, чтобы решение было, как можно более простое. 14 микросхем, это многовато

Микросхемы - линии задержки, которые я нашёл, дают максимум 1250 нс.

Может кто-нибудь за денежку, разработать приличную схему? Без разработки ПП.