Кто любит RISC в жизни, заходим, не стесняемся.

Vlid

Первый раз сказал Мяу!

Сообщения: 32 Зарегистрирован: Ср янв 18, 2017 13:11:34

Сообщение

Vlid Пт мар 15, 2019 09:50:42

Добрый день!

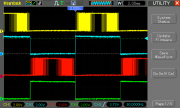

Пытаюсь настроить ШИМ модуляцию для инвертора с чистым синусом. То есть должно быть примерно такая картинка.

Спойлер Пробовал настраивать с помощью прерываний. Работает почти так как надо однако решение не совсем красиво.

Помогите настроить профессионально, так сказать

Вложения

Untitled.png (27.96 КБ) 391 скачивание

Аlex

Модератор

Сообщения: 4614 Зарегистрирован: Чт мар 18, 2010 23:09:57Откуда: Планета Земля

Контактная информация:

Сообщение

Аlex Пт мар 15, 2019 10:01:37

Vlid писал(а): Работает почти так как надо

Это как ?

Показывайте решение и рассказывайте, что в нём не нравится.

Vlid

Первый раз сказал Мяу!

Сообщения: 32 Зарегистрирован: Ср янв 18, 2017 13:11:34

Сообщение

Vlid Пт мар 15, 2019 17:04:15

Таким образом настраиваю ШИМ (EPWM1 отвечает за импульсы низкой частоты, а EPWM2 за формирование синусоиды):

Код: Выделить всё

EPwm1Regs.TBPRD = 4000; В прерывании EPWM2 от забрасываются значение из таблицы синусов в CMPA или CMPB. В прерывании от EPWM1 включаются и исключаются последовательно CMPA и CMPB модуля EPWM2.