|

|

|||||||||||||||

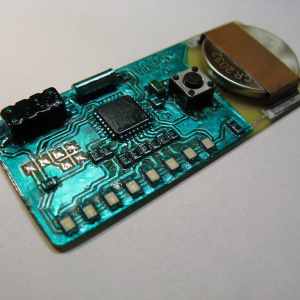

ąöąĄą╗čīčéą░-ąĪąĖą│ą╝ą░ ąÉą”ą¤ ą┤ą╗čÅ ą£ąÜ ąĮą░ ą┐čĆąĖą╝ąĄčĆąĄ ATtiny2313

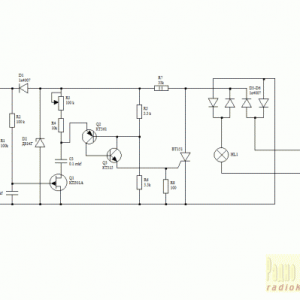

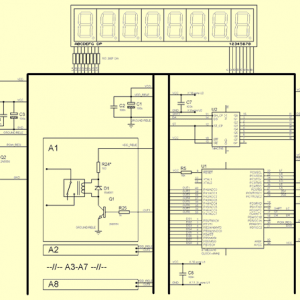

ąÉą▓č鹊čĆ: ąÜčāčĆą║ąĖąĮ ąÉą╗ąĄą║čüąĄą╣ aka Gudd-Head ąÆ ą┤ą░ąĮąĮąŠą╣ čüčéą░čéčīąĄ čÅ ą┐ąŠą┐čŗčéą░čÄčüčī ąŠą▒čŖčÅčüąĮąĖčéčī ą┐čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéčŗ ą┤ąĄą╗čīčéą░-čüąĖą│ą╝ą░ (ąöąĪ, ąĮą░ąĘčŗą▓ą░ąĄą╝ąŠą│ąŠ čéą░ą║ąČąĄ čüąĖą│ą╝ą░-ą┤ąĄą╗čīčéą░) ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠ-čåąĖčäčĆąŠą▓ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅ (ąÉą”ą¤) ąĖ ą┐ąŠą║ą░ąĘą░čéčī, ą║ą░ą║ ąĄą│ąŠ ą╝ąŠąČąĮąŠ ą┐čĆąĖą║ąŠčłą░čćąĖčéčī ą║ ą╗čÄą▒ąŠą╝čā (ą║ą░ą║ ą╝ąĮąĄ ą║ą░ąČąĄčéčüčÅ) ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā (ą£ąÜ). ą¤ąŠč湥ą╝čā ą▓ ą║ą░č湥čüčéą▓ąĄ ą£ąÜ ą▒čŗą╗ą░ ą▓čŗą▒čĆą░ąĮą░ ąĖą╝ąĄąĮąĮąŠ čŹčéą░ čéąĖąĮčīą║ą░? ą¤čĆąŠčüč鹊 ą┐ąŠč鹊ą╝čā, čćč鹊 ąŠąĮą░ čā ą╝ąĄąĮčÅ ąĘą░ą▓ą░ą╗čÅą╗ą░čüčī, ą┤ą░ ąĄčēčæ ąĖ ą▓ DIP-ą║ąŠčĆą┐čāčüąĄ, čāą┤ąŠą▒ąĮąŠą╝ ą┤ą╗čÅ ą╝ą░ą║ąĄčéąĖčĆąŠą▓ą░ąĮąĖčÅ! ąÉ ąĄčēčæ čā ąĮąĄčæ ąĮąĄčé ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ ąÉą”ą¤. ąÜ č鹊ą╝čā ąČąĄ, čüčāą┤čÅ ą┐ąŠ čĆą░ąĘą╝ąĄčĆčā ą┐ąŠčüą▓čÅčēčæąĮąĮąŠą╣ ąĄą╣ č鹥ą╝čŗ č乊čĆčāą╝ą░ [1], ąŠąĮą░ ą┐čĆąĖąŠą▒čĆąĄą╗ą░ ąĮą░čĆąŠą┤ąĮčāčÄ ą╗čÄą▒ąŠą▓čī. ą¤ą╗čÄčü ą║ąŠ ą▓čüąĄą╝čā, ą▒čāą┤čā čüčéą░čĆą░čéčīčüčÅ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ąŠčĆąŠą│ąĖąĄ ąĖ čéčĆčāą┤ąĮąŠą┤ąŠčüčéą░ą▓ą░ąĄą╝čŗąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ. ąĪąŠą▓čĆąĄą╝ąĄąĮąĮčŗą╣ ąöąĪ ąÉą”ą¤ čüąŠčüč鹊ąĖčé ąĖąĘ ą┤ąĄą╗čīčéą░-čüąĖą│ą╝ą░ ą╝ąŠą┤čāą╗čÅč鹊čĆą░ ąĖ čåąĖčäčĆąŠą▓ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅ ŌĆö ą┤ąĄčåąĖą╝ąĖčĆčāčÄčēąĄą│ąŠ čåąĖčäčĆąŠą▓ąŠą│ąŠ čäąĖą╗čīčéčĆą░, ą║ąŠč鹊čĆčŗą╣, ą▓ čüą▓ąŠčÄ ąŠč湥čĆąĄą┤čī, čüąŠčüč鹊ąĖčé ąĖąĘ čäąĖą╗čīčéčĆą░ ąĮąĖąČąĮąĖčģ čćą░čüč鹊čé (ążąØą¦) ąĖ ą┤ąĄčåąĖą╝ą░č鹊čĆą░ (čĆąĖčü. 1) [2].

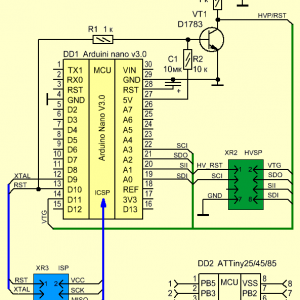

ąĀąĖčü.1. ąĪčéčĆčāą║čéčāčĆą░ ą┤ąĄą╗čīčéą░-čüąĖą│ą╝ą░ ąÉą”ą¤ ąÆ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ąÉą”ą¤ ą┤čĆčāą│ąĖčģ ą▓ąĖą┤ąŠą▓, ą▓ ą┤ąĄą╗čīčéą░-čüąĖą│ą╝ą░ ąÉą”ą¤ ąŠčéčüč湥čéčŗ ą▒ąĄčĆčāčéčüčÅ ąĮąĄ ą▓ č鹊čćą║ą░čģ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ, ą░ ąĮą░ ąĖąĮč鹥čĆą▓ą░ą╗ą░čģ ąĖ čÅą▓ą╗čÅčÄčéčüčÅ, čüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, čüčĆąĄą┤ąĮąĖą╝ąĖ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄą╝ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮą░ čŹčéąĖčģ ąĖąĮč鹥čĆą▓ą░ą╗ą░čģ. ąöąĖčüą║čĆąĄčéąĖąĘą░čåąĖčÅ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĮą░ čćą░čüč鹊č鹥, ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ ą┐čĆąĄą▓čŗčłą░čÄčēčāčÄ čāą┤ą▓ąŠąĄąĮąĮčāčÄ ą▓ąĄčĆčģąĮčÄčÄ čćą░čüč鹊čéčā čüą┐ąĄą║čéčĆą░ ą┐ąŠą╗ąĄąĘąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ (ą▓ ą┤ąĄčüčÅčéą║ąĖ ąĖ čüąŠčéąĮąĖ čĆą░ąĘ). ą×ą▒ą░ čŹčéąĖčģ čäą░ą║čéą░ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ ą┐ąŠąĮąĖąĘąĖčéčī čüą┐ąĄą║čéčĆą░ą╗čīąĮčāčÄ ą┐ą╗ąŠčéąĮąŠčüčéčī čüčĆąĄą┤ąĮąĄą╣ ą╝ąŠčēąĮąŠčüčéąĖ čłčāą╝ą░ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ ą▓ ą┐ąŠą╗ąŠčüąĄ ą┐ąŠą╗ąĄąĘąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąÆčŗčģąŠą┤ąĮčŗą╝ čüąĖą│ąĮą░ą╗ąŠą╝ ą┐čĆąĄąŠą▒čĆą░ąĘčāčÄčēąĄą│ąŠ (ą┤ąĄčåąĖą╝ąĖčĆčāčÄčēąĄą│ąŠ) čäąĖą╗čīčéčĆą░, ąĖ, čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ, ąÉą”ą¤ ą▓ čåąĄą╗ąŠą╝, čÅą▓ą╗čÅąĄčéčüčÅ N-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ čåąĖčäčĆąŠą▓ąŠą╣ čüąĖą│ąĮą░ą╗, čćą░čüč鹊čéą░ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ąŠčéčüč湥č鹊ą▓ ą║ąŠč鹊čĆąŠą│ąŠ čĆą░ą▓ąĮą░ čćą░čüč鹊č鹥 ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ Fd, ą║ąŠč鹊čĆą░čÅ ą▓ ą£ čĆą░ąĘ ą╝ąĄąĮčīčłąĄ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą╝ąŠą┤čāą╗čÅč鹊čĆą░ Fs (Fs=M┬ĘFd). ą£ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą╝ ą┤ąĄčåąĖą╝ą░čåąĖąĖ, ą┐čĆąĖč湥ą╝ ąŠą▒čŗčćąĮąŠ ąŠąĮ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čćč鹊ą▒čŗ čćą░čüč鹊čéą░ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ ą▒čŗą╗ą░ ą▒ą╗ąĖąĘą║ą░ ą║ čāą┤ą▓ąŠąĄąĮąĮąŠą╣ ą▓ąĄčĆčģąĮąĄą╣ čćą░čüč鹊č鹥 čüą┐ąĄą║čéčĆą░ ą┐ąŠą╗ąĄąĘąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąśąĘ čüąŠąŠą▒čĆą░ąČąĄąĮąĖą╣ čāą┤ąŠą▒čüčéą▓ą░ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╣ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ čäąĖą╗čīčéčĆą░ ąŠą▒čŗčćąĮąŠ ą£ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čĆą░ą▓ąĮčŗą╝ 2^N, ą│ą┤ąĄ N ŌĆö čåąĄą╗ąŠąĄ. ą¤čĆąĄąĖą╝čāčēąĄčüčéą▓ąŠą╝ ą┤ąĄą╗čīčéą░-čüąĖą│ą╝ą░ ąÉą”ą¤ ą┐ąĄčĆąĄą┤ ą┤čĆčāą│ąĖą╝ąĖ čéąĖą┐ą░ą╝ąĖ ąÉą”ą¤ čéą░ą║ąČąĄ čÅą▓ą╗čÅąĄčéčüčÅ č鹊čé čäą░ą║čé, čćč鹊, ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü č鹥ąŠčĆąĄą╝ąŠą╣ ąÜąŠč鹥ą╗čīąĮąĖą║ąŠą▓ą░, čćą░čüč鹊čéąĮčŗą╣ čüą┐ąĄą║čéčĆ ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄą╝ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┤ąŠą╗ąČąĄąĮ ą╗ąĄąČą░čéčī ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ čćą░čüč鹊čé ąŠčé 0 ą┤ąŠ Fd/2, ą┐ąŠčŹč鹊ą╝čā ąĮą░ ą▓čģąŠą┤ąĄ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ą░ ąÉą”ą¤ ą┤čĆčāą│ąĖčģ čéąĖą┐ąŠą▓ čüčéą░ą▓čÅčé ążąØą¦ čü čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ą┐ąŠą╗ąŠčüąŠą╣ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ. ąöą╗čÅ ąöąĪ ąÉą”ą¤ ą┤ą░ąĮąĮąŠąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖąĄ ą║ čäąĖą╗čīčéčĆčā ąŠčüą╗ą░ą▒ą╗ąĄąĮąŠ: ą┐čĆąĖ č鹊ą╣ ąČąĄ čłąĖčĆąĖąĮąĄ čüą┐ąĄą║čéčĆą░ čüąĖą│ąĮą░ą╗ą░, ąĄą│ąŠ ą▓čģąŠą┤ąĮą░čÅ čäąĖą╗čīčéčĆą░čåąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮą░ čü ą┐ąŠą╗ąŠą│ąĖą╝ čüą┐ą░ą┤ąŠą╝ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ čćą░čüč鹊čé ąŠčé Fd/2 ą┤ąŠ Fs/2 ąĖ, čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ, čäąĖą╗čīčéčĆ ąĮąĄ ą▒čāą┤ąĄčé ą▓ąĮąŠčüąĖčéčī čüčāčēąĄčüčéą▓ąĄąĮąĮčŗčģ čćą░čüč鹊čéąĮčŗčģ ąĖ čäą░ąĘąŠą▓čŗčģ ąĖčüą║ą░ąČąĄąĮąĖą╣ ą▓ ą┐ąŠą╗ąŠčüąĄ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ. ąøąĖčłčī ąĘą░č鹥ą╝, ą▓ ą┤ąĄčåąĖą╝ąĖčĆčāčÄčēąĄą╝ čäąĖą╗čīčéčĆąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čŹčäč乥ą║čéąĖą▓ąĮą░čÅ čåąĖčäčĆąŠą▓ą░čÅ čäąĖą╗čīčéčĆą░čåąĖčÅ čü ą┐ąŠą╗ąŠčüąŠą╣ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ąŠčé 0 ą┤ąŠ Fd/2. ą¤čĆąĖ čŹč鹊ą╝ čćąĖčüą╗ąŠ ąĘą▓ąĄąĮčīąĄą▓ čäąĖą╗čīčéčĆą░ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąĮą░ ąĄą┤ąĖąĮąĖčåčā ą▒ąŠą╗čīčłąĄ ą┐ąŠčĆčÅą┤ą║ą░ ą╝ąŠą┤čāą╗čÅč鹊čĆą░. ą¤čĆąŠčüč鹥ą╣čłąĖą╣ ą┤ąĄčåąĖą╝ąĖčĆčāčÄčēąĖą╣ čäąĖą╗čīčéčĆ ą╝čŗ čĆąĄą░ą╗ąĖąĘčāąĄą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą▓ ą£ąÜ, ą░ ą▓ąŠčé ą╝ąŠą┤čāą╗čÅč鹊čĆ ą┐čĆąĖą┤čæčéčüčÅ čüą┤ąĄą╗ą░čéčī ą▓ąĮąĄčłąĮąĖą╣. ąĀą░čüčüą╝ąŠčéčĆąĖą╝ čüčéčĆčāą║čéčāčĆąĮčāčÄ čüčģąĄą╝čā ą╝ąŠą┤čāą╗čÅč鹊čĆą░ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░ (čüą╝. čĆąĖčü. 2) [3]. ą£ąŠą┤čāą╗čÅč鹊čĆ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąŠą▒ąŠą╣ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čćą░čüč鹊č鹊ą╣ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ fčéą░ą║čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī ┬½ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ-čćą░čüč鹊čéą░┬╗ čü ąĮąĄą┐čĆąĄčĆčŗą▓ąĮčŗą╝ ąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ąĖ čāčĆą░ą▓ąĮąŠą▓ąĄčłąĖą▓ą░ąĮąĖąĄą╝ ąĘą░čĆčÅą┤ą░. ąĀąĖčü.2. ąĪčéčĆčāą║čéčāčĆąĮą░čÅ čüčģąĄą╝ą░ ą┤ąĄą╗čīčéą░-čüąĖą│ą╝ą░ ą╝ąŠą┤čāą╗čÅč鹊čĆą░ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░ ┬Āą¤ąŠčĆčÅą┤ąŠą║ ą╝ąŠą┤čāą╗čÅč鹊čĆą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ ąĖąĮč鹥ą│čĆą░č鹊čĆąŠą▓ ąĖ čüčāą╝ą╝ą░č鹊čĆąŠą▓. ąŻą▓ąĄą╗ąĖč湥ąĮąĖąĄ ą┐ąŠčĆčÅą┤ą║ą░ ą╝ąŠą┤čāą╗čÅč鹊čĆą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čāą▓ąĄą╗ąĖčćąĖčéčī čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗/čłčāą╝. ąĀą░ą▒ąŠčéą░ čŹč鹊ą╣ čüčģąĄą╝čŗ ąŠčüąĮąŠą▓ą░ąĮą░ ąĮą░ ą▓čŗčćąĖčéą░ąĮąĖąĖ ąĖąĘ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ Uą▓čģ(t) ą▓ąĄą╗ąĖčćąĖąĮčŗ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ čåąĖčäčĆąŠ-ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅ (ą”ąÉą¤), ą┐ąŠą╗čāč湥ąĮąĮąŠą╣ ąĮą░ ą┐čĆąĄą┤čŗą┤čāčēąĄą╝ čéą░ą║č鹥 čĆą░ą▒ąŠčéčŗ čüčģąĄą╝čŗ. ą¤ąŠą╗čāč湥ąĮąĮą░čÅ čĆą░ąĘąĮąŠčüčéčī ąĖąĮč鹥ą│čĆąĖčĆčāąĄčéčüčÅ, ą░ ąĘą░č鹥ą╝ ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčéčüčÅ ą▓ ą║ąŠą┤ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╝ ąÉą”ą¤ ąĮąĄą▓čŗčüąŠą║ąŠą╣ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą║ąŠą┤ąŠą▓ ą┐ąŠčüčéčāą┐ą░ąĄčé ąĮą░ čåąĖčäčĆąŠą▓ąŠą╣ čäąĖą╗čīčéčĆ ąĮąĖąČąĮąĖčģ čćą░čüč鹊čé. ąÆ ą┐čĆąŠčüč鹥ą╣čłąĄą╝ čüą╗čāčćą░ąĄ ąÉą”ą¤ ąĖ ą”ąÉą¤ ąŠą┤ąĮąŠą▒ąĖčéąĮčŗąĄ, čé.ąĄ. ąÉą”ą¤ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąŠą▒ąŠą╣ čéą░ą║čéąĖčĆčāąĄą╝čŗą╣ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ, ą░ ą”ąÉą¤ ŌĆō ┬½ą┐ąĄčĆąĄą║ą╗čÄčćą░č鹥ą╗čī┬╗ ą╝ąĄąČą┤čā ąŠą┐ąŠčĆąĮčŗą╝ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅą╝ąĖ ŌĆōUąŠą┐ ąĖ +UąŠą┐ (čĆąĖčü.3).

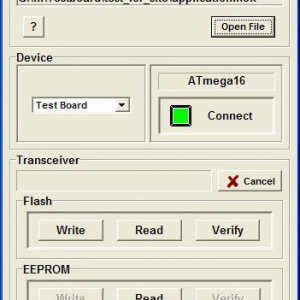

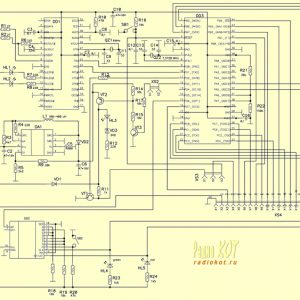

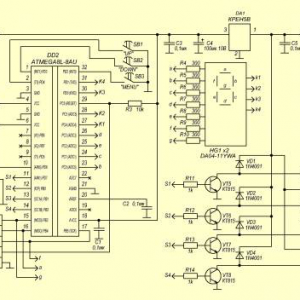

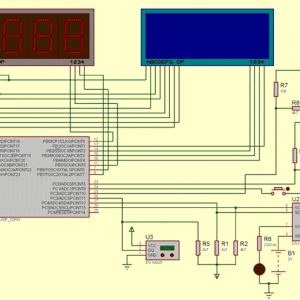

ąĀąĖčü.3. ąĪčéčĆčāą║čéčāčĆąĮą░čÅ čüčģąĄą╝ą░ ą┐čĆąŠčüč鹥ą╣čłąĄą│ąŠ ą┤ąĄą╗čīčéą░-čüąĖą│ą╝ą░ ąÉą”ą¤ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░ ąśčéą░ą║, ąĮą░ą╝ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗąĄ čüčāą╝ą╝ą░č鹊čĆ/ą▓čŗčćąĖčéą░č鹥ą╗čī ąĖ ąĖąĮč鹥ą│čĆą░č鹊čĆ, čéą░ą║čéąĖčĆčāąĄą╝čŗą╣ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ, ąŠą┤ąĮąŠą▒ąĖčéąĮčŗą╣ ą”ąÉą¤ ąĖ čåąĖčäčĆąŠą▓ąŠą╣ čäąĖą╗čīčéčĆ. ąÜą░ą║ čāąČąĄ ą│ąŠą▓ąŠčĆąĖą╗ąŠčüčī ą▓čŗčłąĄ, čåąĖčäčĆąŠą▓ąŠą╣ čäąĖą╗čīčéčĆ ą╝čŗ čĆąĄą░ą╗ąĖąĘčāąĄą╝ ąĮą░ ą£ąÜ. ąÜąŠą╝ą┐ą░čĆą░č鹊čĆ ąĄčüčéčī čā čéąĖąĮčīą║ąĖ, ąŠą┤ąĮą░ą║ąŠ ąĮąĄ ą▒čāą┤ąĄą╝ ą║ ąĮąĄą╝čā ą┐čĆąĖą▓čÅąĘčŗą▓ą░čéčīčüčÅ, čé.ą║. čā ą┤čĆčāą│ąĖčģ ą£ąÜ ąĄą│ąŠ ąĮąĄčé (ą║ č鹊ą╝čā ąČąĄ, ą║ą░ą║ ą▒čāą┤ąĄčé ą┐ąŠą║ą░ąĘą░ąĮąŠ ą┤ą░ą╗ąĄąĄ, ąŠąĮ ą▓čüčæ čĆą░ą▓ąĮąŠ ąĮąĄ ą┐ąŠą┤ąŠą╣ą┤čæčé). ąĪčāą╝ą╝ą░č鹊čĆ/ą▓čŗčćąĖčéą░č鹥ą╗čī čĆąĄą░ą╗ąĖąĘčāąĄą╝ ąĮą░ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╝ čāčüąĖą╗ąĖč鹥ą╗ąĄ (ą×ąŻ), ąĮą░ ąĮčæą╝ ąČąĄ čüą┤ąĄą╗ą░ąĄą╝ ąĖ ąĖąĮč鹥ą│čĆą░č鹊čĆ ą┐ąŠ ą║ą╗ą░čüčüąĖč湥čüą║ąĖą╝ čüčģąĄą╝ą░ą╝ [4]. ą¤ąŠą╗čāčćą░ąĄčéčüčÅ čćč鹊-č鹊 ą┐ąŠčģąŠąČąĄąĄ ąĮą░ čĆąĖčü.4. ąÆčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą┐ąŠą┤ą░čæčéčüčÅ ąĮą░ R1, ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ čü ą▓čŗčģąŠą┤ą░ ąÉą”ą¤ ŌĆö ąĮą░ R3. ąöą░, ąĄčēčæ čģąŠčĆąŠčłąŠ ą▒čŗ ą┤ąŠą▒ą░ą▓ąĖčéčī ą┐ąĄčĆąĄą┤ R1 ą┐ąŠą▓č鹊čĆąĖč鹥ą╗čī ŌĆö ą╝ąŠąČąĮąŠ, ąŠą┐čÅčéčī ąČąĄ, ąĮą░ ą×ąŻ ŌĆö ą┤ą╗čÅ čāą▓ąĄą╗ąĖč湥ąĮąĖčÅ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ. ąśč鹊ą│ąŠ ąĮą░ą╝ ą┐ąŠčéčĆąĄą▒čāąĄčéčüčÅ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 3 ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąĖą║ą░.

┬ĀąĀąĖčü.4. ąĪčāą╝ą╝ą░č鹊čĆ/ą▓čŗčćąĖčéą░č鹥ą╗čī ąĖ ąĖąĮč鹥ą│čĆą░č鹊čĆ ąöąĪą£ ąæčāą┤ąĄą╝ čüčćąĖčéą░čéčī, čćč鹊 ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄą╝čŗą╣ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ čā ąĮą░čü ąĮąĄąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣. ąÆ ą║ą░č湥čüčéą▓ąĄ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ŌĆōUąŠą┐ ą▓ąŠąĘčīą╝čæą╝ ą┐ąŠč鹥ąĮčåąĖą░ą╗ ąŠą▒čēąĄą│ąŠ ą┐čĆąŠą▓ąŠą┤ą░ ŌĆö 0 ąÆ. ąŚą░ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ +UąŠą┐ ą┐čĆąĖą╝ąĄą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąóąŠą│ą┤ą░ ą▓ ą║ą░č湥čüčéą▓ąĄ ąŠą┤ąĮąŠą▒ąĖčéąĮąŠą│ąŠ ą”ąÉą¤ą░ ą▒čāą┤ąĄą╝ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐ąŠčĆčé ą▓čŗą▓ąŠą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.┬Āą¤čĆąŠą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄą╝ ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓ čāąĘą╗ą░čģ čüčģąĄą╝čŗ, ąĖąĘąŠą▒čĆą░ąČčæąĮąĮąŠą╣ ąĮą░ čĆąĖčü.4. ąÆčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗, čĆą░ą▓ąĮąŠ ą║ą░ą║ ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą”ąÉą¤ą░ ą╗ąĄąČąĖčé ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 0ŌĆ”+UąŠą┐. ąŚąĮą░čćąĖčé, ąĮą░ ą▓čģąŠą┤ąĄ ąĖąĮč鹥ą│čĆą░č鹊čĆą░ čüą╗ąĄą┤čāąĄčé ąŠąČąĖą┤ą░čéčī ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčé ŌĆōUąŠą┐ ą┤ąŠ +UąŠą┐. ąśąĮč鹥ą│čĆą░č鹊čĆ čā ąĮą░čü ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĖą╣, ąĮąŠ čŹč鹊 ąĮąĄ čüčéčĆą░čłąĮąŠ, čé.ą║. čŹč鹊 ą╝ąŠąČąĮąŠ čāč湥čüčéčī ą┐čĆąŠčüč鹊ą╣ čüą╝ąĄąĮąŠą╣ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. ąÜ čüąŠąČą░ą╗ąĄąĮąĖčÄ, ą▓čģąŠą┤čŗ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąĮąĄ ą┐ąĄčĆąĄąĮąŠčüčÅčé ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, ą┐ąŠčŹč鹊ą╝čā ąĮąĄ ą┐ąŠą╗čāčćąĖčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ 2313 ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ. ą×ą┤ąĮą░ą║ąŠ, ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ čŹą╗ąĄą╝ąĄąĮčéą░čĆąĮąŠ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░čéčī ŌĆö ą┤ą░! ŌĆö ąŠą┐čÅčéčī ąČąĄ, ąĮą░ ą×ąŻ. ąśč鹊ą│ąŠ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čĆąŠą▓ąĮąŠ 4 ąŠą┐ąĄčĆą░. ą¤ąŠč湥ą╝čā čĆąŠą▓ąĮąŠ? ąöą░ ą┐ąŠč鹊ą╝čā čćč鹊 ąŠąĮąĖ ą▓čŗą┐čāčüą║ą░čÄčéčüčÅ ą┐ąŠ 4 čłčé. ą▓ ąŠą┤ąĮąŠą╝ 14-čéąĖ ą▓čŗą▓ąŠą┤ąĮąŠą╝ ą║ąŠčĆą┐čāčüąĄ! ąŁą║ąŠąĮąŠą╝ąĖčÅ ą┐ą╗ąŠčēą░ą┤ąĖ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ (ą¤ą¤). ąźąŠčéčÅ, ąĮą░ą▓ąĄčĆąĮąŠąĄ, 4 ą║ąŠčĆą┐čāčüą░ microSOT23-5 ą╝ąŠą│čāčé ą▒čŗčéčī ąĖ ą╝ąĄąĮčīčłąĄ. ąØąŠ čüč湥čéą▓ąĄčĆčæąĮąĮčŗą╣ ą×ąŻ ąĄčüčéčī čā ą╝ąĄąĮčÅ ą▓ ą║ąŠčĆą┐čāčüąĄ DIP! ą×ą┤ąĮą░ą║ąŠ čā ą▓čüąĄčģ č湥čéčŗčĆčæčģ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąĖą║ąŠą▓ ą┐ąĖčéą░ąĮąĖąĄ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠąĄ. ąÉ čŹč鹊 ąĘąĮą░čćąĖčé, čćč鹊 ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ąĮą░ ą×ąŻ ą╝čŗ ą▒čāą┤ąĄą╝ ąĖą╝ąĄčéčī ┬▒UąŠą┐. ą¤čĆąĖčćčæą╝ +UąŠą┐ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą╗ąŠą│ąĖč湥čüą║ąŠą╣ ąĄą┤ąĖąĮąĖčåąĄ, ą░ ŌĆōUąŠą┐ ŌĆö ą╗ąŠą│ąĖč湥čüą║ąŠą╝čā ąĮčāą╗čÄ. ą¦č鹊ą▒čŗ ąĮąĄ čüąČąĄčćčī ą┐ąŠčĆčé ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ čü ą▓čŗčģąŠą┤ą░ ą×ąŻ, ą┐ąŠčüčéą░ą▓ąĖą╝ ą╝ąĄąČą┤čā ąĮąĖą╝ąĖ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓čāčÄčēąĖą╣ ą┤ąĖąŠą┤ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, 1N4148: ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ 4 ąĮčü [5]) ąĖ ąĮą░ ą▓čüčÅą║ąĖą╣ čüą╗čāčćą░ą╣ ą┐čĆąĖčéčÅąĮąĄą╝ ą┐ąŠčĆčé ą║ ąĘąĄą╝ą╗ąĄ čĆąĄąĘąĖčüč鹊čĆąŠą╝ (čé.ąĮ. ┬½pull-down┬╗) ą┤ą╗čÅ čĆą░ąĘčĆčÅą┤ą░ ą▓čüčÅą║ąĖčģ ą│ą░ą┤ą║ąĖčģ ą┐ą░čĆą░ąĘąĖčéąĮčŗčģ ąĄą╝ą║ąŠčüč鹥ą╣, čćč鹊ą▒čŗ ą£ąÜ ą║ąŠčĆčĆąĄą║čéąĮąŠ ąŠčéčĆą░ą▒ą░čéčŗą▓ą░ą╗ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ ┬½0┬╗. ąØąŠą╝ąĖąĮą░ą╗čŗ čĆąĄąĘąĖčüč鹊čĆąŠą▓?.. ąÆąŠąĘčīą╝čæą╝, ą║ ą┐čĆąĖą╝ąĄčĆčā, 10 ą║ą×ą╝: ąĮąĄ ą╝ąĮąŠą│ąŠ ąĖ ąĮąĄ ą╝ą░ą╗ąŠ ą┤ą╗čÅ čåąĖčäčĆąŠą▓ąŠą╣ č鹥čģąĮąĖą║ąĖ. ąØąŠą╝ąĖąĮą░ą╗ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ąŠą▒čüčāą┤ąĖą╝ ą┐ąŠąĘąČąĄ. ą¤ąŠą╗čāč湥ąĮąĮą░čÅ čüčģąĄą╝ą░ ąĖąĘąŠą▒čĆą░ąČąĄąĮą░ ąĮą░ čĆąĖčü.5. ąØą░ čüčģąĄą╝ąĄ ąĮąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ čåąĄą┐ąĖ ą┐ąĖčéą░ąĮąĖčÅ ąĖ čé.ą┐. ąĀąĖčü.5. ąĪčāą╝ą╝ą░č鹊čĆ/ą▓čŗčćąĖčéą░č鹥ą╗čī, ąĖąĮč鹥ą│čĆą░č鹊čĆ ąĖ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ąöąĪą£ ąØą░ ąĮąĄąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĖą╣ ą▓čģąŠą┤ ą×ąĀ1 ą┐ąŠą┤ą░čæčéčüčÅ ą▓čģąŠą┤ąĮąŠąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, ąĮą░ R3 ŌĆö čüąĖą│ąĮą░ą╗ čü ą▓čŗčģąŠą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą░ čüąĖą│ąĮą░ą╗ čü D1 ąĖ R6 ąĘą░ą▓ąŠą┤ąĖčéčüčÅ ą▓ ą£ąÜ. ąöą╗čÅ ą┤ąĄą╝ąŠąĮčüčéčĆą░čåąĖąĖ č鹊ą│ąŠ, ą║ą░ą║ ą┤ąŠą╗ąČąĄąĮ čĆą░ą▒ąŠčéą░čéčī ą╝ąŠą┤čāą╗čÅč鹊čĆ, čÅ ąĮą░ą▒čĆąŠčüą░ą╗ ąĄą│ąŠ ą▒ą╗ąŠą║-čüčģąĄą╝čā (čĆąĖčü.6) ą▓ ą┐ą░ą║ąĄč鹥 Simulink ą┐čĆąŠą│čĆą░ą╝ą╝čŗ Matlab.

ąĀąĖčü.6. ąæą╗ąŠą║-čüčģąĄą╝ą░ ąöąĪą£ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ Simulink ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ą╗ąŠą║ąŠą▓ čüčģąĄą╝čŗ, ąĖąĘąŠą▒čĆą░ąČčæąĮąĮąŠą╣ ąĮą░ čĆąĖčüčāąĮą║ąĄ 6, čüą╗ąĄą▓ą░ ąĮą░ą┐čĆą░ą▓ąŠ: Ramp ąĖ Quantizer ŌĆö ąĖčüč鹊čćąĮąĖą║ ą╗ąĖąĮąĄą╣ąĮąŠ ąĮą░čĆą░čüčéą░čÄčēąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĖ ą║ą▓ą░ąĮč鹊ą▓ą░č鹥ą╗čī čÅą▓ą╗čÅčÄčéčüčÅ ąĖčüč鹊čćąĮąĖą║ąŠą╝ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ┬½ą╗ąĄčüąĄąĮą║ą░┬╗; čüčāą╝ą╝ą░č鹊čĆ/ą▓čŗčćąĖčéą░č鹥ą╗čī (ą×ąĀ2 ąĮą░ čĆąĖčü.5); Gain1 ąĖ IntegratorŌĆö ąĖąĮč鹥ą│čĆą░č鹊čĆ (ą×ąĀ3 ąĮą░ čĆąĖčü.5, čü ą┐ąŠą╝ąŠčēčīčÄ čāčüąĖą╗ąĖč鹥ą╗čÅ Gain1 ąĘą░ą┤ą░čæčéčüčÅ ą┐ąŠčüč鹊čÅąĮąĮą░čÅ ą▓čĆąĄą╝ąĄąĮąĖ ąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░ąĮąĖčÅ R5┬ĘąĪ1); Sign ŌĆö ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ (ą×ąĀ4 ąĮą░ čĆąĖčü.5); Saturation ŌĆö ąŠą│čĆą░ąĮąĖčćąĖč鹥ą╗čī (ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ) čüąĖą│ąĮą░ą╗ą░ (ąĮą░ čĆąĖčü.5 ąĄą│ąŠ čĆąŠą╗čī ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą┤ąĖąŠą┤ D1); Gain2 ŌĆö čāčüąĖą╗ąĖč鹥ą╗čī, ą┤ą╗čÅ ąĮą░ą│ą╗čÅą┤ąĮąŠčüčéąĖ ą╝ą░čüčłčéą░ą▒ąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗; Zero-Order Hold ŌĆö čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓čŗą▒ąŠčĆą║ąĖ-čģčĆą░ąĮąĄąĮąĖčÅ, čüąŠą▓ą╝ąĄčüčéąĮąŠ čü ą║ąŠą╝ą┐ą░čĆą░č鹊čĆąŠą╝ Sign ąŠą▒čĆą░ąĘčāčÄčé ┬½čéą░ą║čéąĖčĆčāąĄą╝čŗą╣ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ┬╗ (ąŠą┤ąĮą░ą║ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ą▓čģąŠą┤ą░ ą║ą░ą║ čéą░ą║ąŠą▓ąŠą│ąŠ čā ąĮąĄą│ąŠ ąĮąĄčé, čüčćąĖčéą░ąĄą╝ čćč鹊 ąŠąĮ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ ąŠą┤ąĮąŠą╣ ąŠą┐čĆąĄą┤ąĄą╗čæąĮąĮąŠą╣ čćą░čüč鹊č鹥), ąĄą│ąŠ čĆąŠą╗čī ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčī ą£ąÜ. ąöą╗čÅ ąĮą░ą▒ą╗čÄą┤ąĄąĮąĖčÅ ąĘą░ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą▓ąĖčĆčéčāą░ą╗čīąĮčŗą╣ čéčĆčæčģą║ą░ąĮą░ą╗čīąĮčŗą╣ ąŠčüčåąĖą╗ą╗ąŠą│čĆą░čä Scope, ąĄą│ąŠ ąŠčüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ ąĮą░ čĆąĖčüčāąĮą║ąĄ 7.

ąĀąĖčü.7. ą×čüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝ą░ čĆą░ą▒ąŠčéčŗ čüčģąĄą╝čŗ, ąĖąĘąŠą▒čĆą░ąČčæąĮąĮąŠą╣ ąĮą░ čĆąĖčü.6 ┬Āą¤ąĄčĆą▓čŗą╣ ą║ą░ąĮą░ą╗ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüčéčāą┐ąĄąĮčćą░č鹊 ąĮą░čĆą░čüčéą░čÄčēąĖą╣ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗, ąĮą░ ą▓č鹊čĆąŠą╣ ą║ą░ąĮą░ą╗ ąĘą░ą▓ąŠą┤ąĖčéčüčÅ čüąĖą│ąĮą░ą╗ čü ą▓čŗčģąŠą┤ą░ ąĖąĮč鹥ą│čĆą░č鹊čĆą░, ą░ ąĮą░ čéčĆąĄčéąĖą╣ ŌĆö čü ą▓čŗčģąŠą┤ą░ ą╝ąŠą┤čāą╗čÅč鹊čĆą░. ąśąĘ čĆąĖčüčāąĮą║ą░ ą▓ąĖą┤ąĮąŠ, čćč鹊 ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ (ą┐ąŠ ą░ą▒čüąŠą╗čÄčéąĮąŠą╝čā ąĘąĮą░č湥ąĮąĖčÄ) ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ ąĖąĮč鹥ą│čĆą░č鹊čĆą░ ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ą┐čĆąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╝/ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╝ ą▓čģąŠą┤ąĮąŠą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ, čé.ą║. ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĮą░ ą▓čģąŠą┤ąĄ ąĖąĮč鹥ą│čĆą░č鹊čĆą░ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ┬▒UąŠą┐. ąśąĮč鹥ą│čĆą░č鹊čĆ ą▒čāą┤ąĄčé čĆą░ą▒ąŠčéą░čéčī ą▓ ą╗ąĖąĮąĄą╣ąĮąŠą╝ čĆąĄąČąĖą╝ąĄ, ąĄčüą╗ąĖ ą▓ č鹥č湥ąĮąĖąĄ ąŠą┤ąĮąŠą│ąŠ čéą░ą║čéą░ ąöąĪą£ ą┐čĆąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ ąĮą░ ą▓čģąŠą┤ąĄ, ąĮą░ ą▓čŗčģąŠą┤ąĄ ąŠąĮąŠ ąĮąĄ ą┐čĆąĄą▓čŗčüąĖčé ą┐ą░čüą┐ąŠčĆčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠą│ąŠ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ Umax (ą×ąĀ3 ąĮą░ čĆąĖčü.5). ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ą║čĆąĖč鹥čĆąĖąĄą╝ ą▓čŗą▒ąŠčĆą░ ąĪ1 (ąĮą░ čĆąĖčü.5) čÅą▓ą╗čÅąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĮąĄčĆą░ą▓ąĄąĮčüčéą▓ą░

, ą│ą┤ąĄ ąóą┤čüą╝ ŌĆö ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ąŠą┤ąĮąŠą│ąŠ čéą░ą║čéą░ ą╝ąŠą┤čāą╗čÅč鹊čĆą░ (ąóą┤čüą╝ = 1/fčéą░ą║čé = 1/Fs). ą¤čĆąĖ čŹč鹊ą╝ ąĮąĄ čüą╗ąĄą┤čāąĄčé ą▒čĆą░čéčī ąĪ1 ąĮą░ą╝ąĮąŠą│ąŠ ą▒ą×ą╗čīčłąĖą╝, čé.ą║. ą┐čĆąĖ čŹč鹊ą╝ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ ą┐ąŠčüč鹊čÅąĮąĮą░čÅ ąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░ąĮąĖčÅ, ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ ąĖąĮč鹥ą│čĆą░č鹊čĆą░ ą▒čāą┤ąĄčé ą║ąŠą╗ąĄą▒ą░čéčīčüčÅ ą▓ čĆą░ą╣ąŠąĮąĄ ąĮčāą╗čÅ čü ą╝ą░ą╗ąĄąĮčīą║ąŠą╣ ą░ą╝ą┐ą╗ąĖčéčāą┤ąŠą╣. ąÜą░ą║ čüą╗ąĄą┤čüčéą▓ąĖąĄ, čüąĖą╗čīąĮąĄąĄ ą▒čāą┤čāčé ą┐čĆąŠčÅą▓ą╗čÅčéčīčüčÅ ąĮąĄąĖą┤ąĄą░ą╗čīąĮąŠčüčéąĖ ą×ąŻ: ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ čüą╝ąĄčēąĄąĮąĖčÅ, ą▓čģąŠą┤ąĮčŗąĄ č鹊ą║ąĖ čüą╝ąĄčēąĄąĮąĖčÅ ąĖ ąĖčģ čĆą░ąĘąĮąŠčüčéčī ąĖ čé.ą┐. ąØą░ ą╝ąŠą╣ ą▓ąĘą│ą╗čÅą┤, ąĪ1 čüą╗ąĄą┤čāąĄčé ą▓čŗą▒čĆą░čéčī čéą░ą║ąĖą╝, čćč鹊ą▒čŗ ąĘą░ ąŠą┤ąĖąĮ čéą░ą║čé ą╝ąŠą┤čāą╗čÅč鹊čĆą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ ąĖąĮč鹥ą│čĆą░č鹊čĆą░ ąĮą░čĆą░čüčéą░ą╗ąŠ ąĮą░ 85ŌĆ”95% ąŠčé Umax. ┬ĀąĪąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą╝ąŠą┤čāą╗čÅč鹊čĆą░ č湥ą╝-č鹊 ą┐ąŠčģąŠąČ ąĮą░ čĆąĄąĘčāą╗čīčéą░čé čłąĖčĆąŠčéąĮąŠ-ąĖą╝ą┐čāą╗čīčüąĮąŠą╣ ą╝ąŠą┤čāą╗čÅčåąĖąĖ (ą©ąśą£), ąĮąŠ čü čłąĖčĆąĖąĮąŠą╣ ąĖą╝ą┐čāą╗čīčüą░ ą║čĆą░čéąĮąŠą╣ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąŠą┤ąĮąŠą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░. ą×ą┐ąŠčĆąĮąŠąĄ ┬½ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ┬╗ čüčģąĄą╝čŗ, ąĖąĘąŠą▒čĆą░ąČčæąĮąĮąŠą╣ ąĮą░ čĆąĖčü.6 (ą┤ą╗čÅ ąĮą░ą│ą╗čÅą┤ąĮąŠčüčéąĖ ąĮą░ąĘąŠą▓čæą╝ čüąĖą│ąĮą░ą╗ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝, ąŠą┤ąĮą░ą║ąŠ čüą░ą╝ą░ ą╝ąŠą┤ąĄą╗čī ąĖąĮą▓ą░čĆąĖą░ąĮčéąĮą░ ą║ ą┐čĆąĖčĆąŠą┤ąĄ čüąĖą│ąĮą░ą╗ą░: ąŠąĮ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ą░ąČąĄ čåąĖčäčĆąŠą▓čŗą╝) čĆą░ą▓ąĮąŠ 5 ąÆ, ą┐ąĄčĆą▓ą░čÅ čüčéčāą┐ąĄąĮčīą║ą░ ąĖą╝ąĄąĄčé ą▓ąĄą╗ąĖčćąĖąĮčā 1 ąÆ, čé.ąĄ. ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ čĆą░ą▓ąĄąĮ 1/5┬ĘUąŠą┐. ąóą░ą║ąŠąĄ ą┐čĆąŠčüč鹊ąĄ čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ č鹊ą╝čā, čćč鹊 č湥čéčŗčĆąĄ čéą░ą║čéą░ ą╝ąŠą┤čāą╗čÅč鹊čĆ ą▓čŗą┤ą░čæčé ┬½0┬╗, ąĖ ą║ą░ąČą┤čŗą╣ ą┐čÅčéčŗą╣ čéą░ą║čé ┬½1┬╗. ąĪ č鹊čćąĮąŠčüčéčīčÄ, ą┤ą░ ąĮą░ąŠą▒ąŠčĆąŠčé ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą║ąŠą│ą┤ą░ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ čĆą░ą▓ąĄąĮ 4 ąÆ, čé.ąĄ. 4/5┬ĘUąŠą┐. ąÆ čŹčéąĖčģ ą┤ą▓čāčģ čüą╗čāčćą░čÅčģ ąŠčéą╗ąĖčćąĖą╣ ąŠčé ą║ą╗ą░čüčüąĖč湥čüą║ąŠą╣ ą©ąśą£ ąĮąĄčé. ąÜąŠą│ą┤ą░ ąĮą░ ą▓čģąŠą┤ąĄ 2 ąĖą╗ąĖ 3 ą▓ąŠą╗čīčéą░, ąĮą░ ą▓čŗčģąŠą┤ąĄ ą╝ąŠą┤čāą╗čÅč鹊čĆą░ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą┤ą▓ąĄ ąĖą╗ąĖ čéčĆąĖ ┬½1┬╗ ąĖąĘ ą╗čÄą▒čŗčģ ą┐čÅčéąĖ ą▒ąĖčé (ąĖą┤čāčēąĖčģ ą┐ąŠą┤čĆčÅą┤ čéą░ą║č鹊ą▓). ąØąŠ! ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ: ąŠąĮąĖ ą┐ąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ č湥čĆąĄą┤čāčÄčéčüčÅ čü ąĮčāą╗čÅą╝ąĖ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ąŠą▒čŗčćąĮą░čÅ ą©ąśą£ ą┤ą░ą╗ą░ ą▒čŗ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ┬½11000┬╗ ąĖ ┬½11100┬╗ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▒ąŠą╗čīčłąĄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖą╣ ą╝ąĄąČą┤čā ┬½0┬╗ ąĖ ┬½1┬╗, čé.ąĄ. ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą╝ąŠą┤čāą╗čÅč鹊čĆą░ čüąŠą┤ąĄčƹȹĖčé ą▒ąŠą╗čīčłąĄ ą▓čŗčüąŠą║ąŠčćą░čüč鹊čéąĮčŗčģ čüąŠčüčéą░ą▓ą╗čÅčÄčēąĖčģ, ą║ąŠč鹊čĆčŗąĄ ą╗ąĄą│č湥 ąŠčéčäąĖą╗čīčéčĆąŠą▓ą░čéčī! ąōąŠą▓ąŠčĆčÅ čāą╝ąĮčŗą╝ čÅąĘčŗą║ąŠą╝, ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄ čéą░ą║ąŠą╣ čüčéčĆčāą║čéčāčĆčŗ ą╝ąŠą┤čāą╗čÅč鹊čĆą░ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÄ čé.ąĮ. čŹčäč乥ą║čéą░ ą▓čŗč鹥čüąĮąĄąĮąĖčÅ čłčāą╝ą░ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ ą▓ ąŠą▒ą╗ą░čüčéčī ą▓čŗčüąŠą║ąĖčģ čćą░čüč鹊čé. ąÆ ą║ą░č湥čüčéą▓ąĄ ą┐čĆąĖą╝ąĄčĆą░ ąĮą░ čĆąĖčü.8 ą┐ąŠą║ą░ąĘą░ąĮą░ ąŠčåąĄąĮą║ą░ čüą┐ąĄą║čéčĆą░ą╗čīąĮąŠą╣ ą┐ą╗ąŠčéąĮąŠčüčéąĖ čüčĆąĄą┤ąĮąĄą╣ ą╝ąŠčēąĮąŠčüčéąĖ (ąĪą¤ąĪą£) čüąĖą│ąĮą░ą╗ą░ ąŠą┤ąĮąŠčĆą░ąĘčĆčÅą┤ąĮąŠą│ąŠ ąöąĪą£ ą▓č鹊čĆąŠą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░, ąĖą╝ąĄčÄčēąĄą│ąŠ čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā 100 ą£ąōčå, ą┐čĆąĖ čćą░čüč鹊č鹥 ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ 24,4 ą║ąōčå (ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą▓čŗą▒ąŠčĆą║ąĖ 2^20) [2]. ąĪąŠą┐ąŠčüčéą░ą▓ą╗čÅčÅ ą┤ą▓ąĄ čŹčéąĖ čåąĖčäčĆčŗ: čéą░ą║č鹊ą▓čāčÄ 100 ą£ąōčå (!) ąĖ čüąĖą│ąĮą░ą╗ ┬½ą▓čüąĄą│ąŠ ą╗ąĖčłčī┬╗ 24 ą║ąōčå, ą╝ąŠąČąĮąŠ ąĘą░ą║ą░čéą░čéčī ą│čāą▒čā ąĮą░ č鹊, čćč鹊 ą▓ ąĖč鹊ą│ąĄ ą╝čŗ ą┐ąŠą╗čāčćąĖą╝ č鹊čćąĮčŗą╣ ąĖ ą┐čĆąĖ čŹč鹊ą╝ ą▒čŗčüčéčĆčŗą╣ ąÉą”ą¤.

ąĀąĖčü.8. ąĪą¤ąĪą£ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąöąĪ ą╝ąŠą┤čāą╗čÅč鹊čĆą░ ąĖ ąśąÜą£ ąÉą”ą¤ č鹊ą╣ ąČąĄ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ ąÆąĖą┤ąĮąŠ, čćč鹊 ą▓ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ąĖą╝ą┐čāą╗čīčüąĮąŠ-ą║ąŠą┤ąŠą▓čŗčģ ąÉą”ą¤ (ąśąÜą£ ąÉą”ą¤), ąĪą¤ąĪą£ čłčāą╝ą░ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ ąĮąŠčüąĖčé ąĮąĄ čĆą░ą▓ąĮąŠą╝ąĄčĆąĮčŗą╣ čģą░čĆą░ą║č鹥čĆ, ą░ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ čü čĆąŠčüč鹊ą╝ čćą░čüč鹊čéčŗ. ą¤čĆąĖ čŹč鹊ą╝ ą▓ ąĮąĖąĘą║ąŠčćą░čüč鹊čéąĮąŠą╣ ąŠą▒ą╗ą░čüčéąĖ čüą┐ąĄą║čéčĆą░ ąĪą¤ąĪą£ čłčāą╝ą░ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ ąĮąĖąČąĄ, č湥ą╝ čā ąĖą╝ą┐čāą╗čīčüąĮąŠ-ą║ąŠą┤ąŠą▓čŗčģ ąÉą”ą¤ čü č鹊ą╣ ąČąĄ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčīčÄ ąĖ čćą░čüč鹊č鹊ą╣ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ. ą¤ąŠą┤ą░ą▓ą╗čÅčÅ ą▓čŗčüąŠą║ąŠčćą░čüč鹊čéąĮčŗąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ čłčāą╝ą░ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ čü ą┐ąŠą╝ąŠčēčīčÄ ążąØą¦, ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ąĮą░ ą▓čŗčģąŠą┤ąĄ ąÉą”ą¤ čåąĖčäčĆąŠą▓ąŠą╣ čüąĖą│ąĮą░ą╗ čü ą▓čŗčüąŠą║ąĖą╝ ąŠčéąĮąŠčłąĄąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗/čłčāą╝, čé.ąĄ. čü ą▓čŗčüąŠą║ąŠą╣ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčīčÄ. ąśčéą░ą║, ąĮą░ą╝ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī čåąĖčäčĆąŠą▓ąŠą╣ ą┤ąĄčåąĖą╝ąĖčĆčāčÄčēąĖą╣ čäąĖą╗čīčéčĆ. Tiny2313 čÅą▓ą╗čÅąĄčéčüčÅ ┬½ą▓čüąĄą│ąŠ ą╗ąĖčłčī┬╗ 8-ą╝ąĖ čĆą░ąĘčĆčÅą┤ąĮčŗą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ čü čüąŠą║čĆą░čēčæąĮąĮčŗą╝ ąĮą░ą▒ąŠčĆąŠą╝ ą║ąŠą╝ą░ąĮą┤ (ą┐ąŠ-ą▒čāčĆąČčāą╣čüą║ąĖ RISC) [6], čé.ąĄ. ą┤ą░ą╗ąĄą║ąŠ ąĮąĄ čåąĖčäčĆąŠą▓ąŠą╣ čüąĖą│ąĮą░ą╗čīąĮčŗą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ (DSP), čā ą║ąŠč鹊čĆąŠą│ąŠ čāąČąĄ ąĄčüčéčī ąĮą░ą▒ąŠčĆ ą│ąŠč鹊ą▓čŗčģ ą║ąŠą╝ą░ąĮą┤ ą┤ą╗čÅ čåąĖčäčĆąŠą▓ąŠą╣ čäąĖą╗čīčéčĆą░čåąĖąĖ. ąóą░ą║ čćč鹊 ą┐čĆąĖą┤čæčéčüčÅ ąĮąĄą╝ąĮąŠą│ąŠ ą┐ąŠąĖąĘą│ą░ą╗čÅčéčīčüčÅ. ążąĖą╗čīčéčĆ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 ą╝ąŠą┤čāą╗čÅč鹊čĆą░, ą┐ąŠčŹč鹊ą╝čā ąŠąĮ ą┤ąŠą╗ąČąĄąĮ ąŠą▒ą╗ą░ą┤ą░čéčī ą┤ąŠčüčéą░č鹊čćąĮąŠ ą┐čĆąŠčüč鹊ą╣ čüčéčĆčāą║čéčāčĆąŠą╣, čéą░ą║ čćč鹊 čĆąĄą░ą╗ąĖąĘčāąĄą╝ ążąØą¦ čü ą║ąŠąĮąĄčćąĮąŠą╣ ąĖą╝ą┐čāą╗čīčüąĮąŠą╣ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąŠą╣ (ąÜąśąź). ą×ą┤ąĮąĖą╝ ąĖąĘ ą▓ąŠąĘą╝ąŠąČąĮčŗčģ čĆąĄčłąĄąĮąĖą╣ čÅą▓ą╗čÅąĄčéčüčÅ čĆąĄčłąĄąĮąĖąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ążąØą¦, ąĮąĄ ąĖą╝ąĄčÄčēąĖą╣ ą▓ čüą▓ąŠąĄą╝ čüąŠčüčéą░ą▓ąĄ čāą╝ąĮąŠąČąĖč鹥ą╗ąĄą╣, čéą░ą║ąŠą╣ čéąĖą┐ čäąĖą╗čīčéčĆ ą▓ ą░ąĮą│ą╗ąŠčÅąĘčŗčćąĮąŠą╣ ą╗ąĖč鹥čĆą░čéčāčĆąĄ ą┐ąŠą╗čāčćąĖą╗ ąĮą░ąĘą▓ą░ąĮąĖąĄ sinc-čäąĖą╗čīčéčĆąŠą▓, ą┐ąŠčüą║ąŠą╗čīą║čā ąÉą¦ąź čäąĖą╗čīčéčĆą░ ą┐čĆąŠą┐ąŠčĆčåąĖąŠąĮą░ą╗čīąĮą░ sin(ωt)/ωt:

(1). ą¤ąĄčĆąĄą┤ą░č鹊čćąĮą░čÅ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ čäąĖą╗čīčéčĆą░ ą▓ Z-ąŠą▒ą╗ą░čüčéąĖ:

(2). ąźąŠč鹥ą╗ ąĮą░ą┐ąĖčüą░čéčī čćč鹊-č鹊 ą▓čĆąŠą┤ąĄ ┬½ąĖąĘ (2) ą▓ąĖą┤ąĮąŠ, čćč鹊┬╗ŌĆ” ąØąŠ, ą┤čāą╝ą░čÄ, ą▓ąĖą┤ąĮąŠ ą▒čāą┤ąĄčé ą┤ą░ą╗ąĄą║ąŠ ąĮąĄ ą╝ąĮąŠą│ąĖą╝. ąĢčüą╗ąĖ ą┐ąŠą┐čĆąŠą▒ąŠą▓ą░čéčī ąŠą▒čŖčÅčüąĮąĖčéčī ą▓ ą┤ą▓čāčģ čüą╗ąŠą▓ą░čģ, č鹊 z^(-i) ŌĆö čŹč鹊 ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗, ąĘą░ą┤ąĄčƹȹ░ąĮąĮčŗą╣ ąĮą░ i čéą░ą║č鹊ą▓. ąó.ąĄ. ąĮą░ą╝ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐čĆąŠčüčāą╝ą╝ąĖčĆąŠą▓ą░čéčī ą£ ąĘąĮą░č湥ąĮąĖą╣ čüąĖą│ąĮą░ą╗ą░, ąĘą░ą┤ąĄčƹȹ░ąĮąĮąŠą│ąŠ ąĮą░ 0, 1, ŌĆ”, N-2, N-1 čéą░ą║č鹊ą▓. ąÆ ą║ą╗ą░čüčüąĖč湥čüą║ąŠą╣ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╣ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ čŹč鹊 ą┤ąĄą╗ą░ąĄčéčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ ą┐ąŠą┤ąŠą▒ąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ-ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ąĖ čüčāą╝ą╝ą░č鹊čĆą░ (čüą╝. čĆąĖčü.9).

ąĀąĖčü.9. ąĪčéčĆčāą║čéčāčĆąĮą░čÅ čüčģąĄą╝ą░ sinc-čäąĖą╗čīčéčĆą░ ąÆ ąŠą▒čēąĄą╝ čüą╗čāčćą░ąĄ, ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ Y[n] ą╝ąĄąĮčÅąĄčéčüčÅ čü ą║ą░ąČą┤čŗą╝ čéą░ą║č鹊ą╝ ą▓čģąŠą┤ąĮąŠą│ąŠ. ą×č湥ą▓ąĖą┤ąĮąŠ, čćč鹊 čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī Y[n] ą▓čŗčłąĄ, č湥ą╝ X[n]. ą¤čĆąĖą╝ąĄąĮąĖč鹥ą╗čīąĮąŠ ą║ ąĮą░čłąĄą╝čā čüą╗čāčćą░čÄ, čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ (čü ą▓čŗčģąŠą┤ą░ ąöąĪą£) čĆą░ą▓ąĮą░ ąĄą┤ąĖąĮąĖčåąĄ. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą▒čāą┤ąĄčé ą▓ č鹊ą╝ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ ąĮą░ ą▓čģąŠą┤ąĄ ą▒čāą┤ąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĄą┤ąĖąĮąĖčå. ą¤čĆąĖ čŹč鹊ą╝ ą▓ čüčāą╝ą╝ą░č鹊čĆąĄ ą▒čāą┤ąĄčé čćąĖčüą╗ąŠ N, ą┤ą╗čÅ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖčÅ ą║ąŠč鹊čĆąŠą│ąŠ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ L čĆą░ąĘčĆčÅą┤ąŠą▓ (2^L > N). ąĀąĄą░ą╗ąĖąĘąŠą▓ą░čéčī čéą░ą║ąŠą╣ čäąĖą╗čīčéčĆ ą▓čŗčüąŠą║ąŠą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ą▓ ą£ąÜ ą┤ąŠčüčéą░č鹊čćąĮąŠ ą┐čĆąŠą▒ą╗ąĄą╝ą░čéąĖčćąĮąŠ. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ą▓čüą┐ąŠą╝ąĮąĖčéčī, čćč鹊 čüą╗ąĄą┤ąŠą╝ ąĘą░ čäąĖą╗čīčéčĆąŠą╝ čā ąĮą░čü ąĖą┤čæčé ą┤ąĄčåąĖą╝ą░č鹊čĆ, č鹊 ą▓čüčæ ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ čāą┐čĆąŠčēą░ąĄčéčüčÅ. ąĢčüą╗ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄčåąĖą╝ą░čåąĖąĖ ą£ čā ąĮą░čü ą▒čāą┤ąĄčé čĆą░ą▓ąĮčÅčéčīčüčÅ čćąĖčüą╗čā ą▓čģąŠą┤ąŠą▓ čüčāą╝ą╝ą░č鹊čĆą░ N, č鹊 ą▓ ą║ą░č湥čüčéą▓ąĄ čüčāą╝ą╝ą░č鹊čĆą░ ą╝ąŠąČąĮąŠ ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ (čĆąĖčü.10)!

ąĀąĖčü.10. ąĪčéčĆčāą║čéčāčĆąĮą░čÅ čüčģąĄą╝ą░ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░ ąĀąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ ą▓ ą£ąÜ ą┤ąŠčüčéą░č鹊čćąĮąŠ ą┐čĆąŠčüč鹊: ąĮą░ą┤ąŠ ą╗ąĖčłčī ą┐čĆąĖą▒ą░ą▓ą╗čÅčéčī ąĘąĮą░č湥ąĮąĖąĄ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą║ čüąŠą┤ąĄčƹȹĖą╝ąŠą╝čā ą║ą░ą║ąŠą│ąŠ-ą╗ąĖą▒ąŠ čĆąĄą│ąĖčüčéčĆą░. ąÉ ą┐čĆąŠčåąĄčüčü ą┤ąĄčåąĖą╝ą░čåąĖąĖ ą▒čāą┤ąĄčé ąĘą░ą║ą╗čÄčćą░čéčīčüčÅ ą▓ č鹊ą╝, čćč鹊ą▒čŗ ą║ą░ąČą┤čŗąĄ ą£ čéą░ą║č鹊ą▓ (ą┐ąŠčüą╗ąĄ ą┐čĆąĖčģąŠą┤ą░ ą£ ą▒ąĖčé) X[n] ą▓čŗą┤ą░ą▓ą░čéčī ąĘąĮą░č湥ąĮąĖąĄ Y[n] čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ L ąĖ ąŠą▒ąĮčāą╗čÅčéčī ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ. ąØą░ čĆąĖčüčāąĮą║ąĄ 11 ą┐ąŠą║ą░ąĘą░ąĮą░ ą░ą╝ą┐ą╗ąĖčéčāą┤ąĮąŠ-čćą░čüč鹊čéąĮą░čÅ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ (ąÉą¦ąź) čéą░ą║ąŠą│ąŠ čäąĖą╗čīčéčĆą░ ą┐čĆąĖ ą£ = 65535 (MathCAD ą┐ąŠą┤ą▓ąĖčüą░ą╗ ą┐ąŠčćčéąĖ ąĮą░ čéčĆąĖ ą╝ąĖąĮčāčéčŗ čćč鹊ą▒čŗ ą┐ąŠčüčéčĆąŠąĖčéčī čéą░ą║ąŠąĄ).

ąĀąĖčü.11. ąÉą¦ąź sinc-čäąĖą╗čīčéčĆą░ ą┐čĆąĖ N = 65535 ąśčéą░ą║, ą▓čŗčĆąĖčüąŠą▓čŗą▓ą░ąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╣ ą░ą╗ą│ąŠčĆąĖčéą╝ čĆą░ą▒ąŠčéčŗ ą£ąÜ: 0) ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ; 1) čüčćąĖčéčŗą▓ą░ąĄą╝ ą▒ąĖčé čü ą▓čŗčģąŠą┤ą░ ą╝ąŠą┤čāą╗čÅč鹊čĆą░; 2) ą┐ąĄčĆąĄą┤ą░čæą╝ ąĄą│ąŠ ąĘąĮą░č湥ąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤; 3) ą┐čĆąĖą▒ą░ą▓ą╗čÅąĄą╝ čŹč鹊čé ą▒ąĖčé ą║ ąĘąĮą░č湥ąĮąĖčÄ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░; 4) čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄą╝ ąĘąĮą░č湥ąĮąĖąĄ čüčćčæčéčćąĖą║ą░; 5) ąĄčüą╗ąĖ čüčćčæčéčćąĖą║ ąĮąĄ ą┤ąŠčéąĖą║ą░ą╗ ą┤ąŠ ą£, č鹊 ą┐ąĄčĆąĄčģąŠą┤ ą║ ą┐.1; 6) ą┐ąŠą╗čāčćąĖą╗ąĖ čĆąĄąĘčāą╗čīčéą░čé ą▓ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆąĄ. ą£ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ą▓ą║ą╗čÄčćą░ąĄčé ą▓ čüąĄą▒čÅ ąŠą▒ąĮčāą╗ąĄąĮąĖąĄ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░ ąĖ čüčćčæčéčćąĖą║ą░. ąÜą░ą║ ą▓ąĖą┤ąĮąŠ, ąĮą░ ą║ą░ąČą┤čŗą╣ čéą░ą║čé ą╝ąŠą┤čāą╗čÅč鹊čĆą░ čāčģąŠą┤ąĖčé ą╝ąĖąĮąĖą╝čāą╝ 5 čéą░ą║č鹊ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą░ ąĄčüą╗ąĖ čāč湥čüčéčī, čćč鹊 ąĮąĄą║ąŠč鹊čĆčŗąĄ ą║ąŠą╝ą░ąĮą┤čŗ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ ą▒ąŠą╗ąĄąĄ ąŠą┤ąĮąŠą│ąŠ čéą░ą║čéą░, č鹊 ąĖ ą▓čüąĄ 10 (ą┤ąĄčüčÅčéčī)! ą¤čĆąĖ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 ą£ąÜ 1 ą£ąōčå ąĮą░ ąĮą░ą║ąŠą┐ą╗ąĄąĮąĖąĄ 65535 ąŠčéčüčćčæč鹊ą▓ (čĆą░ąĘ ą┐čĆąĄąĖą╝čāčēąĄčüčéą▓ąŠą╝ ą┤ąĄą╗čīčéą░-čüąĖą│ą╝ą░ ąÉą”ą¤ čÅą▓ą╗čÅąĄčéčüčÅ ą┐ąŠą▓čŗčłąĄąĮąĮą░čÅ č鹊čćąĮąŠčüčéčī, ą┐ąŠą┐čĆąŠą▒čāąĄą╝ ą┐čĆąŠą▓ąĄčĆąĖčéčī čéą░ą║ ą╗ąĖ čŹč鹊 ąĖ ą┐ąŠą╗čāčćąĖčéčī čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ 16 ą▒ąĖčé) čā ąĮą░čü čāą╣ą┤čæčé ą┤ą▓ąĄ čéčĆąĄčéąĖ čüąĄą║čāąĮą┤čŗ!!! ąźąŠčéčÅ ą┤ą╗čÅ ą▓ąŠą╗čīčéą╝ąĄčéčĆą░ ą┐ąŠčüč鹊čÅąĮąĮąŠą│ąŠ č鹊ą║ą░ ą▓ą┐ąŠą╗ąĮąĄ čüą│ąŠą┤ąĖčéčüčÅ. ąĀą░čüčüą╝ąŠčéčĆąĖą╝ č鹥ą┐ąĄčĆčī ą┐ąŠą┤čĆąŠą▒ąĮąĄą╣ ą║ą░ąČą┤čŗą╣ ą┐čāąĮą║čé, ąŠčĆąĖąĄąĮčéąĖčĆčāčÅčüčī ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆ AVR. ąæčāą┤ąĄčé čĆą░čüčüą╝ąŠčéčĆąĄąĮ ąĮą░ąĖą╗čāčćčłąĖą╣ čüą╗čāčćą░ą╣ čü č鹊čćą║ąĖ ąĘčĆąĄąĮąĖčÅ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖčÅ ąĖ ąĘą░ąĮčÅč鹊čüčéąĖ ą┐ąŠčĆč鹊ą▓ ą£ąÜ: ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮčŗ ąĀąÉ0 ąĖ ąĀąÉ1 ATtiny2313. ą¤ąŠčĆčé ąÉ čéčĆčæčģą▒ąĖčéąĮčŗą╣, ąĮąŠ čüčéą░čĆčłąĖą╣ ą▒ąĖčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ čĆąĄčüąĄčéą░. ąöą╗čÅ ąŠčüčéą░ą╗čīąĮčŗčģ čüą╗čāčćą░ąĄą▓ ą▒čāą┤čāčé ą┤ą░ąĮčŗ čĆąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖąĖ, ą░ ą║ąŠą┤ ąĘą░ą║ąŠą╝ą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮ. 0. ą×ą┤ąĖąĮ čåąĖą║ą╗ čĆą░ą▒ąŠčéčŗ 16-čéąĖ ą▒ąĖčéąĮąŠą│ąŠ ąÉą”ą¤ ą╝ąĮąĄ čāą┤ą░ą╗ąŠčüčī ą▓ą┐ąĖčģąĮčāčéčī ą▓ 9 čéą░ą║č鹊ą▓ ą£ąÜ (č鹥ąŠčĆąĄčéąĖč湥čüą║ąĖ, ą╝ąŠąČąĮąŠ čāą╝ąĄčüčéąĖčéčīčüčÅ ą▓ 8). ąØą░ čŹč鹊 čā ą╝ąĄąĮčÅ čāčłą╗ąŠ 6 čĆąĄą│ąĖčüčéčĆąŠą▓: ą┤ą▓ą░ ą┐ąŠą┤ čĆąĄąĘčāą╗čīčéą░čé, ą┤ą▓ą░ ą┤ą╗čÅ čüčćčæčéčćąĖą║ą░, ąŠą┤ąĖąĮ ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖą╣ ąĖ ąŠą┤ąĖąĮ ┬½ąĮčāą╗ąĄą▓ąŠą╣┬╗ (ąĮąĄ R0, ą░ ą┐čĆąŠčüč鹊 ą▓ ąĮčæą╝ ą▓čüčæ ą▓čĆąĄą╝čÅ ąŠą┤ąĮąĖ ąĮčāą╗ąĖ, čé.ąĄ. 0b00000000). ąĪčćčæčéčćąĖą║ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĮčŗą╣, čé.ąĄ. ą║ą░ąČą┤čŗą╣ čéą░ą║čé ą╝ąŠą┤čāą╗čÅč鹊čĆą░ čāą╝ąĄąĮčīčłą░ąĄčé čüą▓ąŠčæ ąĘąĮą░č湥ąĮąĖąĄ. ąöą╗čÅ čüčćčæčéčćąĖą║ą░ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą▓čŗą▒čĆą░čéčī ą┐ą░čĆčā čĆąĄą│ąĖčüčéčĆąŠą▓ Rd+1:Rd, d={24, 26, 28, 30} (čé.ąĄ. č鹥, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą┐ą░ą┤ą░čÄčé ą┐ąŠą┤ ą┤ąĄą╣čüčéą▓ąĖąĄ ą║ąŠą╝ą░ąĮą┤ ADIW ąĖ SBIW). ą» ą▓čŗą▒čĆą░ą╗ R24 ąĖ R25 čćč鹊ą▒čŗ ąĮąĄ ąĘą░ąĮąĖą╝ą░čéčī čĆąĄą│ąĖčüčéčĆčŗ X, Y ąĖ Z. ą¤ą░čĆą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐ąŠą┤ čĆąĄąĘčāą╗čīčéą░čé ŌĆö ą╗čÄą▒ą░čÅ čüąŠčüąĄą┤ąĮčÅčÅ. ąæčŗą╗ą░ ą▓čŗą▒čĆą░ąĮą░ ą┐ą░čĆą░ R20 ąĖ R21. ąöą╗čÅ ┬½ąĮčāą╗ąĄą▓ąŠą│ąŠ┬╗ čĆąĄą│ąĖčüčéčĆą░ ą┐ąŠą┤ąŠą╣ą┤čæčé ą╗čÄą▒ąŠą╣, ą▓čŗą▒čĆą░ąĮ R0. ąĀąĄą│ąĖčüčéčĆ ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖą╣ ŌĆö ą╗čÄą▒ąŠą╣ ąĖąĘ 16-čéąĖ čüčéą░čĆčłąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (ąĀą×ąØ), ą▓čŗą▒čĆą░ąĮ R16. ąśčéą░ą║, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąŠą▒ąĮčāą╗ąĖčéčī čéčĆąĖ čĆąĄą│ąĖčüčéčĆą░ ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčī ą┤ą▓ą░. ą¦č鹊ą▒čŗ ąĮąĄ ąĘą░ą┐čāčéą░čéčīčüčÅ, ą┐čĆąĖčüą▓ąŠąĖą╝ ąĖą╝ ąĖą╝ąĄąĮą░. //ą┐ąŠą┤ą║ą╗čÄčćą░ąĄą╝ ąĘą░ą│ąŠą╗ąŠą▓ąŠčćąĮčŗą╣ čäą░ą╣ą╗ .include //ąŠą▒ąĘčŗą▓ą░ąĄą╝ čĆąĄą│ąĖčüčéčĆčŗ .def zeroreg = R0┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ąĮčāą╗ąĄą▓ąŠą╣ čĆąĄą│ąĖčüčéčĆ .def tmp = R16┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖą╣ .def resultL = R20┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé čĆąĄąĘčāą╗čīčéą░čéą░ .def resultH = R21┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ąĖ čüčéą░čĆčłąĖą╣ .def countL = R24┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé čüčćčæčéčćąĖą║ą░ .def countH = R25┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ąĖ čüčéą░čĆčłąĖą╣ //ąĮą░čüčéčĆą░ąĖą▓ą░ąĄą╝ ą┐ąŠčĆčéčŗ ą▓ą▓ąŠą┤ą░-ą▓čŗą▓ąŠą┤ą░ SBI DDRA,0┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ą┐ąŠčĆčéąÉ.0 ąĮą░ ą▓čŗčģąŠą┤ //CBI DDRA,1┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐ąŠčĆčéąÉ.1 ąĮą░čüčéčĆąŠąĄąĮ ąĮą░ ą▓čģąŠą┤ //ąĖčéą░ą║, ą┐ąŠąĄčģą░ą╗ąĖ! ADC_start:┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;čüčéą░ą▓ąĖą╝ ą╝ąĄčéą║čā ąĮą░čćą░ą╗ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čāą┤ąŠą▒čüčéą▓ą░ ą┐ąĄčĆąĄčģąŠą┤ą░ NOP┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ą┐čĆąŠčüč鹊 čćč鹊ą▒čŗ ąĮąĄ ąĘą░ą▒čŗčéčī, ąĮąĖąČąĄ ąĮą░ą┐ąĖčłčā ąĘą░č湥ą╝ CLR zeroreg┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ąŠą▒ąĮčāą╗ąĖą╗ąĖ ┬½ąĮčāą╗ąĄą▓ąŠą╣┬╗ čĆąĄą│ąĖčüčéčĆ //ąĄčüą╗ąĖ R0 ą▒ąŠą╗čīčłąĄ ąĮąĖą│ą┤ąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, č鹊 ąĄą│ąŠ ą┤ąŠčüčéą░č鹊čćąĮąŠ ąŠą▒ąĮčāą╗ąĖčéčī ąŠą┤ąĖąĮ čĆą░ąĘ CLR resultL┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ąŠą▒ąĮčāą╗čÅąĄą╝ čĆąĄąĘčāą╗čīčéą░čé CLR resultH┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;(ąŠą▒ą░ ą▒ą░ą╣čéą░) SER countL┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄą╝ čüčćčæčéčćąĖą║, SER countH┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;čé.ąĄ. ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝ ą▓ ąĮąĄą│ąŠ $FFFF = 65535 1. ąĪčćąĖčéčŗą▓ą░ąĄą╝ ą▒ąĖčé čü ą▓čŗčģąŠą┤ą░ ą╝ąŠą┤čāą╗čÅč鹊čĆą░. ąóčāčé ą▓čüčæ ą┐čĆąŠčüč鹊: čüąŠčģčĆą░ąĮčÅąĄą╝ ą▓ tmp ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ PINA. 1 čéą░ą║čé. ADC_count:┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ą╝ąĄčéą║ą░ ąĮą░čćą░ą╗ą░ čåąĖą║ą╗ą░ čäąĖą╗čīčéčĆą░čåąĖąĖ IN tmp, PINA┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;čüčćąĖčéčŗą▓ą░ąĄą╝ ąĘąĮą░č湥ąĮąĖąĄ 2. ą¤ąĄčĆąĄą┤ą░čæą╝ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą▒ąĖčéą░ ąĮą░ ą▓čŗčģąŠą┤, čé.ąĄ. ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝ čĆąŠą╗čī čéą░ą║č鹊ą▓ąŠą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. ąĪąĖą│ąĮą░ą╗ ąŠčé ą╝ąŠą┤čāą╗čÅč鹊čĆą░ ą┐ąŠčüčéčāą┐ą░ąĄčé ąĮą░ ąĀąÉ1, ą░ ą▓ ąŠą▒čĆą░čéąĮčāčÄ čüą▓čÅąĘčī ąĘą░ą▓ąŠą┤ąĖčéčüčÅ čü ąĀąÉ0. ąźąŠčćčā čüą║ą░ąĘą░čéčī, čćč鹊 ąĮąĄčüą┐čĆąŠčüčéą░! ąÜą░ą║ čāąČąĄ ą│ąŠą▓ąŠčĆąĖą╗ąŠčüčī, ą┐ąŠčĆčé ąÉ čā 2313 čéčĆčæčģą▒ąĖčéąĮčŗą╣, ą▓ą╝ąĄčüč鹊 čüčéą░čĆčłąĄą│ąŠ ą▒ąĖčéą░ čäčāąĮą║čåąĖąŠąĮąĖčĆčāąĄčé čüą▒čĆąŠčü. ąóą░ą║ čćč鹊, ą▓ąŠ-ą┐ąĄčĆą▓čŗčģ, ąĮąĄ ąĮą░ą┤ąŠ ą▒ąŠčÅčéčīčüčÅ ą▓čŗčüčéą░ą▓ąĖčéčī čćč鹊-ąĮąĖą▒čāą┤čī ąĮąĄ č鹊, ą░ ą▓ąŠ-ą▓č鹊čĆčŗčģ, ą┤ąŠčüčéą░č鹊čćąĮąŠ ą┐ąŠčéčĆą░čéąĖčéčī ąŠą┤ąĖąĮ čéą░ą║čé ąĖ čüą┤ą▓ąĖąĮčāčéčī čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ tmp ąĮą░ ąŠą┤ąĖąĮ čĆą░ąĘčĆčÅą┤ ą▓ą┐čĆą░ą▓ąŠ ąĖ ą┐ąĄčĆąĄą┤ą░čéčī ąĮą░ ą▓čŗčģąŠą┤ (2-ą╣ ąĖ 3-ą╣ čéą░ą║čéčŗ): LSR tmp┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;čüą┤ą▓ąĖą│ą░ąĄą╝ ą▓ą┐čĆą░ą▓ąŠ ąĮą░ ąŠą┤ąĖąĮ čĆą░ąĘčĆčÅą┤ OUT PORTA, tmp┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ą┐ąĄčĆąĄą┤ą░čæą╝ ąĘąĮą░č湥ąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤. ąÆąŠčé ąĘą┤ąĄčüčī ą╝ąŠąČąĮąŠ čü菹║ąŠąĮąŠą╝ąĖčéčī ąŠą┤ąĖąĮ čéą░ą║čé, ąĄčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ąĘąĮą░č湥ąĮąĖąĄ ą▓ ą┤čĆčāą│ąŠą╣ ą┐ąŠčĆčé (čü ą┤čĆčāą│ąĖą╝ ą▒čāą║ą▓ąĄąĮąĮčŗą╝ ąĖąĮą┤ąĄą║čüąŠą╝, ąĮąŠ čü č鹥ą╝ ąČąĄ ąĮąŠą╝ąĄčĆąŠą╝!), č鹊ą│ą┤ą░ ąĮąĄ ą┐ąŠčéčĆąĄą▒čāąĄčéčüčÅ čüą┤ą▓ąĖą│ą░. ą×ą┤ąĮą░ą║ąŠ čéčĆąŠą│ą░čéčī ą┤čĆčāą│ąĖąĄ ą┐ąŠčĆčéčŗ ą╝ąĮąĄ ąĮąĄ čģąŠč鹥ą╗ąŠčüčī, ą┐ąŠčŹč鹊ą╝čā ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░ąĮ č鹊ą╗čīą║ąŠ ą┐ąŠčĆčé ąÉ. 3. ą¤čĆąĖą▒ą░ą▓ąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą▒ąĖčéą░ ą║ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆčā. ąĢčēčæ ąŠą┤ąĮą░ ą┐čĆąĄą╗ąĄčüčéčī ą┐ąŠčĆčéą░ ąÉ čā ąóąĖąĮčīą║ąĖ ą▓ č鹊ą╝, čćč鹊 čüčéą░čĆčłąĖąĄ ąĮąĄąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▒ąĖčéčŗ čćąĖčéą░čÄčéčüčÅ ą║ą░ą║ ąĮčāą╗ąĖ. ą¤ąŠčŹč鹊ą╝čā ąĮąĄ ąĮą░ą┤ąŠ ąĮą░ą║ą╗ą░ą┤čŗą▓ą░čéčī ą╝ą░čüą║čā ąĮą░ tmp (ąĖą╝ąĄčÅ ą▓ ą▓ąĖą┤čā čćč鹊-č鹊 ą▓čĆąŠą┤ąĄ ANDI tmp, 0b00000001) čćč鹊ą▒čŗ ąĮąĄ ą┐čĆąŠą╗ąĄąĘą╗ąĖ ą╗ąĖčłąĮąĖąĄ ąĄą┤ąĖąĮąĖčåčŗ! ąÉ čŹč鹊 菹║ąŠąĮąŠą╝ąĖčÅ čéą░ą║čéą░ ą£ąÜ. ą¤ą╗čÄčü ą║ąŠ ą▓čüąĄą╝čā, ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą▒ąĖčéą░ čā ąĮą░čü čģčĆą░ąĮąĖčéčüčÅ ą▓ ą╝ą╗ą░ą┤čłąĄą╝ čĆą░ąĘčĆčÅą┤ąĄ čĆąĄą│ąĖčüčéčĆą░. ąØą░ą╝ ąĮąĄ ą┐čĆąĖą┤čæčéčüčÅ čéčĆą░čéąĖčéčī čéą░ą║čéčŗ ąĖ čüą┤ą▓ąĖą│ą░čéčī ąĄą│ąŠ! ąś čŹč鹊 ąĘąĮą░čćąĖčé, čćč鹊 ą╝čŗ ą╝ąŠąČąĄą╝ ą┐čĆąŠčüč鹊 čüą╗ąŠąČąĖčéčī ąĘąĮą░č湥ąĮąĖčÅ ą┤ą▓čāčģ čĆąĄą│ąĖčüčéčĆąŠą▓: tmp ąĖ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░. ąźąŠčéčÅ ąĮą░ čüą░ą╝ąŠą╝ ą┤ąĄą╗ąĄ ą▓čüčæ ąĮąĄ čéą░ą║ ą┐čĆąŠčüč鹊: ą┐čĆąĖą┤čæčéčüčÅ čüčāą╝ą╝ąĖčĆąŠą▓ą░čéčī ą┤ą▓čāčģą▒ą░ą╣čéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čü ąŠą┤ąĮąŠą▒ą░ą╣čéąĮčŗą╝. ąĪą┤ąĄą╗ą░ąĄą╝ čŹč鹊 ą▓ ą┤ą▓ą░ ąĘą░čģąŠą┤ą░: čüąĮą░čćą░ą╗ą░ čüą╗ąŠąČąĖą╝ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé čĆąĄąĘčāą╗čīčéą░čéą░ čü čĆąĄą│ąĖčüčéčĆąŠą╝ tmp (ą▓ ą║ąŠč鹊čĆąŠą╝ čģčĆą░ąĮąĖčéčüčÅ ą┐čĆąĖčłąĄą┤čłąĖą╣ ą▒ąĖčé ąŠčé ą┤ąĄą╗čīčéą░-čüąĖą│ą╝ą░ ą╝ąŠą┤čāą╗čÅč鹊čĆą░), ą░ ą┐ąŠč鹊ą╝ čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé čü čäą╗ą░ą│ąŠą╝ ą┐ąĄčĆąĄąĮąŠčüą░ ąĪ, ąĄčüą╗ąĖ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ. ąÆ čüą┐ąĖčüą║ąĄ ą║ąŠą╝ą░ąĮą┤ ąóąĖąĮčīą║ąĖ čÅ ąĮąĄ ąĮą░čłčæą╗ ą║ąŠą╝ą░ąĮą┤čā čüą╗ąŠąČąĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ čü čäą╗ą░ą│ąŠą╝ ą┐ąĄčĆąĄąĮąŠčüą░, č鹊ą╗čīą║ąŠ čüą╗ąŠąČąĄąĮąĖąĄ ą┤ą▓čāčģ čĆąĄą│ąĖčüčéčĆąŠą▓ čü čāčćčæč鹊ą╝ čäą╗ą░ą│ą░ ą┐ąĄčĆąĄąĮąŠčüą░. ąóčāčé-č鹊 ąĖ ą┐ąŠčéčĆąĄą▒čāąĄčéčüčÅ ┬½ąĮčāą╗ąĄą▓ąŠą╣┬╗ čĆąĄą│ąĖčüčéčĆ: čüą╗ąŠąČąĖą╝ ąĄą│ąŠ čü čāčćčæč鹊ą╝ ą┐ąĄčĆąĄąĮąŠčüą░ čüąŠ čüčéą░čĆčłąĖą╝ ą▒ą░ą╣č鹊ą╝ čĆąĄąĘčāą╗čīčéą░čéą░. ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ąĮąĄ ą▒čŗą╗ąŠ (ąĪ = 0), č鹊 ąĘąĮą░č湥ąĮąĖąĄ countH ąĮąĄ ąĖąĘą╝ąĄąĮąĖčéčüčÅ. ąÆ ą┐čĆąŠčéąĖą▓ąĮąŠą╝ čüą╗čāčćą░ąĄ čāą▓ąĄą╗ąĖčćąĖčéčüčÅ ąĮą░ ąĄą┤ąĖąĮąĖčåčā (4-ą╣ ąĖ 5-ą╣ čéą░ą║čéčŗ). //ANDI tmp, 0b00000001┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ą▓ ąŠą▒čēąĄą╝ čüą╗čāčćą░ąĄ ąŠą▒ąĮčāą╗ąĄąĮąĖąĄ ą╗ąĖčłąĮąĖčģ ąĄą┤ąĖąĮąĖčå ADD resultL, tmp┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ą┐čĆąĖą▒ą░ą▓ą╗čÅąĄą╝ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą▒ąĖčéą░ ą║ ą╝ą╗ą░ą┤čłąĄą╝čā ą▒ą░ą╣čéčā ADC resultH, zeroreg┬Ā ┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ą┐čĆąĖą▒ą░ą▓ą╗čÅąĄą╝ čäą╗ą░ą│ ą┐ąĄčĆąĄąĮąŠčüą░ (ąĄčüą╗ąĖ ąĄčüčéčī) ą║ čüčéą░čĆčłąĄą╝čā ą▒ą░ą╣čéčā ąĢčüą╗ąĖ ą┤ą╗čÅ ą▓ą▓ąŠą┤ą░-ą▓čŗą▓ąŠą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čéčĆąĄčéąĖą╣-č湥čéą▓čæčĆčéčŗą╣-ą┐čÅčéčŗą╣ ą▓čŗą▓ąŠą┤ ą┐ąŠčĆčéą░, č鹊 ą┤ą╗čÅ čŹą║ąŠąĮąŠą╝ąĖąĖ ą▓čĆąĄą╝ąĄąĮąĖ ą▓čŗčćąĖčüą╗ąĄąĮąĖą╣ č鹥ąŠčĆąĄčéąĖč湥čüą║ąĖ ąĄčüčéčī čüą╝čŗčüą╗ ąĮąĄ čüą┤ą▓ąĖą│ą░čéčī ą┐čĆąĖąĮčÅčéčŗą╣ ą▒ąĖčé ą▓ ą╝ą╗ą░ą┤čłąĖą╣ čĆą░ąĘčĆčÅą┤, ą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ čĆąĄąĘčāą╗čīčéą░čéą░ čéčĆąĖ ą▒ą░ą╣čéą░ (čĆąĄą│ąĖčüčéčĆčŗ: resultL, resultM, resultH). ąó.ąĄ. ą┐ąŠ-ą┐čĆąĄąČąĮąĄą╝čā čüą╗ąŠąČąĖčéčī ą┐čĆąĖąĮčÅčéčŗą╣ ą▒ąĖčé čü ą╝ą╗ą░ą┤čłąĖą╝ ą▒ą░ą╣č鹊ą╝ čĆąĄąĘčāą╗čīčéą░čéą░ (ADD resultL, tmp), ąĮąŠ ą┐ąŠč鹊ą╝ ą┤ą▓ą░ čĆą░ąĘą░ čüą╗ąŠąČąĖčéčī čü čāčćčæč鹊ą╝ čäą╗ą░ą│ą░ ą┐ąĄčĆąĄąĮąŠčüą░ čüčĆąĄą┤ąĮąĖą╣ ąĖ čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čéčŗ (ADC resultM, zeroreg; ADC resultH, zeroreg) c ┬½ąĮčāą╗ąĄą▓čŗą╝┬╗ čĆąĄą│ąĖčüčéčĆąŠą╝. ąÉ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąŠčüč鹊 čüą┤ą▓ąĖąĮčāčéčī ąĘąĮą░čćą░čēąĖąĄ 16 ą▒ąĖčé ą▓ ą║ą░ą║ąĖąĄ-ą╗ąĖą▒ąŠ ą┤ą▓ą░ čĆąĄą│ąĖčüčéčĆą░. 4. ąśąĮą║čĆąĄą╝ąĄąĮčé/ą┤ąĄą║čĆąĄą╝ąĄąĮčé čüčćčæčéčćąĖą║ą░. ąóčāčé č鹊ąČąĄ ąĮąĖč湥ą│ąŠ ąŠčüąŠą▒ąĄąĮąĮąŠą│ąŠ. ąØą░ čŹč鹊čé čĆą░ąĘ ąĄčüčéčī ą║ąŠą╝ą░ąĮą┤čŗ čüą╗ąŠąČąĄąĮąĖčÅ/ą▓čŗčćąĖčéą░ąĮąĖčÅ čüą╗ąŠą▓ą░ (ą┤ą▓čāčģą▒ą░ą╣čéąĮąŠą│ąŠ čćąĖčüą╗ą░) čü ą║ąŠąĮčüčéą░ąĮč鹊ą╣. ą×ą┤ąĮą░ą║ąŠ, ą┐čĆąĖ ąČąĄą╗ą░ąĮąĖąĖ čāą▓ąĄą╗ąĖčćąĖčéčī čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī, ąĮą░ą┤ąŠ ą▒čāą┤ąĄčé ą┐ąŠą┤čāą╝ą░čéčī (6-ą╣ ąĖ 7-ą╣ čéą░ą║čéčŗ). SBIW countL, 1┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ą┤ąĄą║čĆąĄą╝ąĄąĮčé ą┤ą▓čāčģą▒ą░ą╣čéąĮąŠą│ąŠ čüčćčæčéčćąĖą║ą░ 5. ą¤čĆąŠą▓ąĄčĆą║ą░ čāčüą╗ąŠą▓ąĖčÅ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ą¤ąŠčüą║ąŠą╗čīą║čā čüčćčæčéčćąĖą║ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĮčŗą╣, č鹊 ąĄčüą╗ąĖ ąĄą│ąŠ ąĘąĮą░č湥ąĮąĖąĄ ąĮąĄ čĆą░ą▓ąĮąŠ ąĮčāą╗čÄ, č鹊 ą┐ąĄčĆąĄčģąŠą┤ąĖą╝ ą║ ą┐.1, čé.ąĄ. ą║ ą╝ąĄčéą║ąĄ ADC_count (8-ą╣ ąĖ 9-ą╣ čéą░ą║čéčŗ). BRNE ADC_count┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ą┐ąĄčĆąĄčģąŠą┤ ąĮą░ ą╝ąĄčéą║čā ADC_count, ąĄčüą╗ąĖ ąĮąĄ ąĮąŠą╗čī 6. ąśčéą░ą║, ą▓ resultH ąĖ resultL ą┐ąŠą╗čāčćąĖą╗ąĖ čĆąĄąĘčāą╗čīčéą░čé. ąÆčüčæ, ą┤ą░ą╗ąĄąĄ ą╝ąŠąČąĄą╝ ą┤ąĄą╗ą░čéčī čü ąĮąĖą╝ ą▓čüčæ, čćč鹊 čģąŠčéąĖą╝. ąÆ čüą░ą╝ąŠą╝ ąĮą░čćą░ą╗ąĄ, ą┐ąŠčüą╗ąĄ ą╝ąĄčéą║ąĖ ADC_start, ą╝čŗ ą┐ąŠčüčéą░ą▓ąĖą╗ąĖ ┬½ąĮąŠą┐čćąĖą║┬╗. ąØą░ ą╝ąĄčüč鹊 čŹč鹊ą│ąŠ NOPŌĆÖa ą╝ąŠąČąĮąŠ ą┐ąŠčüčéą░ą▓ąĖčéčī čćč鹊-ąĮąĖą▒čāą┤čī ą┐ąŠą╗ąĄąĘąĮąŠąĄ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ ąĘą░ą┐čĆąĄčéąĖčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ ąŠąĮąĖ čĆą░ąĘčĆąĄčłąĄąĮčŗ (CLI). ą¤ąŠč鹊ą╝čā čćč鹊 ą╗čÄą▒ąŠą╣ ąĮąĄąĘą░ą┐ą╗ą░ąĮąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą▓čŗčģąŠą┤ ąĖąĘ čåąĖą║ą╗ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čüą▓ąĄą┤čæčé ą▓čüčÄ č鹊čćąĮąŠčüčéčī ąĮą░ ąĮąĄčé. ą£ąŠąČąĄčé ą▒čŗčéčī, ą║ąŠą╝čā-ąĮąĖą▒čāą┤čī ąĘą░čģąŠč湥čéčüčÅ ą┐ąŠą┤ąČąĄčćčī čüą▓ąĄč鹊ą┤ąĖąŠą┤ąĖą║ ąĮą░ ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĖą╗ąĖ ąĄčēčæ čćč鹊. ąØčā ąĖ ą║ąŠąĄ-čćč鹊 ąĄčēčæŌĆ” ą¤ąŠčüą║ąŠą╗čīą║čā čĆąŠą╗čī čéą░ą║čéąĖčĆčāąĄą╝ąŠą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ čā ąĮą░čü ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą£ąÜ č鹊ą╗čīą║ąŠ ą▓ čåąĖą║ą╗ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ą▓ąĮąĄ čŹč鹊ą│ąŠ čåąĖą║ą╗ą░ ą▓ąĮąĄčłąĮčÅčÅ čüčģąĄą╝ą░ (čĆąĖčü.5) ┬½ąĘą░ą╝ąĖčĆą░ąĄčé┬╗. ąŁč鹊 čĆą░ą▓ąĮąŠčüąĖą╗čīąĮąŠ č鹊ą╝čā, čćč鹊 ą╝čŗ čĆą░ąĘčĆčŗą▓ą░ąĄą╝ čåąĄą┐čī ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╣ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ (ą×ą×ąĪ), čćč鹊 ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ čāčģąŠą┤čā ąĖąĮč鹥ą│čĆą░č鹊čĆą░ (ą×ąĀ3 ąĮą░ čĆąĖčü.5) ą▓ ąĮą░čüčŗčēąĄąĮąĖąĄ ą┤ąŠ ┬▒Umax. ąĪą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąĄčĆą▓čŗčģ čéą░ą║č鹊ą▓ ą╝ąŠą┤čāą╗čÅč鹊čĆ ą▓čŗčģąŠą┤ąĖčé ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ ą▓ čĆą░ą▒ąŠčćčāčÄ ąŠą▒ą╗ą░čüčéčī, ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąĄčĆą▓čŗčģ ą▒ąĖčé ą╝ąŠą│čāčé ą▓ąĮąĄčüčéąĖ ąŠčłąĖą▒ą║čā ą▓ čĆąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąŚąĮą░čćąĖčé, ą┤ąŠ ą▓čģąŠą┤ą░ ą▓ čåąĖą║ą╗ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čģąŠčéčÅ ą▒čŗ ą┐ąŠą┐čŗčéą░čéčīčüčÅ ą▓čŗą▓ąĄčüčéąĖ ą╝ąŠą┤čāą╗čÅč鹊čĆ ą▓ čĆą░ą▒ąŠčćčāčÄ ąŠą▒ą╗ą░čüčéčī. ąĪą┤ąĄą╗ą░čéčī čŹč鹊 ą┐čĆąŠčēąĄ ą▓čüąĄą│ąŠ, ą┐čĆąŠąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ą▓ čüąĖą│ąĮą░ą╗, ąĖą┤čāčēąĖą╣ ąŠčé ą£ąÜ ą║ ąöąĪą£. ąśąĮčŗą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čüčćąĖčéą░čéčī ąĘąĮą░č湥ąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┐ąŠčĆčéą░, ą┐čĆąŠąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░čéčī ąĄą│ąŠ ąĖ čüąĮąŠą▓ą░ ąŠčéą┐čĆą░ą▓ąĖčéčī ąĮą░ ą▓čŗčģąŠą┤, ąĘą░č鹥ą╝ ą┐ąŠą┤ąŠąČą┤ą░čéčī, ąĖ č鹊ą╗čīą║ąŠ ą┐ąŠč鹊ą╝ ą▓čģąŠą┤ąĖčéčī ą▓ čåąĖą║ą╗ (ą╝ąĄčéą║ą░ ADC_count). ąĪą║ąŠą╗čīą║ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąČą┤ą░čéčī? ąŁč鹊 ąĘą░ą▓ąĖčüąĖčé ąŠčé ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ą×ą┤ąĮą░ą║ąŠ, ą┤ąŠ ąĮą░čćą░ą╗ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą╝čŗ ąŠ ąĮčæą╝ ąĮąĖč湥ą│ąŠ ąĮąĄ ąĘąĮą░ąĄą╝. ąĀą░čüčüą╝ąŠčéčĆąĖą╝ 菹║čüčéčĆąĄą╝ą░ą╗čīąĮčŗąĄ čüą╗čāčćą░ąĖ. ąÆ ą┐ąĄčĆą▓ąŠą╝ čüą╗čāčćą░ąĄ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą╝čŗ ą┤čæčĆąĮąĄą╝ ąĮąŠą│ąŠą╣ ą£ąÜ, ąĮą░ ą▓čģąŠą┤ąĄ ąĖąĮč鹥ą│čĆą░č鹊čĆą░ ą▒čāą┤ąĄčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠąĄ (ą┐ąŠ ą╝ąŠą┤čāą╗čÄ) ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, ą▓ąŠ ą▓č鹊čĆąŠą╝ ŌĆö ą▓ą┤ą▓ąŠąĄ ą╝ąĄąĮčīčłąĄ, ą▓ čéčĆąĄčéčīąĄą╝ ŌĆö ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠąĄ. ąØą░ čĆąĖčüčāąĮą║ąĄ 12 ą┐ąŠą║ą░ąĘą░ąĮą░ ąŠčüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ąĖąĮč鹥ą│čĆą░č鹊čĆą░ (ą▓ ą┐čĆąĄą┤ą┐ąŠą╗ąŠąČąĄąĮąĖąĖ, čćč鹊 ąŠąĮ ąĮą░čüčŗčéąĖą╗čüčÅ ą┤ąŠ -Umax) ą┤ą╗čÅ čŹčéąĖčģ čüą╗čāčćą░ąĄą▓.

ąĀąĖčü.12. ąÜ ą▓čŗą▒ąŠčĆčā ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┤ąĄčƹȹ║ąĖ ą¤ąŠ ą▓ąĄčĆčéąĖą║ą░ą╗ąĖ čłą║ą░ą╗ą░ ąĮąŠčĆą╝ąĖčĆąŠą▓ą░ąĮą░ ąĮą░ Umax, ą┐ąŠ ą│ąŠčĆąĖąĘąŠąĮčéą░ą╗ąĖ ŌĆö ąĮą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ąŠą┤ąĮąŠą│ąŠ čéą░ą║čéą░ ąöąĪą£. ą¤ąŠčüč鹊čÅąĮąĮą░čÅ ą▓čĆąĄą╝ąĄąĮąĖ ąĖąĮč鹥ą│čĆą░č鹊čĆą░ ą▓čŗą▒čĆą░ąĮą░ čéą░ą║ąŠą╣, čćč鹊ą▒čŗ ąĘą░ ąŠą┤ąĖąĮ čéą░ą║čé ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░čĆą░čüčéą░ą╗ąŠ ąĮąĄ ą▒ąŠą╗ąĄąĄ, č湥ą╝ ąĮą░ 90% ąŠčé Umax. ąśąĘ čĆąĖčüčāąĮą║ą░ ą▓ąĖą┤ąĮąŠ, čćč鹊 ąĄčüą╗ąĖ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ąĘą░ą┤ąĄčƹȹ║ąĖ ą▒čāą┤ąĄčé čćčāčéčī ą▒ąŠą╗čīčłąĄ (ą▓ ą┤ą░ąĮąĮąŠą╝ čüą╗čāčćą░ąĄ ąĮą░ 10%) ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą┤ą▓čāčģ čéą░ą║č鹊ą▓ ą╝ąŠą┤čāą╗čÅč鹊čĆą░, č鹊 ąĮą░ ą╝ąŠą╝ąĄąĮčé ą▓čģąŠą┤ą░ ą▓ čåąĖą║ą╗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ ąĖąĮč鹥ą│čĆą░č鹊čĆą░ ą▒čāą┤ąĄčé ą╗ąĄąČą░čéčī ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ąŠčé -Umax ą┤ąŠ +Umax. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐ąŠą▓čŗčüąĖčéčüčÅ č鹊čćąĮąŠčüčéčī ąĖąĘą╝ąĄčĆąĄąĮąĖą╣ ą▓ čĆą░ą╣ąŠąĮąĄ UąŠą┐/2. ąśčéą░ą║, ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓ ąĘą░ą┤ąĄčƹȹ║ąĖ ą£ąÜ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čéą░ą║ąŠąĄ ąČąĄ, ą║ą░ą║ ą▓ ą┤ą▓čāčģ čéą░ą║čéą░čģ ą╝ąŠą┤čāą╗čÅč鹊čĆą░ ą┐ą╗čÄčü 5ŌĆ”15 ą┐čĆąŠčåąĄąĮč鹊ą▓ (ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┐ąŠčüč鹊čÅąĮąĮąŠą╣ ą▓čĆąĄą╝ąĄąĮąĖ ąĖąĮč鹥ą│čĆą░č鹊čĆą░). ąÜąŠą┤: LDI tmp, 0b00000001┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;čé.ą║. ą╝ą╗ą░ą┤čłąĖą╣ čĆą░ąĘčĆčÅą┤ ą┐ąŠčĆčéą░ ąÉ ąĮą░čüčéčĆąŠąĄąĮ ąĮą░ ą▓čŗčģąŠą┤, OUT PINA, tmp┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ą┤čæčĆą│ą░ąĄą╝ ąĮąŠą│ąŠą╣ ąĘą░ą┐ąĖčüčīčÄ ┬½1┬╗ ą▓ čĆąĄą│ąĖčüčéčĆ PIN NOP┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ąĘą░ą┤ąĄčƹȹ║ąĖ ą┐ąŠ ą▓ą║čāčüčā, ą╝ąŠąČąĮąŠ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░čéčī čåąĖą║ą╗, ŌĆ”┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ą╝ąŠąČąĮąŠ ą┤ąĄą╗ą░čéčī čćč鹊-ąĮąĖą▒čāą┤čī ą┐ąŠą╗ąĄąĘąĮąŠąĄ: ąĮą░ą┐čĆąĖą╝ąĄčĆ, NOP┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā┬Ā ;ąŠą▒ąĮčāą╗čÅčéčī/čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčī čĆąĄą│ąĖčüčéčĆčŗ, ąĘą░ą┐čĆąĄčēą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąźąŠčéčÅ ąĄčüą╗ąĖ ąĮą░ čćč鹊-č鹊 ą▓ą░ąČąĮąŠąĄ ąĮąĄ ą▒čāą┤ąĄčé čģą▓ą░čéą░čéčī ą┐ą░ą╝čÅčéąĖ ąĮą░ ą┐ą░čĆčā ą║ąŠą╝ą░ąĮą┤, čŹč鹊 ą╝ąŠąČąĮąŠ ą▓čŗą║ąĖąĮčāčéčī. ąÆ ąČąĄą╗ąĄąĘąĄ ą▓čüčæ čŹč鹊 ą┐čĆąŠą▓ąĄčĆčÅą╗ąŠčüčī ąĮą░ ą╝ą░ą║ąĄčéąĮąŠą╣ ą┐ą╗ą░č鹥. ą×čüąĮąŠą▓ąĮą░čÅ čćą░čüčéčī čüčģąĄą╝čŗ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü.13.

ąĀąĖčü.13. ą×čüąĮąŠą▓ąĮą░čÅ čćą░čüčéčī čüčģąĄą╝čŗ ą╝ą░ą║ąĄčéąĮąŠą╣ ą┐ą╗ą░čéčŗ ą┤ą╗čÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ ą×ą┐ąĄčĆą░čåąĖąŠąĮąĮąĖą║ ŌĆö TL084CN (ą▓čģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ 10^12 ą×ą╝, čé.ąĄ. ą╝ąĖą╗ą╗ąĖąŠąĮ ą╝ąĄą│ą░ąŠą╝!!! [7]). ąĀ1 ŌĆö ą╝ąĮąŠą│ąŠąŠą▒ąŠčĆąŠčéąĮčŗą╣, čéąĖą┐ą░ 3106. ą¤ąĖčéą░ąĮąĖąĄ (┬▒5 ąÆ) ŌĆö ąŠčé ą┤ą▓čāčģ č鹥ą╗ąĄč乊ąĮąĮčŗčģ ąĘą░čĆčÅą┤ąŠą║, ąĮąĄ ąŠč湥ąĮčī čüčéą░ą▒ąĖą╗ąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗčģ. ą£ąÜ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ čćą░čüč鹊č鹥 500 ą║ąōčå ąŠčé ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░. ąĀąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▓čŗą▓ąŠą┤ąĖčéčüčÅ ąĮą░ ąČąĖą┤ą║ąŠą║čĆąĖčüčéą░ą╗ą╗ąĖč湥čüą║ąĖą╣ ąĖąĮą┤ąĖą║ą░č鹊čĆ (ą¢ąÜąś) 0802 ą┐čĆčÅą╝ąŠ ą▓ čģąĄą║čüąĄ. ąĪ čéą░ą║ąŠą╣ ą┐čĆąŠčłąĖą▓ą║ąŠą╣ ąĖ čüčģąĄą╝ąŠą╣ čāą┤ą░ą╗ąŠčüčī ą┤ąŠą▒ąĖčéčīčüčÅ čŹčäč乥ą║čéąĖą▓ąĮąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą▒ąŠą╗ąĄąĄ 15 ą▒ąĖčé ŌĆö ą╝ą╗ą░ą┤čłąĖą╣ čĆą░ąĘčĆčÅą┤ ąĖąĮąŠą│ą┤ą░ ┬½ą┤čæčĆą│ą░ąĄčéčüčÅ┬╗. ąĪč鹊ą╗čī ąĮąĖąĘą║ą░čÅ čćą░čüč鹊čéą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą£ąÜ čüą▓čÅąĘą░ąĮą░ čü čāą┤ąŠą▒čüčéą▓ąŠą╝ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ąĖąĮč乊čĆą╝ą░čåąĖąĖ (ą┤ą░ąĮąĮčŗąĄ ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ ą┐čĆąĖą╝ąĄčĆąĮąŠ čĆą░ąĘ ą▓ čüąĄą║čāąĮą┤čā ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ) ąĖ ąĮąĄ čüą░ą╝ąŠą╣ ą▓čŗčüąŠą║ąŠą╣ čüą║ąŠčĆąŠčüčéčīčÄ ąĮą░čĆą░čüčéą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĮąŠą│ąŠ ą×ąŻ (13 ąÆ/ą╝ą║čü). ąĪą░ą╝čŗąĄ ą▓čŗčüąŠą║ąĖąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą┐ąŠ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖčÄ ą┐čĆąĄą┤čŖčÅą▓ą╗čÅčÄčéčüčÅ ą║ čüčāą╝ą╝ą░č鹊čĆčā/ą▓čŗčćąĖčéą░č鹥ą╗čÄ (ą×ąĀ2 ąĮą░ čĆąĖčü.5 ąĖ 13): ą▓čĆąĄą╝čÅ ąĄą│ąŠ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą╝ąĮąŠą│ąŠ ą╝ąĄąĮčīčłąĄ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąŠą┤ąĮąŠą│ąŠ čéą░ą║čéą░ ą╝ąŠą┤čāą╗čÅč鹊čĆą░. ąØą░ą┐ąŠčüą╗ąĄą┤ąŠą║ ąĄčēčæ ąŠą┤ąĮą░ čäąĖčłą║ą░. ąöąŠą┐čāčüčéąĖą╝, ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ (ą║ąŠč鹊čĆąŠąĄ ą▓čŗą┤ą░čæčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ, ą▓ ą┤ą░ąĮąĮąŠą╣ čüčģąĄą╝ąĄ) čā ąĮą░čü 4,789 ąÆ. ąóąŠą│ą┤ą░ ąĄčüą╗ąĖ ą╝čŗ ą▓ čüčćčæčéčćąĖą║ ą▓ą╝ąĄčüč鹊 $FFFF (2^16 - 1) ą┐čĆąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ąĘą░ą┐ąĖčłąĄą╝ $BB12 (47890), č鹊 čĆąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čā ąĮą░čü ą▒čāą┤ąĄčé čüčĆą░ąĘčā ą▓ ą┤ąĄčüčÅčéčŗčģ ą┤ąŠą╗čÅčģ ą╝ąĖą╗ą╗ąĖą▓ąŠą╗čīčéą░!!! ą×č湥ąĮčī čāą┤ąŠą▒ąĮąŠ, ą║ą░ą║ ą╝ąĮąĄ ą║ą░ąČąĄčéčüčÅ. ąÜąŠąĮąĄčćąĮąŠ, ąĮąĄą╝ąĮąŠą│ąŠ ą┐ąŠčüčéčĆą░ą┤ą░ąĄčé č鹊čćąĮąŠčüčéčīŌĆ” ąĮąŠ ąĄčüą╗ąĖ čüąĖą╗čīąĮąŠ ąĮąĄ ąĘą╗ąŠčāą┐ąŠčéčĆąĄą▒ą╗čÅčéčī (čģąŠčéčÅ ą▒čŗ ąĮąĄ ąŠą┐čāčüą║ą░čéčīčüčÅ ąĮąĖąČąĄ 2^15), č鹊 ąĮąĖč湥ą│ąŠ čüčéčĆą░čłąĮąŠą│ąŠ. ąĪ ą┤čĆčāą│ąŠą╣ čüč鹊čĆąŠąĮčŗ, ąĄčüą╗ąĖ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ čüą┤ąĄą╗ą░čéčī ą▓čĆąĄą╝čÅ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ ą║čĆą░čéąĮčŗą╝ 20 ą╝čü, č鹊 ąĘą░ čüčćčæčé čāčüčĆąĄą┤ąĮąĄąĮąĖčÅ ą┤ąŠą╗ąČąĮąŠ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčīčüčÅ ą▓ą╗ąĖčÅąĮąĖąĄ 菹╗ąĄą║čéčĆąŠčüąĄčéąĖ (50 ąōčå) ąĮą░ čĆąĄąĘčāą╗čīčéą░čé ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ. ąśčéą░ą║, ą┐ąŠą┤ą▓ąĄą┤čæą╝ ąĖč鹊ą│ąĖ. ┬Ā ąöąŠčüč鹊ąĖąĮčüčéą▓ą░: 1) ą┐čĆąŠčüč鹊čéą░ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╣ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╣ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ; 2) ą▓čŗčüąŠą║ą░čÅ čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī (ąĘą░ą▓ąĖčüąĖčé ąŠčé ą▓čĆąĄą╝ąĄąĮąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ); 3) ą┤ąĄčłąĄą▓ąĖąĘąĮą░; 4) ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ą║ąŠą┤ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ čćąĖčüą╗ą░ (ą▓ čé.čć. ąĮąĄ čĆą░ą▓ąĮąŠą│ąŠ 2^N-1); 5) č鹊ą╗ąĄčĆą░ąĮčéąĮąŠčüčéčī ą║ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╝čā ą▓čģąŠą┤ąĮąŠą╝čā ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ. ┬Ā ąØąĄą┤ąŠčüčéą░čéą║ąĖ: 1) ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéčī ą┤ą▓čāą┐ąŠą╗čÅčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ; 2) ą╝ąĄą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī (ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąŠą┐ąŠčĆčåąĖąŠąĮą░ą╗čīąĮąŠ čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ). ┬Ā ą¤ąĄčĆčüą┐ąĄą║čéąĖą▓čŗ ąĖ ą┐čāčéąĖ ą┤ą░ą╗čīąĮąĄą╣čłąĄą│ąŠ čĆą░ąĘą▓ąĖčéąĖčÅ. ąæčŗą╗ąŠ ą▒čŗ ąĖąĮč鹥čĆąĄčüąĮąŠ ą┐ąŠąĖą│čĆą░čéčīčüčÅ čü ąŠą┐ąŠčĆąĮčŗą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝: čüą┤ąĄą╗ą░čéčī ąĄą│ąŠ ą▒ąŠą╗ąĄąĄ čüčéą░ą▒ąĖą╗čīąĮčŗą╝ ąĖ/ąĖą╗ąĖ ą┤ą▓čāą┐ąŠą╗čÅčĆąĮčŗą╝ (č鹊ą│ą┤ą░ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą▒čŗ ąŠčåąĖčäčĆąŠą▓čŗą▓ą░čéčī ąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ). ąÜąŠąĮąĄčćąĮąŠ ąČąĄ, čĆą░čüą║ąŠč湥ą│ą░čĆąĖčéčī ą£ąÜ ą┤ąŠ ąŠą▒ąĄčēą░ąĮąĮčŗčģ 20 ą£ąōčå (čü ą┤čĆčāą│ąĖą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą╝ąŠąČąĮąŠ ąĖ ą▒ąŠą╗čīčłąĄ) ąĖ ą┐ąŠčüą╝ąŠčéčĆąĄčéčī, ą║ą░ą║ ą▓ąĄą┤čæčé čüąĄą▒čÅ ąÉą”ą¤. ą¤ą╗čÄčü ą║ąŠ ą▓čüąĄą╝čā, ą┐čĆąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠą╣ ąŠčåąĖčäčĆąŠą▓ą║ąĖ 2-čģ, 3-čģ ąĖą╗ąĖ 4-čģ čüąĖą│ąĮą░ą╗ąŠą▓, čŹč鹊 ą╝ąŠąČąĮąŠ ą┤ąĄą╗ą░čéčī ą▓ ąŠą┤ąĮąŠą╝ čåąĖą║ą╗ąĄ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čāą▓ąĄą╗ąĖčćąĖčéčüčÅ ąĮą░ 60, 120 ąĖ 170 ą┐čĆąŠčåąĄąĮč鹊ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą▓ą╝ąĄčüč鹊 100, 200 ąĖ 300 ą┐čĆąŠčåąĄąĮč鹊ą▓, ąĄčüą╗ąĖ ąŠčåąĖčäčĆąŠą▓čŗą▓ą░čéčī ą║ą░ąČą┤čŗą╣ čüąĖą│ąĮą░ą╗ ą┐ąŠ ąŠčéą┤ąĄą╗čīąĮąŠčüčéąĖ. ąśąĮč鹥čĆąĄčüąĮąŠ ą▒čŗą╗ąŠ ą▒čŗ čüą┤ąĄą╗ą░čéčī ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ ą┤ąĄčåąĖą╝ąĖčĆčāčÄčēąĖą╣ čäąĖą╗čīčéčĆ ąĮą░ ą¤ąøąśąĪ ąĖą╗ąĖ DSP. ąóąŠą│ą┤ą░ čāąČąĄ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą▒čŗ ą│ąŠą▓ąŠčĆąĖčéčī ąĖ ą┐čĆąŠ ąŠčåąĖčäčĆąŠą▓ą║čā ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ┬Ā ┬Ā ąĪčüčŗą╗ą║ąĖ/ą╗ąĖč鹥čĆą░čéčāčĆą░: 1. ąÆąĪąü ą┐ąŠ ą┐čĆąŠčłąĖą▓ą║ąĄ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÄ AT90S2313/ATTiny2313 2. ąŻčéą║ąĖąĮ ą£.ąØ. ąöąĖą┐ą╗ąŠą╝ąĮą░čÅ čĆą░ą▒ąŠčéą░ ą╝ą░ą│ąĖčüčéčĆą░ "ąĀą░ąĘčĆą░ą▒ąŠčéą║ą░ ąĖ ąĖčüčüą╗ąĄą┤ąŠą▓ą░ąĮąĖąĄ ą┤ąĄčåąĖą╝ąĖčĆčāčÄčēąĄą│ąŠ čäąĖą╗čīčéčĆą░ čü ą╝ą░ą╗ąŠą╣ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄą╝ąŠą╣ ą╝ąŠčēąĮąŠčüčéčīčÄ ą┤ą╗čÅ ą░ąĮą░ą╗ąŠą│ąŠ-čåąĖčäčĆąŠą▓ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅ", ąĪą¤ą▒ąōą¤ąŻ, 2009 ą│., 89 čü. 3. ąĪąĖą│ą╝ą░-ą┤ąĄą╗čīčéą░ ąÉą”ą¤ 4. ą¤čĆąĖą╝ąĄąĮąĄąĮąĖąĄ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮčŗčģ čāčüąĖą╗ąĖč鹥ą╗ąĄą╣ 5. 1N4148; 1N4448 High-speed diodes 6. 8-bit Microcontroller with 2K Bytes In-System Programmable Flash 7. General Purpose J-FET Quad Operational Amplifiers ąÆčüąĄ ą▓ąŠą┐čĆąŠčüčŗ ą▓ ążąŠčĆčāą╝.

ąŁčéąĖ čüčéą░čéčīąĖ ą▓ą░ą╝ č鹊ąČąĄ ą╝ąŠą│čāčé ą┐čĆąĖą│ąŠą┤ąĖčéčīčüčÅ: |

|

|||||||||||||||

|

|

|

||||

|

|

||||